Активность

Лента обновляется автоматически

- Последний час

-

Xilinx ISE for Win 10 x64

3apw ответил druzhin тема в Среды разработки - обсуждаем САПРы

Я Вас не убеждаю верить во что-либо, просто описываю ситуацию, которую имел в виде факта в своей жизни. В качестве подтверждения есть работающий ПК на Windows10 с установленной Xilinx ISE 14.7 без каких-либо виртуальных машин. Относительно "блокировка со стороны Xilinx на активацию" сам наблюдал требования брандмауэра ПК разрешить открыть новые порты на домене Xilinx при установке пакета Xilinx ISE 14.7 и после разрешения которого все и заканчивалось. Поэтому предлагаю Вам пари на 1 000 000 (миллион) рублей - я демонстрирую Вам и Вашим секундантам работающую ПК на Windows10 с пакетом Xilinx ISE 14.7 и без виртуальных машин. В случае неработоспособности ПК с данным пакетом я плачу Вам 1 миллион рублей, в обратном случае такую же сумму Вы платите мне. Согласны? -

я все время использую для описания мультиплексора (VHDL) ptr_read_next <= ptr_read + 1 when rd_en_int = '1' else ptr_read; или под клоком в процессе с помощью if else

-

Стандартом VHDL функция conv_integer не определена, как и операция умножения для типа std_logic_vector

-

makc подписался на Проблемы поддержки VHDL/Verilog в PangoMicro PDS

-

Beby подписался на Проблемы поддержки VHDL/Verilog в PangoMicro PDS

-

Да я бы и не против (а может и всячески 'за'), но что-то не могу сообразить, о чём идёт речь. Поэтому, если хотите получить ответ (или результат проведённого мною эксперимента), то: - либо приведите (ссылку/текст) фрагмента стандарта, который мною приведённая запись нарушает; - либо сам вариант записи конструкции (cnMux_W - generic positive, Sel - std_logic_vector).

-

Xilinx ISE for Win 10 x64

Alex77 ответил druzhin тема в Среды разработки - обсуждаем САПРы

Фраза "По всей видимости при установке по интернету идет блокировка со стороны Xilinx на активацию. VPN также не помог." не добавляет правдивости к высказыванию "Xilinx ISE 14.7 у меня проработал несколько лет на обычной Win10" - Сегодня

-

qazse123 присоединился к сообществу

-

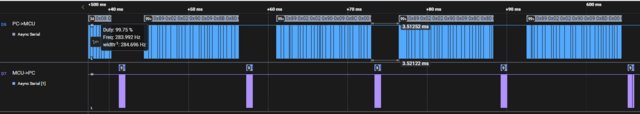

Да, именно это и произошло сейчас. Половина данных передается нормально, потом какая-то помеха прилетает и все помирает. Тут нужно видимо делать интеллектуальную функцию по поиску данных в этой каше.

-

HFSS и ЛПДА

uve ответил Alex_2015 тема в RF & Microwave Design

Я видел Вашу антенну на фото, ширина элементов разная. А эфф. диэл. проницаемость изменяется при разной ширине вибраторов. -

Нужна разработка на ПЛИС - разовый проект

speleoastronom опубликовал тема в Предлагаю работу

Привет. Нам нужен человек на проект на ПЛИС. Суть задачи - получать данные с КМОП матрицы (камеры), немного их обрабатывать, выдавать в двух различных режимах, принимать настройки для алгоритмов, передавать настройки матрице. Основные сложности проекта: 1) камера быстрая, 4000 кадров/сек, 2) связь с матрицей по 80 каналам ПЛИС, 3) придется принять участие в формулировке техзадания, втч. выбрать ПЛИС. Это не задача по обработке видеосигнала и тем более не обработка изображений. Алгоритмы простые. Москва, Московская область. Пишите на anickol(SOBAKKA)yahoo.com -

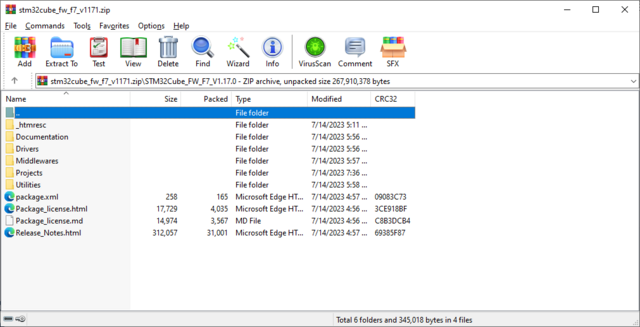

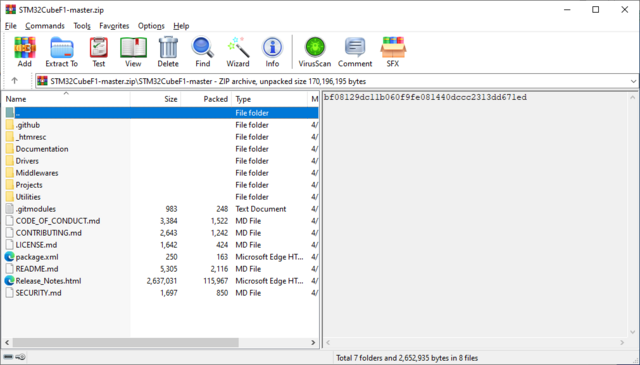

!!! Проглядел, искал с _fw_ Ещё раз спасибо.

-

Ага, помеха спомеховала и один из байтов в посылке потерялся. Поэтому никуда вы от таймаутов не уйдёте, потому что никогда не знаете, сколько отправилось байт в линию, и сколько дошло до вашего приёмника..

-

https://github.com/STMicroelectronics/STM32CubeF1/archive/refs/tags/v1.8.4.zip

-

Altera: an433.pdf

-

Спасибо за ссылку, но IDE требует stm32cube_fw_f1_v1.8.4, там этого нет, или не вижу.

-

Двигать клок относительно данных, или данные относительно клока - без разницы. При этом если двигать клок, то нужно двигать именно клок тактирующий выходные флопы, а не тот что наружу выходит. А если двигать дату, то нужно флопы размещать подальше от выхода, так что от идеи с размещение флопов в паде придется отказаться. При этом мне кажется что при правильных констрейнтах (плюс в сетапе и минус в холде, как я написал, и как в примере терасика) тул сам затянет клок для выходных флопов и постарается разместить их так, чтобы выходная задержка уложилась в констрейнт. И да, не нужно пытаться разместить флопы в паде, это может сильно помешать. А вот выходной клок лучше сделать дедикейтед пином чтобы было поменьше лэтенси.

-

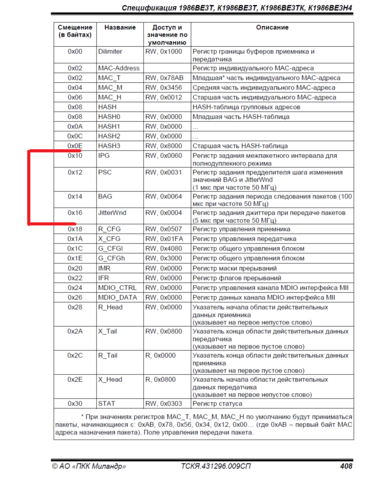

Какие-то внутренние настройки данного контроллера, скорее всего разработчик оставил данные поля для возможной точной настройки, и я не рекомендовал бы менять значения по умолчанию. В смысле? Записать в регистр что положено и потом проверить прочитав, то-ли там, что записано?

-

Вот что выяснил: Задержка при приеме из виртуального COM-порта возникает, если ReadFileEx не знает сколько байт нужно принять и ждет паузы между принятыми байтами. Например так : ReadFileEx(hSerial, DataBuf, sizeof(DataBuf), &OverLap, (LPOVERLAPPED_COMPLETION_ROUTINE)RxComplete); Примет он например 10 байт, паузы дождется(по факту плюс еще 35 мс) и вызовет RxComplete. Если же четко задать сколько байт надо принять (например 1 байт), то все происходит намного быстрее. Задержка между приемом и отправкой ~ 3 мс. ReadFileEx(hSerial, DataBuf, 1, &OverLap, (LPOVERLAPPED_COMPLETION_ROUTINE)RxComplete); Конечно теперь придется другой функции разбираться в этой каше, искать где начало данных, но в принципе задержка стала почти в 10 раз меньше.

-

Работа периодическая, не на полную занятось, те больше в режиме подработки. География - чтобы можно было иногда доехать в офис, но в целом дистанционная. Работаем в основном над своими идеями, заказного мало. Производим, в основном, диктофоны Edic-mini ( www.telesys.ru ). Идеологически они несложные (по сути микрофон, контроллер (STM32 сейчас) и память) и похожие, но мы выжимаем максимум из параметров (минимальный размер и тд) те оптимизация - это основное. Суть работы сводится к сборке проектов в кучу, их проверке, наведению лоска, отладке технологии сборки, доделке ничейных мелочей и тд. Как правило, схему, прошивку у нас делает один человек, плату разводит другой, корпусные детали делает третий. Все это нужно в кучу собрать чтобы получился диктофон, потестить, собрать обратку от продажников, истории ремонтов, дать рекомендации что надо изменить, где поправить (или сделать это самому, если есть навыки - получится быстрее), описать (или видео) технологию сборки и контроля для серийной сборки (сборку плат мы заказываем на стороне, а у себя делаем финальную сборку) и тд. Какие навыки полезны: тестер, осциллограф, паяльник, лазерный гравер/резак, 3D принтер. Ну и общее понимание техники. Все мелкое, поэтому хороошее зрение важно. Если можете делать какую-то работу на уровне разработчика/конструктора, то можем озадачить и ею. Оплата - ну, наверное, попроектно. Договоримся. Раньше у нас был человек для этой работы, но у нас случился большой перерыв во внедрении новых изделий, поэтому ищем нового. С предложениями пишите в личку, плиз.

-

Interactive BOM

Vovs ответил mobidev тема в Бесплатные САПР: KiCAD, EasyEDA, EAGLE и др.

Может быть кому нибудь будет интересно. Плагин для Альтиума, который генерирует Interactive BOM. https://boastools.com/ -

Xilinx ISE for Win 10 x64

kskssk ответил druzhin тема в Среды разработки - обсуждаем САПРы

Какая ж это магия, если и матлаб и моделсим преследуют.. -

Факт есть факт. На своём устройстве я ничего не трогаю, на ПК меняю ful/half. В обоих случаях на ПК есть приём. Если не трудно повторите тезисно, может действительно что-то пропустил. Да проверял уже... Ну оно, собственно, и логично. Если скорости совпадают, то почему должен отсутствовать приём. Это делалось исключительно ради эксперимента. У меня была задача проверить мой передатчик, передаёт ли он все кадры. В ответ с ПК я ничего не посылал. Я только подсчитывал кадры. То есть виндовозными средствами никак? У меня нет уверенности что установка режима в 1986BE3T отрабатывает правильно. К тому же есть подтверждение И если BE1 глючат то почему BE3 не могут? Вот я и хотел через ПК посмотреть какой режим стоит по факту. И ещё вопрос, кто-нибудь может объяснить мне смысл этих полей:

-

HFSS и ЛПДА

Alex_2015 ответил Alex_2015 тема в RF & Microwave Design

Первую версию считал и делал на ФАФ-4. Диэлектрическая проницаемость 2,7. Эффективная получалась 2,24. Соответственно, делил на корень 2,24. Сейчас считаю для понимания тот же ФАФ. Когда получу на нем приемлемые результаты, перейду на ФР4. Так дешевле в изготовлении. Хоть и потери немного возрастут. - Вчера

-

Рисунок LT527-Pin.pdf Эт вы его в PCAD?

-

Урезанный - это Cortex-M0 ;-), а это весьма "борзый" контроллер, в DSP умеющий лучше Cortex-M4 ;-) 1) Стереть начисто... 2) тут всё просто: TI значит Code Composer Studio, ну и его родные JTAG-и (Sauris XDS-510, XDS100) 3) ti.com, если пустят Документация лучше\подробнее\обильнее чем у T113s Ж8-Ь

-

похожая проблема и возможное ршение https://community.nxp.com/t5/i-MX-Processors/eMMC-5-0-boot-error-in-i-MX6D/m-p/602623

-

Пользователи

- gazpar

- dm_mur

- kochevkv

- alex2022

- HardEgor

- tony_copper

- Ozelot

- A.V.Avtomat

- sh007

- illich

- vsrb

- BOS

- тау

- DAV

- Палыч

- Пыщ-пыщ

- speleoastronom

- makc

- Zig

- zxc_pavel

- 3apw

- mcuprog

- Алексей ВМ1

- Alex_2015

- fighter_161

- Alex77

- aBoomest

- iosifk

- Михась

- Shamil

- Katatsuburi

- vguard

- stells

- remontsofta

- antis

- EdgeAligned

- kpv

- oratie

- uve

- ANATOLP

- НЕХ

- Burenkov

- Vasil_Riabko

- AlexMI

- MartensA93

- RDutch

- Ramil

- BigRed

- EugeneS

- GPP

- Flip-fl0p

- aegis

- Anxigeros

- whale

-

Статистика пользователей