Поиск

Показаны результаты для тегов 'eda'.

-

1. Главной проблемой была некорректная работа Hierarchy Updater’а: пока он не может корректно построить дерево проекта в тех местах, где в VHDL используются внешние модули (Verilog / IP-Core), но об этом я уже писал. 2. Для некоторых может быть непривычно и неочевидно, что (в строгом соответствии с VHDL’93) при использовании entity из библиотеки Work, необходимо указывать: library work; use work.all; 3. Несколько напрягает, что все справочные материалы на китайском. 4. Немного изменилась работа с атрибутами: для VHDL необходимо использовать Syn_* атрибуты (на 2023.1 достаточно было использовать PAP_* атрибуты – тогда было меньше warning/info о преобразовании Syn_* атрибутов в PAP_*). С другой стороны в ADS_Synthesis_User_Guide.pdf добавлено очень подробное описание правил применения Syn_* атрибутов с примерами на каждый случай. Но главной проблемой был п.1, т.к. приводил к падению Compile с «internal error» без объяснения причин падения. Отмечу, что Pango Micro старается сделать PDS/ADS лучше, с каждым шагом (2022.2-SP4->2023.1->2023.2-SP1) я отмечаю существенные сдвиги в лучшую сторону.

-

ПЛИС PangoMicro

Gas Wilson опубликовал тема в Работаем с ПЛИС, области применения, выбор

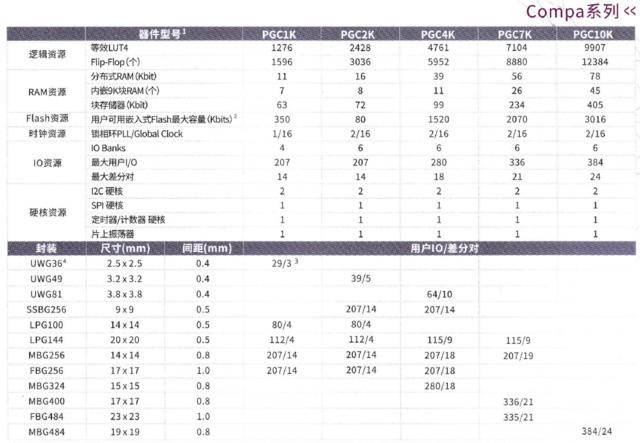

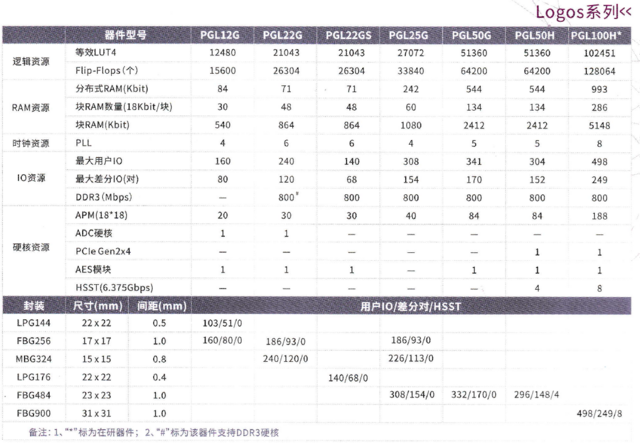

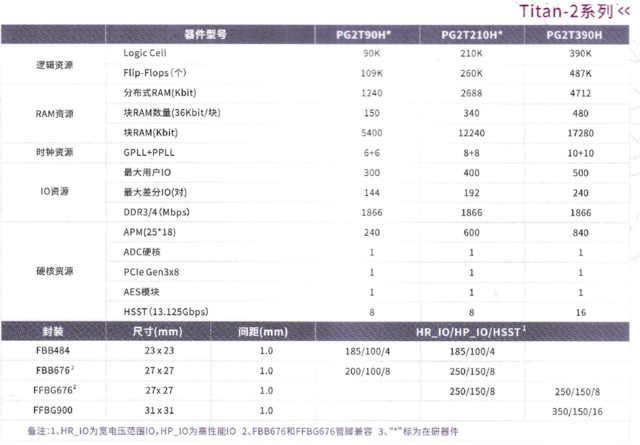

Даташиты на английском на семейства Compact, Logos 2 и Titan от Pango Micro. Перевод не супер, но легче ориентироваться, чем в китайском даташите. Logos - уровень Spartan 6 Titan - уровень Kintex 7 XC6SLX25 FTG256 -> PGL25G FBG256 XC7A50T FGG484 -> PG2L50H FBG484 XC7A100T FGG484 -> PG2L100H FBG484 XC7K325T FBG676 -> PG2T390H FFBG676 DS03001 Compact Family CPLD Device Data Sheet 1.5.pdf DS04001_Logos2 Family FPGA Device Data Sheet .pdf DS05001 Titan2 Series FPGA Device Data Sheet 1.pdf -

Моделирование проектов ПЛИС PangoMicro

Xagen опубликовал тема в Методы и средства верификации ПЛИС/ASIC

а как этот проект моделировать? У меня вообще серьезные проблемы с моделированием. Ни одно IP ядро не моделируется. Все падают с ошибками на этапе компилирования в modelsim или questasim. Судя по логам какая-то проблема с зашифрованными исходниками. Ругается на синтаксис в зашифрованном регионе. При этом в самом PDS синтезируется. -

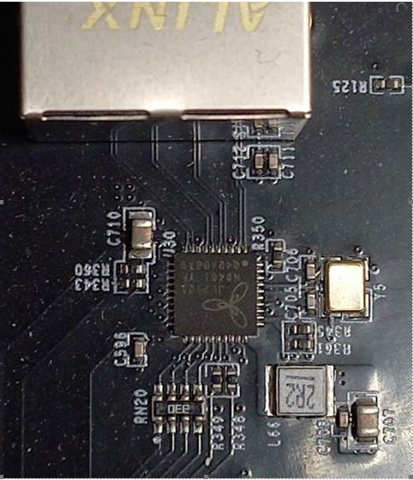

Добрый день! Может кому пригодится. Разбираюсь с платой AXP100 (с PG2L100H). На моей плате вместо указанного в документации PHY KSZ9031RNX оказался установлен PHY jl2121 с последовательными сопротивлениями (33 Ом) в цепях RGMII со стороны драйверов PHY. Пробовал запустить демо проект ethernet_test не заработал, искажались полученные FPGA полубайты. Проверил на другой плате AXP100 с KSZ9031RNX демо проект работал отлично. Начал разбираться с RGMII, предположил, что у по умолчанию jl2121 нет задержки rx_clk как у KSZ9031RNX (datasheet на jl2121 мне найти не удалось), но прицепившись логическим анализатором увидел задержку, плюс к этому пробовал задерживать rx_clk на разное время уже в FPGA, не помогало, так что причина была в другом. Сами искажения полубайтов выглядели так, как будто duty cycle у rx_clk на входе FPGA не 50%, повторялись старшие полубайты. Попробовал убрать последовательные резисторы соединив выходы PHY jl2121 напрямую с FPGA как в схеме подключения PHY KSZ9031RNX, это также не дало положительного результата. Правда, после того как восстановил резисторы тип искажений изменился, появлялись все полубайты но они были перепутаны, так как будто rx_clk был задержан больше требуемого на входе FPGA. Но это уже легко вылечилось инвертированием в FPGA rx_clk. Теперь ethernet_test работает с PHY jl2121.

-

ПЛИС PangoMicro Compact

Abo опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую, коллеги. Пришлось осваивать Панго серии компакт. Сделал простенький тестовый проект с использованием встроенного в микросхему генератора (в приложении весь проект). сделал констрейны на клоки и выходы. Однако при сборке получаю критическое предупреждение: "Place-2028: CASCADED_GLOBAL_CLOCK: the driver GTP_OSC_E2_inst/gateop fixed at OSC_11_174 is unreasonable. Sub-optimal placement for a clock source and a clock buffer." Не понятно, как от этого предупреждения избавиться. Чтение доступной документации и поиск не привели даже к догадке, где искать ответ. Может конечно не все прочитал. Прошу совета, куда рыть? Ну не могу я себе позволить оставлять в проектах даже предупреждения. pangotest.zip