Поиск

Показаны результаты для тегов 'altium'.

-

Выравнивание дифференциальных линий

Fillya опубликовал тема в Altium Designer, DXP, Protel

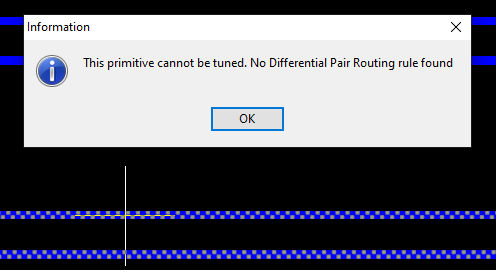

Доброго времени суток! При разводке дифференциальных линий возникла ошибка, которая не позволяет использовать опцию Interactive Differential Pair Length tuning. При попытке выделить дифф. пару такой опцией возникает поясняющее окно "This primitive cannot be tuned, No Differential Pair Routing rule found" хотя правила для разводки есть, более того их два для параметров дифф. линий на внешних и внутренних слоях, созданных для соответствующего класса. Также есть правило по максимальному разбегу длин этих линий, которое прекрасно отображается в окне PCB жёлтым цветом. Кроме того наблюдал такое явление - строго задан зазор, но в некоторых местах проводники могут сойтись на более близкое расстояние, по сути, нарушив правила, присвоенного для данного класса. В HyperLynx линии после экспорта считаются одиночными даже после присвоения им параметра DP в меню Setup и назначения моделей для дифференциальных интерфейсов (от имеющейся по умолчанию Virtex4.ibs). Кто нибудь встречался с такой проблемой? З.Ы. Был старый проект, эскизный. В нём вся плата работает (версия AD 15.0). Правила в нём были не все заданы, также не было отдельной сетки для одного из компонентов, из которого выходят линии. Других различий нет.- 6 ответов

-

- плата

- дифференциальная линия

- (и ещё 2 )

-

Схемотехник на небольшие работы

Samum421 опубликовал тема в Предлагаю работу

Нужен специалист c Allegro. Оплата по факту. -

Предлагаю услуги по трассировке ПП в Altium Designer

iron_fairy13 опубликовал тема в Ищу работу

Предлагаю услуги по трассировки печатных плат в Altium Designer. Имеется опыт трассировки печатных плат до 8 слоев. Выполнение трассировки плат с высокой плотностью монтажа. Также осуществляю услуги по оформлению, ведению и обновлению библиотек компонентов. Почта для связи: [email protected]- 1 ответ

-

- altium

- трассировка печатных плат

- (и ещё 1 )

-

Тополог г. Москва (high-speed PCB)

Kaola опубликовал тема в Предлагаю работу

Компания Бифорком Тек находится в поисках Инженера-тополога. Мы разрабатываем и производим телекоммуникационное оборудование, находимся в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Telegram: https://t.me/terina_ekat Также можно откликнуться на вакансию в hh.ru. Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Высшее техническое образование образование Работа в команде. Аккуратность; Нацеленность на результат, исполнительность и желание развиваться. Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики-

- топология

- маршрутизатор

- (и ещё 16 )

-

Компания Бифорком Тек находится в поисках тополога в свою команду RnD. Пару слов о нас. Мы существуем с 2015 года, занимаемся разработкой и производством продуктовой линейки высокотехнологичных устройств с использованием технологий SDN/IoT/4G/5G/6LoWPAN и решений в области передачи данных. Находимся в в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Ссылка на наш сайт - https://b4com.tech. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Также можно откликнуться на вакансию в hh - https://hh.ru/vacancy/72745516. Инженер-тополог: Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; Подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; Приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики; Компания внесена в реестр аккредитованных IT-компаний

-

Здравствуйте уважаемые знатоки. Столкнулись с такой проблемой: имеются gerber файлы и текстовый файл отверстий, необходимо просмотреть 3D модель платы и вытащить габаритные размеры для исправления чертежа.

-

Доброго времени суток! Задача звучит так: Нужно соблюсти зазор от края TH-пада компонента, располагающегося на слое Top до края SMT-пада компонента, располагающегося на слое Bottom. И наоборот, если TH-компонент находится на слое Bottom, зазор мы считаем до SMT пада компонента на слое Top. Сначала я пошёл по пути Component Clearance. Работало следующим образом: Зазор считался от 3д-модели контактов TH-компонента, которые торчали из платы с обратной стороны до 3д-модели корпуса SMT-компонента на обратной стороне. Этот вариант не подошёл, потому что корпуса разные, SMT-пады выступают за пределы корпуса по-разному и т.п. Затем я попробовал сделать через Electrical/Clearance. Если мы точно знаем, что все TH-компоненты на слое Top, а все SMT на слое боттом, то в одной части Custom Query пишем "IsSMTPin and OnBottomLayer", а в другой "IsThruPin and PadIsPlated" (да, мы выделяем любые металлизированные TH-пады, но если нам точно известно, что все TH-компоненты на слое Top, то это работает). Перестаёт это работать, если попадаются TH-компоненты на слое Bottom, а SMT компоненты на слое Top. Основная проблема в том, что я не могу указать, что нужно использовать TH-пады только для компонентов определённого слоя, так как TH-пад подразумевается, как Multilayer. Запросы формата "IsPad and IsThruComponent and OnBottom" не работают, вообще все запросы упираются в отметку слоя. Подскажите пожалуйста, есть у кого какие мысли, как можно выполнить задачу?

-

Необходимо перенести проект с STM8 на ATMEGA4808

Pavel_335 опубликовал тема в Предлагаю работу

Мы — 4Blind, международная инжиниринговая компания родом из России, мы создаём инновационные устройства и технологические решения, которые расширяют возможности слепых и слепоглухих людей в общении, образовании, трудоустройств и самостоятельной жизни. Нам нужно перенести проект с STM8 на ATMEGA4808. В проекте используются: Таймеры, АЦП, ЦАП (генерирование звука), GPIO, UART. Проект сделан в Altium.- 6 ответов

-

- stm8

- atmega4808

-

(и ещё 1 )

C тегом:

-

Разработка электронных систем. Москва.

vorrom опубликовал тема в Ищу работу

Разработка электроники. Полное ведение проекта, от проработки устройства, написания софта и firmware до отладки образца. FPGA Xilinx - проекты любой сложности. Опыт больше 20 лет. STM32 - включая BLE устройства. Большой опыт разработки для разных заказчиков. Altium Designer - разработка печатных плат. Опыт работы с JKLC PCB. Сделаны многие проекты. Написание приложений под ОС Android. ADC приложения и ЦОС (DSP). Почта для связи [email protected]- 2 ответа

-

- stm32

- fpga xilinx

- (и ещё 5 )

-

Altium. Многоканальный проект. Работа с шинами

shamrel опубликовал тема в Altium Designer, DXP, Protel

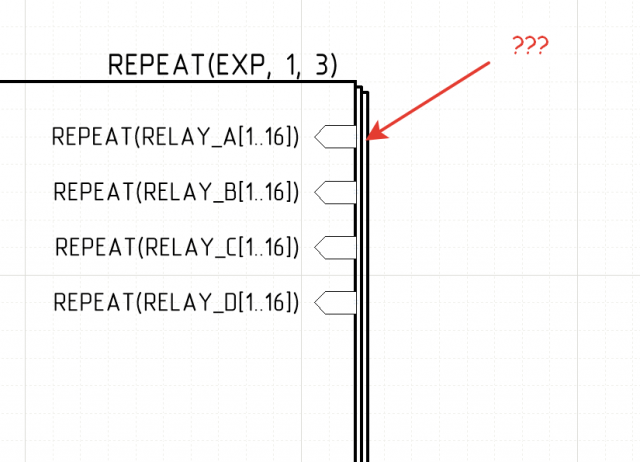

Приветствую. Сделать проект иерархическим -- не сама цель, просто у меня есть блок, который повторяется 64 (!!!) раза. Но речь не про него. Для вывода портов в шину используется функция Repeat. А как быть, если из повторяющегося блока выводит шина? Repeat здесь уже не работает. Я не думал, что это настолько редкая ситуация, чтобы в Altium не было для этого готового решения. Как быть? -

КД по ЕСКД в Altium Designer

Vadim Ivanov опубликовал тема в Altium Designer, DXP, Protel

Всем привет! Я очень давно зарегистрирован на форуме, практически 10 лет, но по большей части я был читателем. За это время я уволился с НИИ, в котором проработал 9 лет(работал в IT подразделении, внедрял Altium,Windchill PDM, MPMLink и занимался разработкой интеграционных решений) и стал заниматься продажей продуктовой линейки Altium и разработкой ПО. Мы с ребятами практически три года вели разработку нашего собственного решения Board Assistant и недавно выпустили 2 версию продукта. Board Assistant – программный комплекс для автоматизированного формирования КД на основе проекта, выполненного в Altium Designer (ПЭ, ВП, спецификация, чертёж на ПП, СБ, спецификация на ПП). Что нового в программе: поддержка Altium Designer 20 и Altium Nexus, с учётом тем оформления; учёт исполнений (Variants) и функциональных групп (SheetEntry) при формировании документации по ЕСКД; редактор документации – инструмент для формирования текстовой КД; формирование документа «Спецификация»; формирование документа «Спецификация на печатную плату»; сортировка отечественных элементов в соответствии с ЕСКД (группа, номинал, вольтаж и т.д.); возможность изменять настройки штампа, добавлять поля, менять толщины линий, шрифт; простановка позиций на сборочном чертеже в соответствии со спецификацией. Также были учтены замечания и предложения пользователей, исправлены ошибки. Любой желающий может скачать дистрибутив программы по ссылке: https://glavkon.com/boas В связи с не простой ситуацией в мире, мы раздаем бесплатные коммерческие годовые лицензии всем желающим до 30.04.2020 г. Для этого следуйте инструкции в видеоролике и пришлите ключ на [email protected]- 22 ответа

-

- altium

- altium designer

-

(и ещё 3 )

C тегом:

-

Инженер-разработчик РЭА, Москва

113 опубликовал тема в Предлагаю работу

Нужен разработчик электроники. В основном - носимые цифровые устройства. Опыт разработки обязателен. Работа в Altium. Схемотехника и трассировка. Грамотный подбор компонентов. ЕСКД - не обязательно. Обязательно - уметь самостоятельно разработать и запустить устройство. Офис в районе м. Кожуховская. Полный день, карьерный рост. ЗП от 140т.р. Умение программировать под ARM приветствуется. Контакты: [email protected] (903)685-78-47 Иван -

Дробление компонентов по зазорам между падами

morlord опубликовал тема в Altium Designer, DXP, Protel

Доброго времени суток! Есть задача - разбить все компоненты на 3 группы по расстоянию между падами и сделать разные зазоры между разными группами. Например, все компоненты с зазором между падами до 1.27 мм мы относим к группе А, с зазором от 1.27 до 2.54 мм относим к группе Б, а с зазором от 2.54 и больше к группе В. Теперь между компонентами группы А и Б нужно соблюсти зазор в 1 мм, между А и В - 2 мм и между В и Б - 3 мм. И написать правило в Альтиуме, которое будет отслеживать такие зазоры между группами компонентов. Рабочий вариант - считать ручками зазоры на футпринте и записывать в отдельный параметр компонента принадлежность к определённой группе. Однако компонентов много, это долго и в случае, если вытаскивать на PCB футпринт без параметров - правило не сработает. Поэтому хотелось бы считать зазоры внутри футпринта автоматически, но если это невозможно, то хотя бы задать в футпринте новый слой, на котором вести завести строку с текстом обозначающим группу. Слой я задал, выбирать весь текст на этом слое смог, но как выбирать не весь текст, а только текст, в котором есть "А" например? Уже всё перепробовал, ничего не работает. Либо весь текст на этом слое у всех компонентов, либо никакой. Подскажите пожалуйста, если кто-то сталкивался с подобным. Есть ещё вариант, который пришёл мне в голову. Группу можно прописать в описании футпринта "Description" и правилами цепляться за него, но проблема та же - как разделять компоненты с разными описаниями? -

Проверка зазоров между падами одной цепи.

morlord опубликовал тема в Altium Designer, DXP, Protel

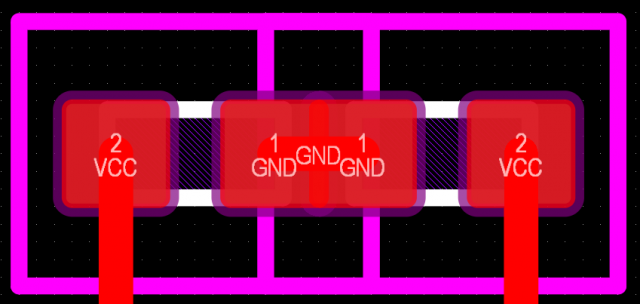

Всем добрый день! Возник вопрос по настройке правил в Altium Designer. Подскажите пожалуйста, может кто сталкивался с этим? Дано: два компонента (в данном случае два резистора), у которых есть по паду, принадлежащему одной цепи. Если разместить их так, чтобы пад одного резистора заходил на пад другого - проверка DRC не ругается. Вопрос: Как с помощью правил в Altium отслеживать такие моменты? Чтобы при наложении двух падов разных компонентов друг на друга вылезала ошибка? Спасибо, за внимание!- 9 ответов

-

- clearance rules

- rules

-

(и ещё 1 )

C тегом:

-

Открыть .Cam файл

DesinusMan опубликовал тема в Altium Designer, DXP, Protel

Подскажите пожалуйста, где еще можно открыть .Cam файл сделанный в Altium или изменить его формат, скажем, в DXF/DWG. Мне прислали .Cam файл и он открывает пустое окно в Altium. Открываю его же в CAMvu 14.1 и там уже готовая плата. Только он не дает возможности экспорта в другом формате. -

Открытие платы от маски

DesinusMan опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте. Можете ли вы подсказать, как делать вырезы в открытии от маски? (как показано на рисунке). Тобишь copper region в слое top solder открывает от маски, polygon cutout в этом же слое не убирает открытие маски. Такой же вопрос с линиями при их открытии от маски заданием параметра solder mask expansion. Тобишь возможно ли в участке, очищенном от маски при помощи region'a в слое top solder, сделать участок, который будет покрыт ей. (условно так, как показано на рисунке. Тобишь фиолетовое - очищенная от маски часть платы, а красное - покрытое)- 10 ответов

-

Altium 21 Копирование формата Room на угол

Altimist опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте, столкнулся с проблемой, есть 2 комнаты с компонентами (настроенные), при копировании формата 1й во 2ю копируется расположение компонентов как в 1й возможно ли в AD сделать так, что бы при копировании формата из 1й румы во 2ю расположение компонентов менялось допустим на 90 градусов? а не нужно было поворачивать 2ю в ручную. -

Part Swapping

nubO_O опубликовал тема в Altium Designer, DXP, Protel

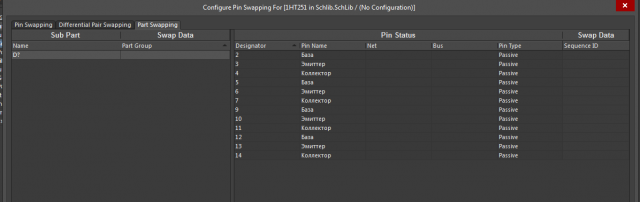

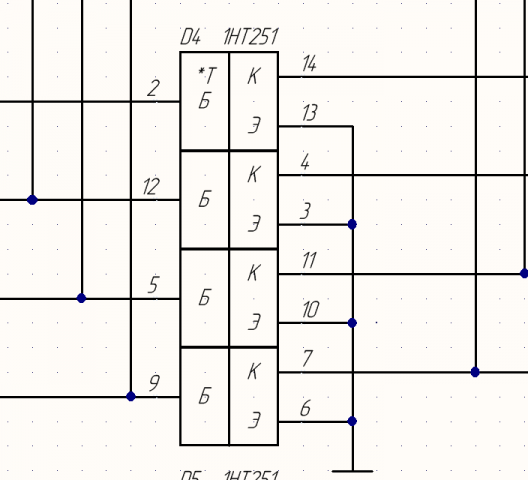

Здравствуйте. Осваиваю альтиум, и не могу разобраться, как настроить part swapping для компонента, имеющего одно уго (один part). По инструкции альтиума, для возможности парт свапа, я должен создавать компонент в виде набора этих парт свапов (тогда и в графе part swapping их будет несколько, и я смогу устанавливать эквивалентности между выводами). Но что делать, если у меня несколько партов в рамках одного уго (несколько транзисторов в матрице 1нт251, созданного, как на фото ниже)? Как "вручную" вбить несколько партов, и эквивалентности между выводами, как это легко можно было сделать в пикаде? Весь мозг расчесал себе, ничего не нашёл. Благодарю. -

Выравнивание нескольких цепей одного контакта

Evilpk опубликовал тема в Altium Designer, DXP, Protel

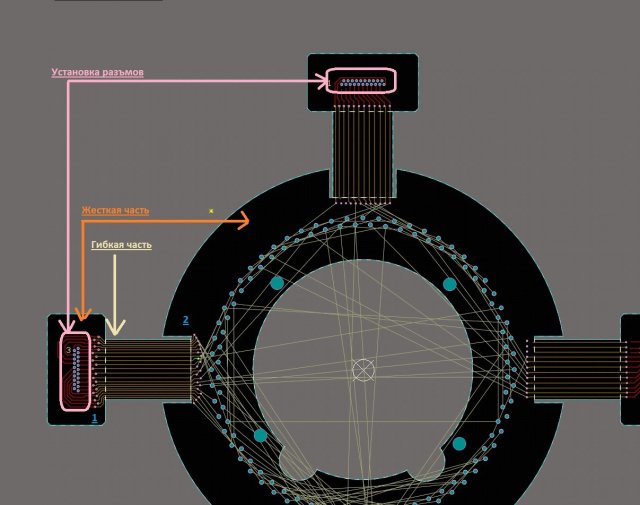

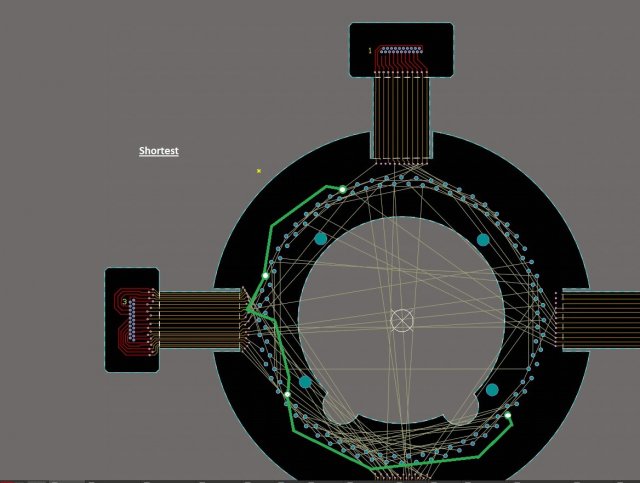

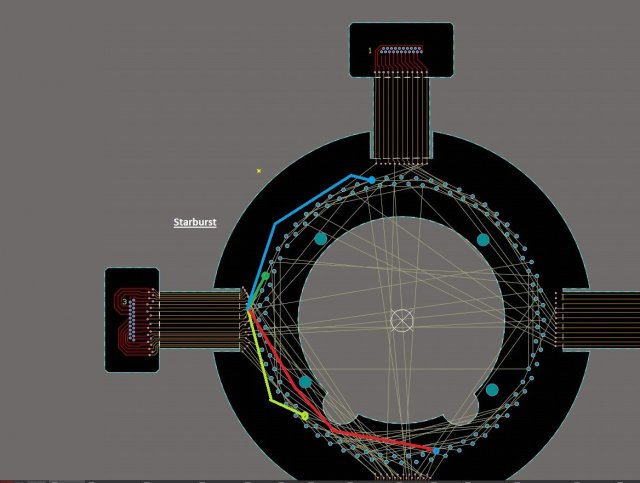

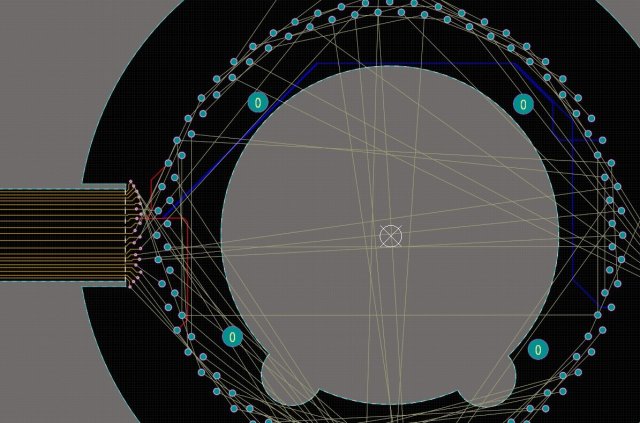

На первом изображении указаны гибкие и жесткие места и розовым указаны места, куда садится разъем сверху, и слева( ну еще справа и снизу есть). Цель: разводка цепей от этих разъемов до контактов, расположенных по кругу. От посадочного места под разъем идут коричневым(mid-layer на гибкой части) цепи до жесткой части. Там отверстия переходные(2) для выхода на слои top/bottom, чтоб потом уже для разводки на контакты по кругу. Проблема заключается в том, с одного контакта от разъема идет несколько веток на контакты круговые. Поэтому выбирая в Rules routing Topology типа Shortest. цепь идет от контакта разъема ПОСЛЕДОВАТЕЛЬНО до всех контактов(рис второй). А выбирая routing Topology типа Starburst цепи должны идти от общей точки переходного отверстия (2) на все контакты круговые(рис третий). По факту же все равно скрещиваются после общей точки(рис четвертый) и не выравниваются. Нужно в итоге получить все цепи одного сигнала из одной точки и Выравнить их по длине при постройки трассировки auto route. Но Matched Lengths на них как настроить если это одна цепь, а там вроде как между разными, но тогда как? диф пары тоже не получилось настроить, делал общую шину все обозвал. но приходит то на один общий контакт. Помогите советом новичку.- 18 ответов

-

- altium

- auto route

-

(и ещё 2 )

C тегом:

-

КУРСЫ по проектированию печатных плат

Skat-pro опубликовал тема в Altium Designer, DXP, Protel

Уважаемые коллеги! Учебно-консультационный центр «Skat-Pro» осуществляет набор на курсы по проектированию печатных плат. Обучение проводят высококвалифицированные преподаватели - сертифицированные компанией Altium Ltd. Ближайшие курсы в январе 1) ALTIUM DESIGNER. ПРОЕКТИРОВАНИЕ И КОНСТРУИРОВАНИЕ ЭЛЕКТРОННОЙ АППАРАТУРЫ (БАЗОВЫЙ УРОВЕНЬ) с 27 по 31 января 2) ОСНОВЫ ПРОЕКТИРОВАНИЯ ПОМЕХОЗАЩИЩЕННОЙ И ПОМЕХОУСТОЙЧИВОЙ АППАРАТУРЫ с 27 по 28 января Расписание всех курсов Подробная информация: [email protected], тел. +7(995)960-04-02.- 5 ответов

-

- печатная плата

- трассировка

- (и ещё 2 )

-

Ошибка в правилах разводки платы

sergafan4ik опубликовал тема в Altium Designer, DXP, Protel

При проверке разводки платы на ошибки выскакивают ошибки Minimum Solder Mask Constraint и Silk to Solder Mask Clearance Constraint. Как по вашему мнению, что можно поменять в правилах разводки или в схеме что-то? -

Экспорт печатной платы в старую версию

repstosw опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте! Столкнулся с таким фактом. Есть файл печатной платы, выполненный предположительно в DXP Protel старшей версии. Сконвертировал его в формат 5-й версии. Открыл Altium Designer'ом 6-й версии. Далее взял оттуда футпринт одной компоненты (состоит из одних падов TOP слое). Нарисовал УГО и отремапил его на этот футпринт. В итоге: связи между этим элементом есть, но они становятся видны только при перетаскивании элемента. Также при печати рисунка платы, принтер не распечатывает футпринт, но на чертеже он есть. Решил проблему удалением проблемного футпринта и его ручным перерисовыванием. Кто сталкивался, можете подсказать в чём может быть дело? Складывется впечатление, что футпринт оказался в "теневом бане" у САПР. -

Помощь с Altium Designer

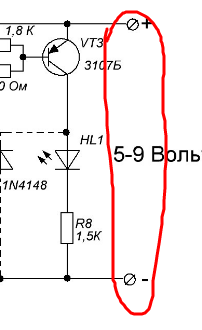

Kirill_Alehin опубликовал тема в Решение задач

Добрый день, помогите разобраться со схемой в Altium Designer. Как при создании схемы обозначать такие входы/выходы? Подойдет, если я на минус повешу землю, а на плюс порт? Извиняюсь за глупый вопрос, просто только первый курс, только начали проходить, а уже на дистанционку отправили самим разбираться -

Добрый день, друзья. Подскажите, пожалуйста, если кто сталкивался с такой проблемой: при разработке эл. схемы по ГОСТу допускается группировать однотипные элементы по определённому признаку, например для конденсаторов, резисторов это номинал. Как выглядит это на схеме отобразил в прикреплённом файле. Вопрос: есть ли возможность в Altium, в схемном редакторе сделать что-то подобное (когда в схеме около 100 конденсаторов по 0,1 мкФ рисовать это напрягает:) )? Спасибо. Группировка элементов.bmp

-

Инженер разработчик (Еатеринбург)

www... опубликовал тема в Предлагаю работу

В связи с выполнением новых проектов, в крупную организацию, ищем разработчиков в Екатеринбурге на полный рабочий день. Обязанности: -разработка аппаратной части электронных узлов и блоков(цифровая техника, аналоговая техника); -разработка топологии печатных плат (Altium) -разработка ПО микроконтроллеров(STM32, HAL); -разработка документации (конструкторской или программной). Требования: -высшее образование и стаж работы от одного года; -опыт работы с аналоговой и цифровой схемотехникой; -опыт разработки ПО микроконтроллеров на языке Си; -знание основных интерфейсов UART, CAN, I2C, SPI, Ethernet; Условия: работа связанная с разработкой авиационной техники; возможен гибкий график; работа в центре около станции метро; оформление и ЗП в соответствии с ТК РФ. Оклад от 50 000р, может быть увеличен по результатам собеседования в зависимости от квалификации и опыта. Оклад полностью "белый", сумма указана после вычета налогов. Так же по завершению этапов проектов дополнительно выплачиваются премии. Просим направить резюме с контактами, неразглашение информации из резюме третьим организациям гарантируем. [email protected]- 5 ответов

-

- екатеринбург

- altium

-

(и ещё 2 )

C тегом: