Поиск

Показаны результаты для тегов 'clearance rules'.

-

Проверка зазоров между падами одной цепи.

morlord опубликовал тема в Altium Designer, DXP, Protel

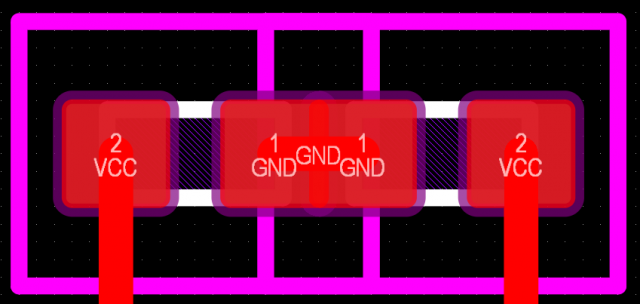

Всем добрый день! Возник вопрос по настройке правил в Altium Designer. Подскажите пожалуйста, может кто сталкивался с этим? Дано: два компонента (в данном случае два резистора), у которых есть по паду, принадлежащему одной цепи. Если разместить их так, чтобы пад одного резистора заходил на пад другого - проверка DRC не ругается. Вопрос: Как с помощью правил в Altium отслеживать такие моменты? Чтобы при наложении двух падов разных компонентов друг на друга вылезала ошибка? Спасибо, за внимание!- 9 ответов

-

- clearance rules

- rules

-

(и ещё 1 )

C тегом:

-

Всем доброго времени суток! Имеется плата с BGA 0.8, которую предполагается изготавливать в Резоните. Технологические возможности производства определяют зазор между дорожкой и КП VIA не менее 0.1 мм (параметр "Зазор между проводниками", Продвинутый (коэфф 1.5)) на внутреннем слое для фольги 0.18. При этом параметр "Зазор площадка - огибающий полигон" равен 0.15 мм, т.е. наблюдается явная асимметрия параметра зазора, чем это объясняется описано в темах форума Резонита и в общем вопросов не вызывает. Переходные отверстия используются диаметром 0.2 мм, площадка 0.45. В CES заданы правила зазоров: Trace to VIA = 0.1 mm, VIA to Plane = 0.15 mm. При этом в параметрах Plane Classes and Parameters в Layout задан отступ от всех прочих объектов (Other object (minimum)) = 0.25 mm. Под BGA 0.8 для обеспечения устранение разрывов в полигоне с помощью Padstack processor удалены неподключенные КП VIA, но при этом оказывается, что дорожки могут приблизиться к оставшимся от VIA металлизированным отверстиям на те же самые 0.1 мм (заданные правилом Trace to VIA), что неправильно. Полигоны, благодаря параметру "Other object (minimum)", оказываются на требуемом расстоянии от отверстий VIA и с этим пока всё хорошо. При этом, естественно, разрывы в полигонах устраняются и всё становится более-менее красиво. Но оставшаяся проблема с трассами не даёт покоя и для ее решения я попробовал задать параметр "Additional Drill Hole Conductor Clearance, равный 0.15 mm: Однако это вполне предсказуемо привело к неприятному эффекту в виде снова появившихся разрывов в полигонах, т.к. 0.1 + 0.15 = 0.25 для трасс (все хорошо, как и требовалось) и 0.15 + 0.15 = 0.3 для полигонов - даёт разрывы в полигонах (0.8 (шаг BGA) - 2*0.3 (двойной отступ) - 0.2 (диаметр отверстия) равно нулю, а нужно хотя бы 0.1 мм). В связи с этим вопрос: как правильно задать правила в CES, чтобы с одной стороны соблюдалось правило отступа меди не менее 0.25 мм от металлизированного отверстия, а с другой стороны отступ 0.1 между проводниками и 0.15 отступ между контактными площадками и полигонами? Как вы решаете эту проблему? Пока приходит в голову только одно решение: создать Rule area под BGA 0.8, в котором бы параметр VIA to plane был бы равен 0.1, а по всей остальной плате 0.15. Теоретически это должно быть допустимо, т.к. полигоны под BGA напоминают швейцарский сыр и мест где бы встречались КП VIA и полигоны практически нет, а там где есть ширина области полигона сопоставима с шириной широких дорожек.

-

- ces

- clearance rules

-

(и ещё 2 )

C тегом: