Поиск

Показаны результаты для тегов 'ddr4'.

-

Серверные модули памяти от MMY

МакроГрупп опубликовал тема в Объявления пользователей

Компания MMY объявила о расширении своей линейки модулей памяти DDR4 формата R-DIMM 8-64 ГБ. Подробнее -

Тополог г. Москва (high-speed PCB)

Kaola опубликовал тема в Предлагаю работу

Компания Бифорком Тек находится в поисках Инженера-тополога. Мы разрабатываем и производим телекоммуникационное оборудование, находимся в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Telegram: https://t.me/terina_ekat Также можно откликнуться на вакансию в hh.ru. Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Высшее техническое образование образование Работа в команде. Аккуратность; Нацеленность на результат, исполнительность и желание развиваться. Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики-

- топология

- маршрутизатор

- (и ещё 16 )

-

Компания Макро Групп стала официальным дистрибьютором твердотельных накопителей, модулей памяти и микросхемам памяти MMY. Подробнее

-

Компания Бифорком Тек находится в поисках тополога в свою команду RnD. Пару слов о нас. Мы существуем с 2015 года, занимаемся разработкой и производством продуктовой линейки высокотехнологичных устройств с использованием технологий SDN/IoT/4G/5G/6LoWPAN и решений в области передачи данных. Находимся в в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Ссылка на наш сайт - https://b4com.tech. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Также можно откликнуться на вакансию в hh - https://hh.ru/vacancy/72745516. Инженер-тополог: Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; Подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; Приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики; Компания внесена в реестр аккредитованных IT-компаний

-

Компания Alliance Memory объявила о расширении своего портфолио CMOS DDR4 SDRAM новыми «A» версиями микросхем объёмом 4 Гбит в 96- и 78-шариковых корпусах FBGA соответственно – серии AS4C256M16D4 и AS4C512M8D4. Подробнее

-

DDR4 Aria10 С чего начать?

Станислав-- опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Передо мной стоит задача подключить к отладочной плате ПЛИС Aria10 комплект памяти DDR4 Hilo (та что идёт в комплекте) и далее буферизировать на ней выборки снятые с АЦП. Поделитесь пожалуйста материалами и гайдами для подключения ddr4 Спасибо -

Компания ARRIVAL создает современный коммерческий электрический транспорт таким, каким он должен быть: доступным, элегантным, тихим и безопасным. Одна из наших основных задач - разработать электрический автомобиль, который будет стоить не дороже аналогичного автомобиля с бензиновым двигателем как по цене покупки, так и по стоимости владения. Чтобы этого достичь, мы стараемся оптимизировать каждый этап его создания - от проектирования, разработки всех компонент, используемых материалов и до программного обеспечения. Программное обеспечение автомобиля (от контроллеров движения до систем искусственного интеллекта), а также сопутствующие сервисы мы разрабатываем в Санкт-Петербурге, автомобили собираются в Банбери (Англия). Мы ищем опытного, увлеченного Инженера-схемотехника, знакомого с "черной магией" трассировки высокоскоростных интерфейсов для разработки высокотехнологичных платформ, интегрированных в продукты ARRIVAL. Ваши будущие задачи: Разрабатывать электронные устройства: разработка схем электрических принципиальных, трассировка многослойных печатных плат. Участвовать в наладке, тестировании, испытаниях и сдаче в эксплуатацию изделий. Взаимодействовать с поставщиками компонентов. Сопровождать производство. Мы ждем от вас: Опыт разработки многослойных печатных плат с высокоскоростными интерфейсами (LVDS; DDR4; FPD-Link III (IV); CSI; GigEthernet; PCIe; SATA; GMSL). Опыт проработки высокоуровневой архитектуры устройств. Отличное понимание схемотехники, цифровых интерфейсов, целостности сигнала, помехоустойчивости, умение производить расчеты импеданса цепей, механической прочности платы, тепловыделения элементов на печатной плате. Знание аналоговой и цифровой электроники, знание современной элементной базы. Опыт разработки цифровых и аналоговых электронных устройств. Опыт работы с одним из САПР разработки и трассировки печатных плат (Altium Designer, Cadence OrCAD Capture, Mentor Graphics Expedition PCB, HyperLynx). Опыт отладки и запуска разработанных устройств. Знание измерительной аппаратуры (осциллограф, мультиметр), умение работать с ней, умение обращаться с паяльником. Хорошим дополнением будет: Опыт разработки встраиваемого ПО для микроконтроллеров ARM. Опыт тестирования аппаратной части устройства с использованием программных средств Linux, bash, python, C/C++, etc. Опыт разработки, отладки драйверов, модулей ядра для Linux. Знание SolidWorks. Знание CAN\LIN. Мы предлагаем: Участие в создании новых высокотехнологичных устройств на старте проектов. Увлеченную своим делом команду. Достойную заработную плату по результатам собеседования. Современный офис в Приморском районе Санкт-Петербурга. Условия работы: оформление по ТК РФ + доплата до 100% оклада для больничных и отпусков, полный пакет ДМС, компенсация затрат на занятия спортом и/или изучение иностранного языка, бесплатные горячие обеды в офисе. Буду рада ответить на вопросы по вакансии. Моя почта: [email protected] Спасибо за внимание! Катя HR manager Arrival

-

DDR4

NDPaw опубликовал тема в Форумы по интерфейсам

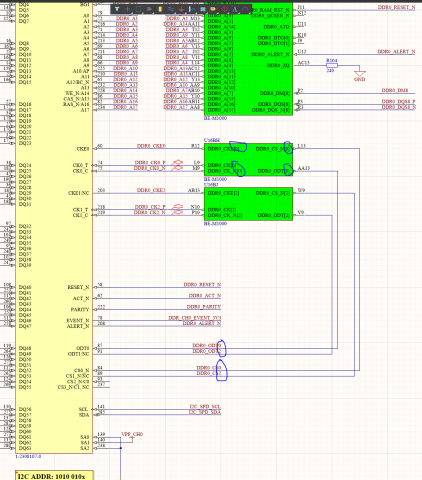

Добрый день, уважаемые форумчане! Есть вопрос к подключению планок DDR4. Как подключать сигналы CKE[0..3], CK(CK_N)[0..3], CS_N[0..3] и ODT[0..3] к четырем планкам DDR4. Видел, что подключают так [0,1] к одной плашке памяти, а [2,3] к другой. Можно ли подключить к одной плашке эти сигналы с индексами [0,2], а к другой - с индексами [1,3]? Рисунки для наглядности прилагаю. С уважением. -

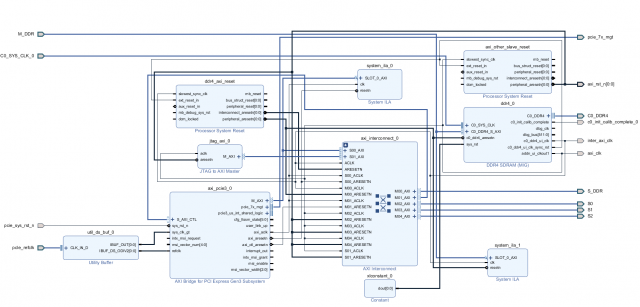

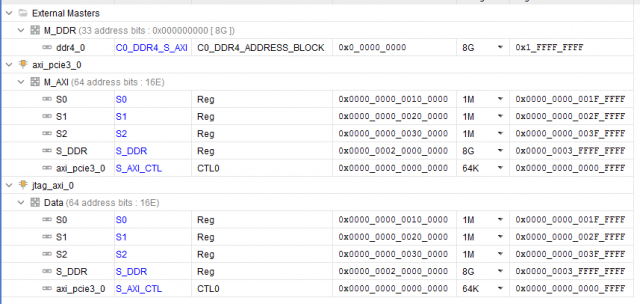

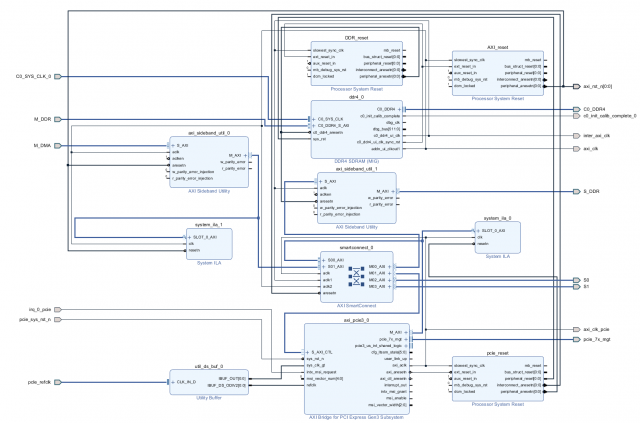

Добрый день. Долго работал с Intel (Altera) бед не знал в среде Quartus и вот пришлось перейти (к глубокому сожалению) на работу с Xilinx... Сразу был разочарован, многое из того, что доведено до автоматизма у Intel тут нужно делать самому, вникая в низкоуровневые тонкости. Очень большие ограничения на использования ip-ядер (плюс скудный набор изменяемых параметров) и плохие тайминги заводят меня в тупик. Так вот, какова суть проблемы. Работаю с Kintex Ultrascale. Понадобилось собрать систему из ядра PCIe -> interconnect ->DDR4. Прочитал кучу мануалов (PG194 v3.0, PG059 и тд.., Ответы с форумов, Видео пример настройки, Вивадовские примеры). В общем собрал систему похожую на систему из примеров. Рис. 1 Тут добавил ещё Jtag консоль для удобства отладки (в дальнейшем необходимо заменить её на свой блок ДМА), вывел интерфейсы для своих слейвов наружу. ДДР тоже вывел наружу (как S_DDR) на верхнем уровне закольцевал и вернул обратно (как M_DDR, опять же дикость связанная с XILINX пришлось решать одну из его проблем таким образом). Повесил ещё пару ИЛА для отладки и отображения шины АXI. Назначил адресные пространства. Рис. 2 Вроде всё задышало. Но с большими слеками на интерконнекте... То PCIe сама развестись не может, то на ядре ДДР какие то проблемы по таймингам. В общем всё плохо, но как то работает. По PCIe есть доступ и к DDR и к регистрам в слейвах, вроде всё корректно. Начинаю работать через Jtag консоль (в дальнейшем её нужно заменить своим блоком ДМА) и всё, ДДР не читается не пишется, комп умирает, интерконнект виснет. Проблема только при обращении к ДДР, при работе с моими слейвами регистровыми проблем нет, данные корректно пишутся и читаются. Залез по ИЛА и увидел что от ДДР не доходит сигнал BVALID и BID через интерконнект. Собственно из ДДР он вышел, но через интерконнект до второго мастера он не приходит, а для первого без проблем, всегда всё хорошо. Окей, меняю местами Jtag и PCIe та же шляпа. Jtag работает корректно, до PCIe не доходит BVALID и BID. Получается что второму мастеру по счёту просто не даётся доступ к ДДР. Листал форумы, читал советы, нашёл. Говорят что на Ultrascale и Ultrascale+ стандартный интерконнект не работает корректно, нужно ставить некий "SMARTCONNECT"... Ну окей.. читаю документацию, разбираюсь, вставляю смартконнект.. А у него оказывается выкидывает все ID(r/w/b) на шине AXI. Чтобы ID не выкидывались, ставьте "axi sideband" (говорит XILINX) до и после интерконнекта на каждой шине.. окей, поставил. Спустя все эти манипуляции я получил рабочую схему, которая может работать с двумя мастерами и без проблем читать и писать в ДДР. Рис. 3 Но эта штука разводится очень плохо. Сложность в том, что у AXI PCIe максимальная частота 250МГц, у ДДР в моём режиме (1200МГц частота памяти) AXI DDR 300МГц. Слейвы свои на такой частоте я не потяну, иначе вообще всё по таймингам умрёт... пришлось ставить в 2 раза меньше. Поставил 150МГц на слейвах. В итоге интерконнект городит очень сложную структуру из ядер клоковых конвертеров, конвертеров данных, протоколов и тд.. А потом при имплементации на эти же ядра и ругается Вивадо. Долго бьюсь над этой проблемой, не могу нормально побороть слеки. Пришлось понизить частоту ДДР до 1000МГц, соответственно AXI DDR стала 250Мгц, а частота моих слейвов 125 МГц. Слеки явно улучшились, работать можно, но проблема совсем не ушла. Как мне правильно настроить систему, чтобы не было конфликтов между ядер XILINX и всё нормально разводилось при требуемых параметрах?

- 17 ответов

-

- xilinx

- ultrascale

-

(и ещё 4 )

C тегом:

.jpg.f84f482ed0f7fac9dae6e0d63a167b4c.jpg)