Fillya

Участник-

Постов

35 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Fillya

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Здравствуйте! Что как с программными пакетами, может быть возможна заливка на Rutracker данного набора программ?

-

Расшифровка названия материала ПП

Fillya опубликовал тема в Работаем с трассировкой

Здравствуйте! Столкнулся со следующей проблемой. Есть различные материалы (ядра и препреги) различных производителей и, соответственно, для заказа предлагаются различные полные наименования. При этом на сайте я не могу найти расшифровку для материала так, как это было бы для какого-либо элемента. В частности для материалов ISOLA IS420ML 0.250B H018/H018 и DURAVER-e-Cu 104 ML. Стандарты IPC, откуда и взяты, как я понял, данные сокращения, полноценные тоже найти не могу (только вырезку). Наверное, простую плату на изготовление можно и так отправить, будет работать из чего сделают, но всё же хотелось бы понять, что да как в мире поставки материалов (и указать это в Altium Stackup Manager, где же ещё...). До сих пор выяснил, что 104 это тип материала (плетения стекловолокна и содержания смолы, H018... это толщины меди с двух сторон ядра, B это вроде принадлежность к какому-то классу по IPC, а вот ML и 0.250 пока остаются загадкой. Заранее благодарен за просвещение в нелёгком вопросе поиска расшифровок! -

Я, честно говоря, только начал знакомство с Linux (RHEL потому что именно она мне нужна в данный момент), и по этой причине тыкнулся в отсутствие первого пакета, которые увидел (5.6) и решил, что его нет. Наверное, привычка от Windows... Спасибо за ответ, посмотрю в репозитории, наверняка там действительно лежит самая новая версия. Спасибо за ответ! Если установка с помощью make остаётся невидимой для yum, то есть ли "правильный" способ удалить всё установленное (а не только удалить созданный каталог), чтобы откатиться на этап # yum install libX11-devel freetype-devel zlib-devel libxcb-devel \ libxslt-devel libgcrypt-devel libxml2-devel gnutls-devel \ libpng-devel libjpeg-turbo-devel libtiff-devel gstreamer-devel \ dbus-devel fontconfig-devel И попробовать ещё раз, не опасаясь того, что какие-то старые данные остались в системе и могут помешать новой установке?

-

Доброго времени суток. Мне для Linux RHEL 6.1 необходимо установить wine, для последующей установки посредством данной программы дистрибутивы под Windows. Для этого я выполнил следующие действия: Оформил подписку через менеджер и скачал обновления: # subscription-manager register # subscription-manager attach --auto # yum clean all # yum update # yum groupinstall 'Development Tools' # yum install libX11-devel freetype-devel zlib-devel libxcb-devel \ libxslt-devel libgcrypt-devel libxml2-devel gnutls-devel \ libpng-devel libjpeg-turbo-devel libtiff-devel gstreamer-devel \ dbus-devel fontconfig-devel После я начал непосредственно установку wine: # cd /usr/src # wget https://dl.winehq.org/wine/source/5.x/wine-5.6.tar.xz # tar -Jxf wine-5.6.tar.xz # cd wine-5.6 # ./configure --enable-win64 После чего консоль вернула мне ошибку, связанную с отсутствием некоторого bison соответствующей версии. Устанавливаю его: # wget http://ftp.gnu.org/gnu/bison/bison-3.4.tar.gz # tar -zxvf bison-3.4.tar.gz # cd bison-3.4/ # ./configure На этом этапе он мне выдаёт несколько предупреждений о том, что у меня нет OpenGL и некоторых других программ, поэтому они поддержаны не будут, я пропускаю: # make # make install Думаю, что программа установилась (так и есть, судя по всему), возвращаюсь к установке wine с этапа конфигурации: # ./configure --enable-win64 После этого он мне выдаёт новую ошибку, также на изображении видны соответствующие архивы и каталоги с в файловой системе. Объясните, в чём я ошибаюсь при установке и почему появляется ошибка, также мне неясно, почему раз bison-3.4 установлен, я его не вижу с помощью команды # yum list all (зато вижу несколько файлов, подсвеченных в списке жёлтым и красным). И могу ли я удалять каталоги bison-3.4 и wine-5.6 (и как правильно это сделать)? Заранее благодарен за помощь!

-

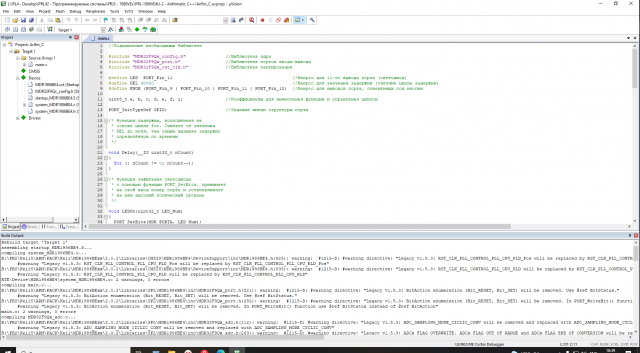

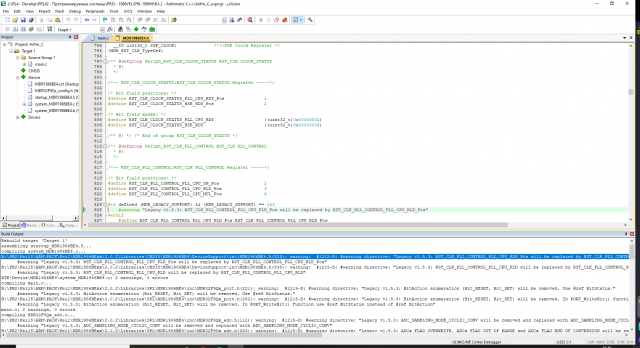

Спасибо большое! Как вы и говорили, все трудности ушли. Касательно MDR_LEGACY я понимаю, что они хотят обновлять содержимое библиотек и внесли в версию предупреждения по этому поводу, а что касательно extern "C"? У меня нет старых версий, но кажется данное выражение там было. Можно услышать о том, почему такое включение сработало и предположение о том, почему его изначально там не было? Заранее благодарен за доп. ответы :)

-

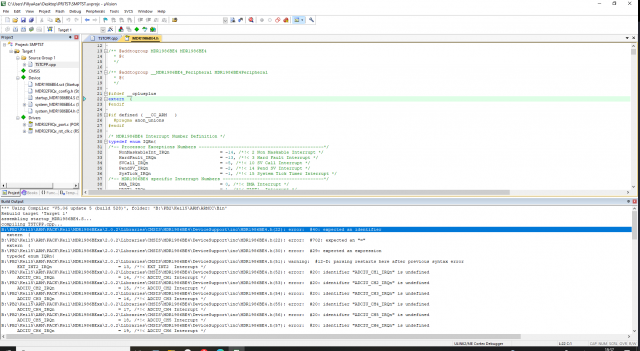

Я не могу убрать явно включённые файлы - они подключаются автоматически после включения библиотек ядра и периферии в Manage Run-time Environment и функции удаления для них нет. После компиляции они все, как вы и говорите, присутствуют в виде списка под соответствующим исходником. З.Ы. Убрал библиотеку Core, оставил только драйвера блока тактовых частот и портов ввода-вывода - ошибки те же самые, а категория CMSIS исчезла

-

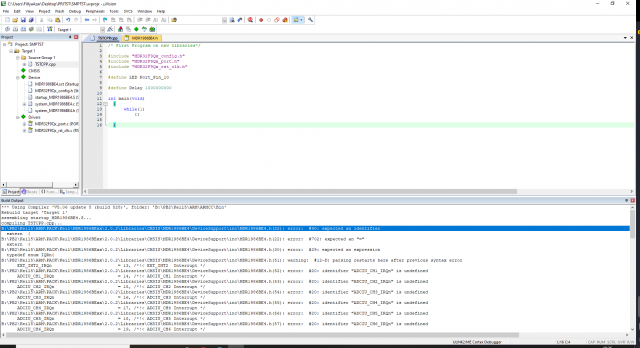

Доброго времени суток. После пары программ на STM32 (я не очень опытный программист) решил попробовать отечественный контроллер 1986ВЕ4У. Написал на нём в своё время несколько программ и они работали. При открытии через год тех же программ, они работают (хотя появляются предупреждения вида (прил. 1). При попытке создать новый пустой проект появляются ошибки, которые начинаются с библиотечных (прил. 2). Кто-нибудь может подсказать, в чём тут дело? Допускаю, что может я что-то забыл.

-

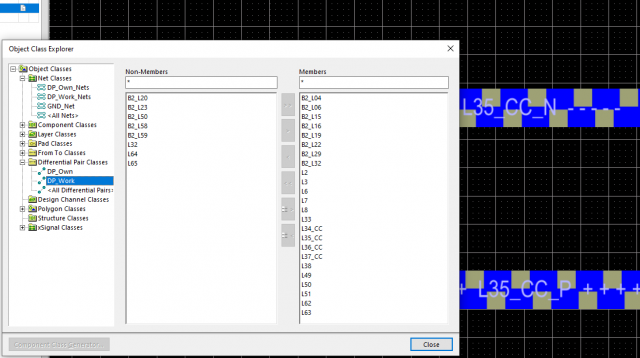

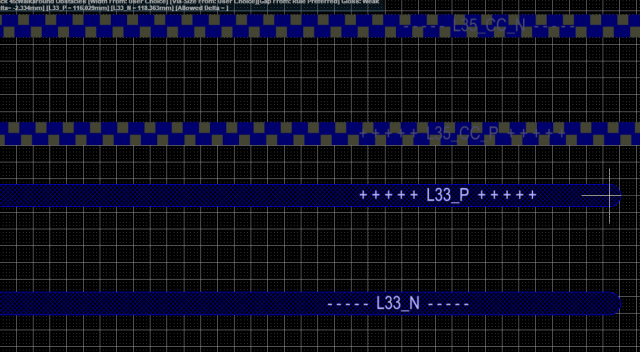

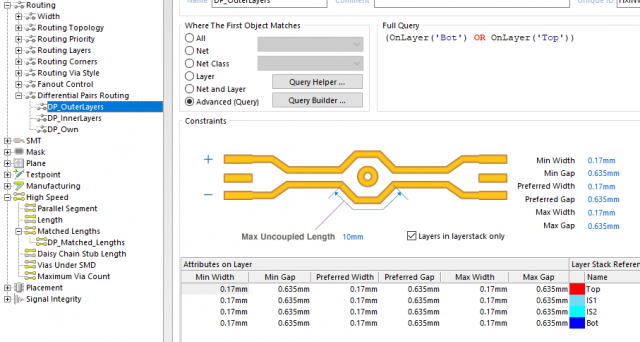

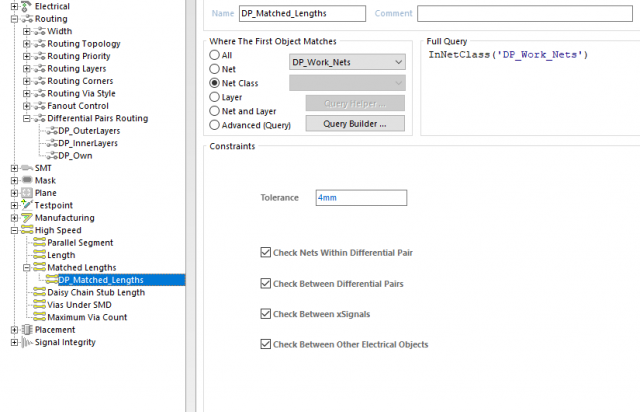

Правила для разводки работают на всех слоях, трассы изменяются после перехода через ПО. Инструменты также все работают, я развожу вблизи инструментов In. diff. pair routing, в пространстве платы multi-routing. Для заданных линий правила применяются, для мою выделенных отдельно не применяются - в соответствии с задумкой. Не работает только выравнивание именно для дифференциальных пар. Возможно, исходя из второй строки ваших предположений, стоит к классам слоёв, для которых определены правила, также добавить и класс пар, чтобы наверняка указать системе на принадлежность одного к другому. Класс с All попробую добавить. Соответственно на изображениях видно, что всё есть и всё работает. Правка вручную при отсутствии автоматизированного редактирования дифференциальных пар - довольно долгое занятие, которого хотелось бы избежать. По поводу замечания - я считаю, что дифференциальная линия (пара) всё таки пара, то есть пара линий, которые управляются двумя транзисторными каскадами, работающими противофазно и создающими два сигнала различной полярности, которые схлопываются на резисторе у нагрузки, образуя у входов приёмника полезный сигнал. Конечно, при сильном разнесении двух линий теряются основные преимущества дифференциальной пары, но тут есть и некоторые явные и не очень, пусть и не такие значительные, но преимущества, которые я использую в данной разводке потому-что могу и потому что удобно, ну и потому что работать будет, как только я решу возникшую задачу с САПР) З.Ы. На самом деле в основном потому что просто удобно и пространство позволяет в данной плате.

- 6 ответов

-

- плата

- дифференциальная линия

- (и ещё 2 )

-

Будет по-вашему. "Излишек" я удалил, "Кусочек" я добавил, очень верю в то, что мне это поможет (в очередной раз справиться с какой-то невероятной особенностью программы). Так же замечу, что редактировать одну линию (Equalize Net Length) вполне себе можно в соотв. с правилом. Даже не знаю, может какие-то правила конфликтуют

- 6 ответов

-

- плата

- дифференциальная линия

- (и ещё 2 )

-

Выравнивание дифференциальных линий

Fillya опубликовал тема в Altium Designer, DXP, Protel

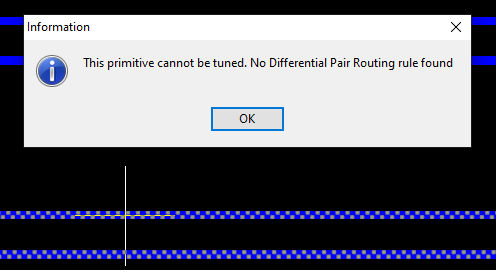

Доброго времени суток! При разводке дифференциальных линий возникла ошибка, которая не позволяет использовать опцию Interactive Differential Pair Length tuning. При попытке выделить дифф. пару такой опцией возникает поясняющее окно "This primitive cannot be tuned, No Differential Pair Routing rule found" хотя правила для разводки есть, более того их два для параметров дифф. линий на внешних и внутренних слоях, созданных для соответствующего класса. Также есть правило по максимальному разбегу длин этих линий, которое прекрасно отображается в окне PCB жёлтым цветом. Кроме того наблюдал такое явление - строго задан зазор, но в некоторых местах проводники могут сойтись на более близкое расстояние, по сути, нарушив правила, присвоенного для данного класса. В HyperLynx линии после экспорта считаются одиночными даже после присвоения им параметра DP в меню Setup и назначения моделей для дифференциальных интерфейсов (от имеющейся по умолчанию Virtex4.ibs). Кто нибудь встречался с такой проблемой? З.Ы. Был старый проект, эскизный. В нём вся плата работает (версия AD 15.0). Правила в нём были не все заданы, также не было отдельной сетки для одного из компонентов, из которого выходят линии. Других различий нет.- 6 ответов

-

- плата

- дифференциальная линия

- (и ещё 2 )

-

Доброго времени суток. После попытки регистрации системы, установленной на win10 через VirtualBox с проверенным наличием доступа в сет, нет возможности зарегистрировать систему ни через консоль, ни через графический интерфейс. После ввода логина и пароля открывается окно "Регистрация системы" со строкой загрузки и подстрочной надписью "Получение списка организаций", которое продолжает работать неопределённое время без каких-либо результатов.

-

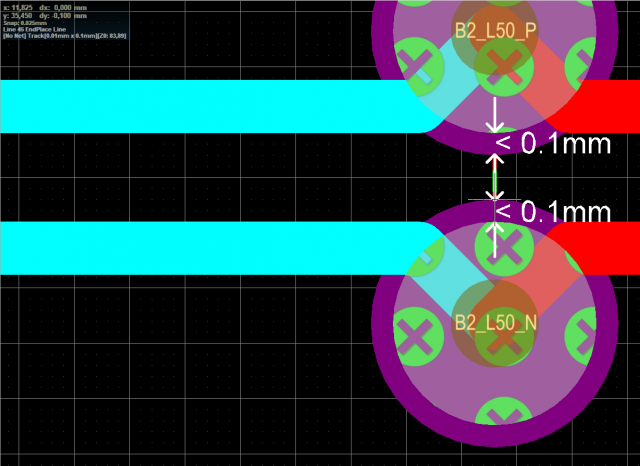

Доброго времени суток. В продолжении вопросов о работе с редактором печатных плат. Столкнулся со следующим - можно ли при интерактивном разведении дифференциальной пары, при переходе на другой слой (Ctrl + Shift + Колёсико) делать так, чтобы переходные отверстия расходились друг от друга на определённое расстояние (зазор) автоматически? Сейчас у меня расстояние между двумя линиями пары 200 микрон, а между участками вскрытия паяльной маски переходные отверстий - 100 микрон (то есть отверстия устанавливаются центрами по ближайшей возможной ширине между линиями из правила), хотелось бы увеличить данный зазор до 200-300 микрон. В редакторе окне правил есть таковые для расстояния между краями стволов (holes), между металлизацией элементов, но в моём случае (при автоматической установке переходных отверстий при интерактивной трассировке), установление данных правил не оказывает никакого влияния на положение отверстий. Есть способы решения такой задачи? З.Ы. Отверстия подсвечены ошибкой из за того, что между ними провёл обычную линию, без неё ошибок не будет.

-

Спасибо, помогло.

-

1. Имеется ввиду, что есть соединитель уже готовый. кем-то нарисованный. Я для него в своём проекте использую отдельную сетку для удобства разводки, но контактные площадки (их 4 ряда) данного соединителя (их центры) не желают вставать в перекрестья сетки, Я так понимаю, что всё посадочное место центрируется относительной какой-то одной точки, а мне хотелось бы, чтобы соединитель встал ровно именно контактными площадками по сетке. 2. Да, изменение зазора, но не как правило, а как часть описанной геометрии. Как вы подтвердили, это будет невозможно, т.е. либо копировал-вставил, как ответили вы, либо делать Snippet, либо можно попробовать извратиться скриптами,

-

После установки по необходимости Linux, сначала версии 8.4, затем версии 6.7, столкнулся с тем, что не могу создать общую папку Win10-Host RHEL6.7-Gost. Если кто-то уже сталкивался, опишите алгоритм с подробностями, по руководствам в сети до ума ничего довести не смог (из того, что выглядело, как подходящее для Red Hat. Может, мне нужны заранее какие-то приложения накатить на систему. З.Ы. Gost Additions я устанавливаю, соответствующий знак появляется на экране ОС, а вот дальше с получением доступа к папкам, заданным в VirtualBox начинаются трудности (на RHEL 8.4 я не мог получить к ним доступ, на 6.7 они и вовсе не желают появляться).