-

Постов

3 866 -

Зарегистрирован

Весь контент Maverick_

-

Понял спасибо Я просто выделил несколько файлов и перетащил...

-

Добрый день. Здесь выложил несколько файлов В результате для скачивания получилась "цельная строка": Мне кажется если файлы для скачивания будут представлены в виде столбца будет лучше

-

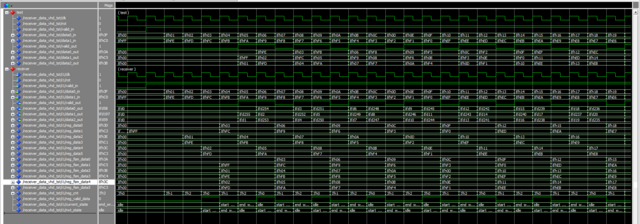

des00 за намек спасибо. Ниже скрин симуляции: файлы реализации и тестбенча во вложении wave.do c.do receiver_data.vhd receiver_data_vhd_tst.vhd Решение я уже привел, я не знаю как по другому пояснить задачу, которую мне надо было реализовать... Сформулируйте Вы - интересна Ваша формулировка моей задачи...

-

Не понял Вас ... Если можно поясните пожалуйста Спасибо, попробую

-

pipeline 2 bytes to 3 bytes

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день Что-то я не могу придумать как сделать. Мне надо принимать паралельно 2 байта, а выдавать паралельно 3 байта: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity receiver_data is generic ( BYTE_WIDTH : integer := 8; BYTES : natural := 1 ); Port ( clk : in std_logic; rst : in std_logic; valid_in : in std_logic; data0_in : in std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data1_in : in std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); valid_out : out std_logic; data0_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data1_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data2_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); ); end receiver_data; Подскажите пожалуйста как такое реализовать? -

work Pin Planner (Quartus standart)

Maverick_ опубликовал тема в Среды разработки - обсуждаем САПРы

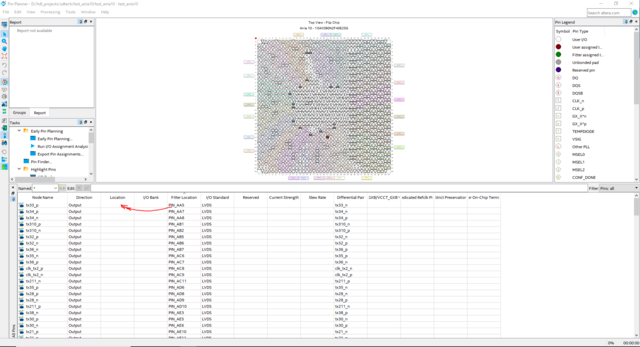

Всем привет Квартус скомпилировал проект и предварительно назначил пины. В Pin Planner они появились в клонке Fitter Location. Можно ли их переместить/скопировать в клонку Location? Если да, подскажите пожалуйста как это сделать Разобрался, обычное копирование колонки Выделил данные колонки -> копировать -> выделил колонку в которую вставить -> вставить -

LVDS SERDES

Maverick_ ответил Maverick_ тема в Среды разработки - обсуждаем САПРы

wolfman спасибо за информацию -

LVDS SERDES

Maverick_ ответил Maverick_ тема в Среды разработки - обсуждаем САПРы

Подскажите пожалуйста когда Вы работали с LVDS ставили внешние микросхемы или делали передачу непосредственно с пинов FPGA? При передачи данных наблюдались ли ошибки? Применяли ли Вы помехозащищенное кодирование например 8b/10b? -

почитайте я использую: VHDL for the “Mealy” machine example with two VHDL processes стр 12 FSM_design.pdf

-

uart.vuart_tb.vuart_hw_test.v посмотрите такую реализацию с 2-мя тестбенчами PS Под посмотреть я понимаю запустить симуляцию с разными тестбенчами, вывести с описаний реализации UART все сигналы на waveform и попробовать разобраться как работает. Далее попробовать например поменять скорость и опять посмотерть симуляцию... Здесь найдете некоторое объяснение/рекомендации по реализации UART https://github.com/Paebbels/PicoBlaze-Library/blob/master/documentation (Xilinx)/UART - 200 MHz UART with Internal 16-Byte Buffer [XAPP223][2008.04.24][v1.2].pdf

-

-

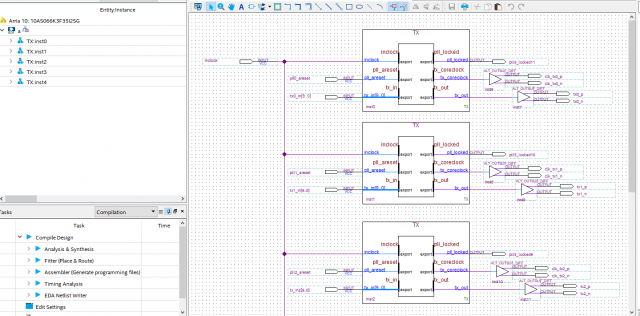

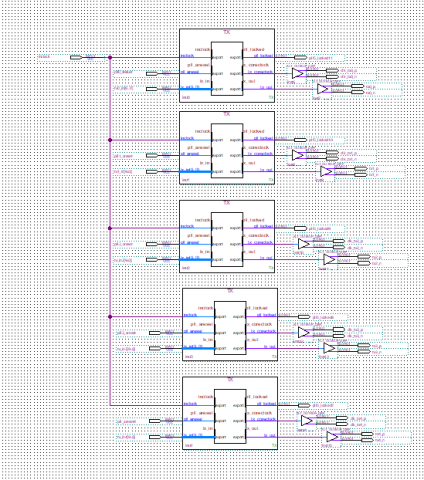

LVDS SERDES

Maverick_ опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день Сделал проект в котором использую корку LVDS SERDES Intel (5 штук). На этапе fitter мне выдается ошибка Error (16234): No legal location could be found out of 36 considered location(s). Reasons why each location could not be used are summarized below: Error (18515): Attempted to route one dedicated refclk pin, inclock, to 5 IOPLLs. In order to feed multiple IOPLLs, this signal must be promoted to a global clock. (30 locations affected) Info (175029): B15 Info (175029): A15 Info (175029): E12 Info (175029): E11 Info (175029): AH18 Info (175029): AG18 Info (175029): AK23 Info (175029): AL23 Info (175029): AF14 Info (175029): AG15 Info (175029): AL10 Info (175029): AM10 Info (175029): and 18 more locations not displayed Error (18515): Attempted to route one dedicated refclk pin, inclock, to 5 IOPLLs. In order to feed multiple IOPLLs, this signal must be promoted to a global clock. (4 locations affected) Info (175029): H18 Info (175029): G18 Info (175029): D19 Info (175029): C19 Поиск ошибки по интернет привел к https://www.intel.com/content/www/us/en/support/programmable/articles/000074176.html С одной коркой проблем нет. Ниже скриншоты проекта Чтобы выполнить set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to xxx мне во внутрь корок смотреть(RTL viewer), чтобы увидеть сигналы? или я не прав? Возможно кто-то может сгенерировать проект - этот проект может решить проблему за счет внешнего pll https://www.intel.com/content/www/us/en/docs/programmable/683520/22-1-20-0-1/combined-ip-transmitter-and-receiver.html -

спасибо большое

-

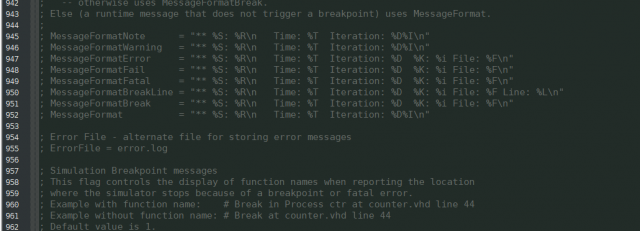

можешь своим modelsim.ini поделиться? пожалуйста Получается что если я уберу Time: %T Iteration: %D%I\n то не будет выводиться?

-

Modelsim (вывод в окно Transcript)

Maverick_ опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день Подскажите пожалуйста можно ли как то сделать ограничение на вывод в окно Transcript Для отладки я использую вставки в описании ------ for simulution ------------------------------------------------------------------------------------------- -- synthesis translate_off process (all) begin IF (CLK'EVENT AND CLK = '1') THEN --if reg_same_ready = '1' then if (reg_same_ready = '1') or (reg_same_ready_down = '1') or (reg_ready = '1') then report "Find data in the table IP_mask" severity note; report "index =: " & to_string(to_integer(unsigned(reg_index))) severity note; end if; end if; end process; -- synthesis translate_on -- synthesis translate_off process (all) begin IF (CLK'EVENT AND CLK = '1') THEN --if reg_same_ready = '1' then if (reg_error = '1') then report "Not find data in the table IP_mask" severity note; end if; end if; end process; -- synthesis translate_on у меня в окно Transcript Modelsim выводятся сообщения ** Note: Start new packet with IP_destination =: 82596CC9 # Time: 1920 ns Iteration: 1 Instance: /top_vhd_tst/i1/monitor_ip_header_inst # ** Note: Find data in the table IP_mask # Time: 1960 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 0 # Time: 1960 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find data in the table IP_mask # Time: 1970 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 15 # Time: 1970 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find data in the table IP_mask # Time: 2010 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 16 # Time: 2010 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find data in the table IP_mask # Time: 2050 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 17 # Time: 2050 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find data in the table IP_mask # Time: 2140 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 14 # Time: 2140 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find data in the table IP_mask # Time: 2180 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: index =: 13 # Time: 2180 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/core_binary_search_inst # ** Note: Find work channel # Time: 2330 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/search_work_channel_inst # ** Note: for index is work channel =: 16 # Time: 2330 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/search_work_channel_inst # ** Note: Find work channel # Time: 2430 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/search_work_channel_inst # ** Note: for index is work channel =: 14 # Time: 2430 ns Iteration: 1 Instance: /top_vhd_tst/i1/binary_search_inst/search_work_channel_inst Можно ли как то запретить вывод # Time: * ns Iteration: 1 * если да подскажите пожалуйста как это сделать ??? PS Просто эти строки затрудняют чтение выводимой мною информации -

передача по LVDS на плате

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

добрый день Подскажите пожалуйста с плис(Сyclone10gx) без использования внешних микросхем передача данных на плате на расстояние до 80 см по LVDS на 250МГц с клоком без потерь данных? -

my_work_loopback.zip в uart.vhd entity UART is Generic ( CLK_FREQ : integer := 50e6; -- system clock frequency in Hz BAUD_RATE : integer := 115200; -- baud rate value PARITY_BIT : string := "none"; -- type of parity: "none", "even", "odd", "mark", "space" USE_DEBOUNCER : boolean := True -- enable/disable debouncer ); пропишите свою тактовую частоту и другие параметры UART...

-

Деление не самая приятная математика для плис. Главный вопрос необходимо ли это делать на плис... Возможно по другому рассмотреть время - ниже описание таймера. Модуль system_timer.v представляет собой многоступенчатый счетчик модуля, который сообщает об истекшем рабочем времени. Выходные данные сообщают о днях, часах, минутах, секундах, миллисекундах и микросекундах. Он обнуляется через 1024 дня. Импульсные выходы могут быть удобно для периодических обновлений в системах управления. Данные от таймера передавать процессору... module system_timer ( input clk,rst, output reg [9:0] usecond_cntr, output reg [9:0] msecond_cntr, output reg [5:0] second_cntr, output reg [5:0] minute_cntr, output reg [4:0] hour_cntr, output reg [9:0] day_cntr, output reg usecond_pulse, output reg msecond_pulse, output reg second_pulse ); parameter CLOCK_MHZ = 200; reg [7:0] tick_cntr; reg tick_cntr_max; // review tick counter design if leaving this range // initial assert (CLOCK_MHZ > 64 && CLOCK_MHZ < 250); always @(posedge clk) begin if (rst) begin tick_cntr <= 0; tick_cntr_max <= 0; end else begin if (tick_cntr_max) tick_cntr <= 1'b0; else tick_cntr <= tick_cntr + 1'b1; tick_cntr_max <= (tick_cntr == (CLOCK_MHZ - 2'd2)); end end ///////////////////////////////// // Count off 1000 us to form 1 ms ///////////////////////////////// reg usecond_cntr_max; always @(posedge clk) begin if (rst) begin usecond_cntr <= 0; usecond_cntr_max <= 0; end else if (tick_cntr_max) begin if (usecond_cntr_max) usecond_cntr <= 1'b0; else usecond_cntr <= usecond_cntr + 1'b1; usecond_cntr_max <= (usecond_cntr == 10'd998); end end ///////////////////////////////// // Count off 1000 ms to form 1 s ///////////////////////////////// reg msecond_cntr_max; always @(posedge clk) begin if (rst) begin msecond_cntr <= 0; msecond_cntr_max <= 0; end else if (usecond_cntr_max & tick_cntr_max) begin if (msecond_cntr_max) msecond_cntr <= 1'b0; else msecond_cntr <= msecond_cntr + 1'b1; msecond_cntr_max <= (msecond_cntr == 10'd998); end end ///////////////////////////////// // Count off 60s to form 1 m ///////////////////////////////// reg second_cntr_max; always @(posedge clk) begin if (rst) begin second_cntr <= 0; second_cntr_max <= 0; end else if (msecond_cntr_max & usecond_cntr_max & tick_cntr_max) begin if (second_cntr_max) second_cntr <= 1'b0; else second_cntr <= second_cntr + 1'b1; second_cntr_max <= (second_cntr == 6'd58); end end ///////////////////////////////// // Count off 60m to form 1hr ///////////////////////////////// reg minute_cntr_max; always @(posedge clk) begin if (rst) begin minute_cntr <= 0; minute_cntr_max <= 0; end else if (second_cntr_max & msecond_cntr_max & usecond_cntr_max & tick_cntr_max) begin if (minute_cntr_max) minute_cntr <= 1'b0; else minute_cntr <= minute_cntr + 1'b1; minute_cntr_max <= (minute_cntr == 6'd58); end end ///////////////////////////////// // Count off 24h to form 1day ///////////////////////////////// reg hour_cntr_max; always @(posedge clk) begin if (rst) begin hour_cntr <= 0; hour_cntr_max <= 0; end else if (minute_cntr_max & second_cntr_max & msecond_cntr_max & usecond_cntr_max & tick_cntr_max) begin if (hour_cntr_max) hour_cntr <= 1'b0; else hour_cntr <= hour_cntr + 1'b1; hour_cntr_max <= (hour_cntr == 5'd22); end end ///////////////////////////////// // Count off 1024 days then wrap ///////////////////////////////// always @(posedge clk) begin if (rst) begin day_cntr <= 0; end else if (hour_cntr_max & minute_cntr_max & second_cntr_max & msecond_cntr_max & usecond_cntr_max & tick_cntr_max) begin day_cntr <= day_cntr + 1'b1; end end ///////////////////////////////////// // Filtered output pulses ///////////////////////////////////// always @(posedge clk) begin if (rst) begin usecond_pulse <= 1'b0; msecond_pulse <= 1'b0; second_pulse <= 1'b0; end else begin usecond_pulse <= tick_cntr_max; msecond_pulse <= tick_cntr_max & usecond_cntr_max; second_pulse <= tick_cntr_max & msecond_cntr_max & usecond_cntr_max; end end endmodule

-

Кто-то с ней работал? работает без проблем?

-

Это плохое суждение/призыв...

-

Значит будет отдельный процесс/always с компараторами где будет сравнение с этими магическими числами...

-

Сигнал ресет

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

Я знаю ))) -

Сигнал ресет

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

также как и я )))