-

Постов

3 861 -

Зарегистрирован

Весь контент Maverick_

-

организация семплирования

Maverick_ ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

поясните подробнее почему? -

организация семплирования

Maverick_ ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

хороший вопрос) -

организация семплирования

Maverick_ ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

теперь понял -

организация семплирования

Maverick_ ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

Спасибо, ето понятно для меня Мне не понятен момент частоти генерации псп сигнала (красная стрелка) - етот момент поясните плиз Т.е я могу генерить псп на любой частоте семплирования? не важно что в реалии она 1,023МГц? -

организация семплирования

Maverick_ ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

Всем спасибо за ответ Просто генерировать последовательность (C/A code generator) на 5.714 MHz sampling frequency? (красная стрелка) или генерировать псп на 1,023МГц просто ее так сказать семплировать на 5.714 MHz? как правильно? поясните пожалуйста почему "весьма говенный приемник"? кроме более високой частоти, еще какие аргументи? -

организация семплирования

Maverick_ опубликовал тема в Алгоритмы ЦОС (DSP)

Привет Есть блок схема: Есть псевдослуайний генератор (C/A code generator) работающий на частоте 1,023МГц но как я понимаю частота семплирования должна производиться на частоте 5,714МГц Как правильно такое организовать? Подскажите пожалуйста. Просто генерировать последовательность (C/A code generator) на 5.714 MHz sampling frequency? Затем ее фильровать как на блок схеме? -

Для чего? используйте просто data_in : in std_logic_vector(DATA_SIZE-1 downto 0); внутри модуля преобразуйте в unsigned/signed reg_data <= unsigned(data_in ); Далее работайте с типом unsigned (например) - все дальнейшие вічисления с безнаковими числами

-

Cпасибо quato_a

-

калибровку задержек TX/RX трактов между ПЛИС и трансивером как делали (если плата с трансивером своей разработки)?

-

quato_a Меня интересует программа для инициализации ad9361, которая поможет с ее инициализацией Часть для FPGA - сделана. Снифером считал у SDR радио на основе ad9361, то там оказалось более 4000 команд передается для инициализации...

-

конфигурируем микросхему ad9361

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго дня Насколько я понимаю есть ПО помогающее сконфигурировать микросхему ad9361 сужу по ресурсам: https://ez.analog.com/wide-band-rf-transceivers/design-support/f/q-a/79163/ad9361-configuration-software AD936X Advanced Plugin [Analog Devices Wiki] вот у китайцев https://blog.csdn.net/qq_37989552/article/details/124381604 подскажите где можно скачать? Может кто-то может поделиться? меня интересует паралельнй CMOS для RX/TX не LVDS у ad9361 PS Ответ можно в личку -

Помощь с core atan

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день Пожалуйста разобраться с коркой вычисления atan Нашел корку - запустил симуляцию (в атаче архив), но не пойму как по выходам определить угол. Аналогичную корку нащел здесь на форуме Помогите понять как понимать данные выдаваемые коркой и переводить в угол PS Времени нет сесть разорбраться сейчас, но обязательно это сделаю позже... atan.7z -

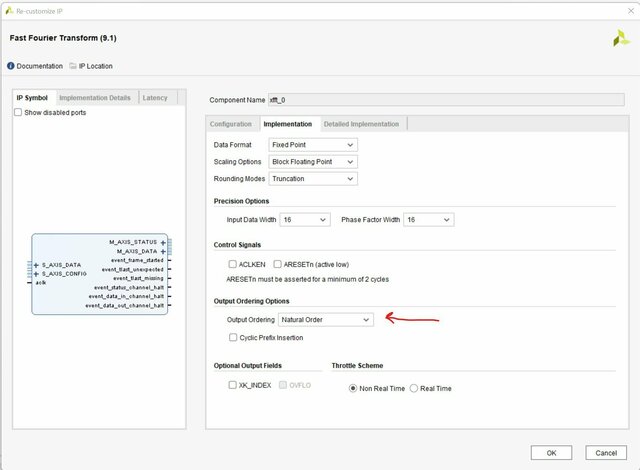

fft vivado 2019.1

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

-

fft vivado 2019.1

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день Начал работать с коркой fft ver 9.1 Создал к корке обвязку - в виде генератора синуса и косинуса из памяти со стриминг интерфейсом для выдачи данных на корку fft Данные для корки fft : Младшие 16 бит - значения синуса Старшие 16 бит - значения косинуса Выход корки соеденил со входом второй коркой fft сконфигурипрванную на обратное преобразование. С матлабом ничего не сошлось. Конфигурацию по стриминг интерфкйсу делаю. Где подводные камни/нюансы могут быть при работе с коркой fft ver 9.1? -

Мой совет идти на курсы лучше с каким то багажом знаний - иначе будет сложно сразу все освоить.... Так у Вас будут вопросы которые сможете там спросить... Лучше всего начать с работы в ModelSim/QuestaSim писать и проверять... Для проверки понимания синтезатором вібрать например Quartus - он проще для понимания чем Vivado (мое мнение) На форуме задавайте вопросы - здесь есть очень хорошие специалисты - они помогут... Во вложении пару книг которые могут помочь... SystemVerilog for Verification.pdf Systemverilog For Design.pdf

-

Может сделать 2 процессора и каждый с одним Ethernet? 2 потока и 2 обработчика...

-

что делать со случаем "в нескольких местах используется этот одинаково называнный LPM_DIVIDE, но в одной части он должен быть одной версии, а в другой - соответственно другой версии библиотеки." как исправить?

-

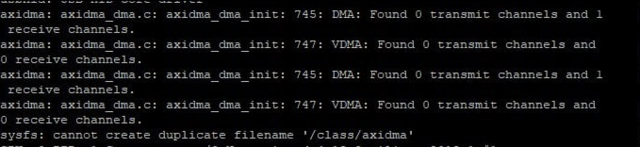

linux 2 устройства

Maverick_ опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый! Вопрос по поводу DMA: в части логики объявлены 2 устройства AXI DMA, device tree файл обновлен и содержит описание модулей. При запуске видно, что отрабатывает создание только одного устройства (оно потом появляется в /dev). Конфликт связан с тем, что там одно имя на 2 устройства в драйвере. Можно ли как-то обойти эту ситуацию? Лог ошибки axidma: axidma_dma.c: axidma_dma_init: 745: DMA: Found 0 transmit channels and 1 receive channels. axidma: axidma_dma.c: axidma_dma_init: 747: VDMA: Found 0 transmit channels and 0 receive channels. axidma: axidma_dma.c: axidma_dma_init: 745: DMA: Found 0 transmit channels and 1 receive channels. axidma: axidma_dma.c: axidma_dma_init: 747: VDMA: Found 0 transmit channels and 0 receive channels. sysfs: cannot create duplicate filename '/class/axidma' CPU: 1 PID: 1 Comm: swapper/0 Not tainted 4.19.0-xilinx-v2019.1 #1 Hardware name: Xilinx Zynq Platform [<c010f18c>] (unwind_backtrace) from [<c010af0c>] (show_stack+0x10/0x14) [<c010af0c>] (show_stack) from [<c06949ac>] (dump_stack+0x80/0xa0) [<c06949ac>] (dump_stack) from [<c0243e00>] (sysfs_warn_dup+0x4c/0x64) [<c0243e00>] (sysfs_warn_dup) from [<c0243ef8>] (sysfs_create_dir_ns+0xa0/0xc8) [<c0243ef8>] (sysfs_create_dir_ns) from [<c0698c40>] (kobject_add_internal+0xb0/ 0x1f4) [<c0698c40>] (kobject_add_internal) from [<c0698e30>] (kset_register+0x20/0x3c) [<c0698e30>] (kset_register) from [<c03e96e4>] (__class_register+0xbc/0x130) [<c03e96e4>] (__class_register) from [<c03e9798>] (__class_create+0x40/0x70) [<c03e9798>] (__class_create) from [<c054ff2c>] (axidma_chrdev_init+0x54/0x15c) [<c054ff2c>] (axidma_chrdev_init) from [<c054ecb4>] (axidma_probe+0xf0/0x14c) [<c054ecb4>] (axidma_probe) from [<c03ea2e4>] (platform_drv_probe+0x48/0x94) [<c03ea2e4>] (platform_drv_probe) from [<c03e88fc>] (really_probe+0x1bc/0x280) [<c03e88fc>] (really_probe) from [<c03e8c48>] (driver_probe_device+0x140/0x158) [<c03e8c48>] (driver_probe_device) from [<c03e8cec>] (__driver_attach+0x8c/0xc8) [<c03e8cec>] (__driver_attach) from [<c03e6f74>] (bus_for_each_dev+0x64/0xa0) [<c03e6f74>] (bus_for_each_dev) from [<c03e7f00>] (bus_add_driver+0x16c/0x1d4) [<c03e7f00>] (bus_add_driver) from [<c03e94f4>] (driver_register+0xac/0xf0) [<c03e94f4>] (driver_register) from [<c0102670>] (do_one_initcall+0x70/0x140) [<c0102670>] (do_one_initcall) from [<c0900e1c>] (kernel_init_freeable+0x18c/0x1 d0) [<c0900e1c>] (kernel_init_freeable) from [<c06a5d80>] (kernel_init+0x8/0x10c) [<c06a5d80>] (kernel_init) from [<c01010e8>] (ret_from_fork+0x14/0x2c) Exception stack(0xef063fb0 to 0xef063ff8) 3fa0: 00000000 00000000 00000000 00000000 3fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 3fe0: 00000000 00000000 00000000 00000000 00000013 00000000 kobject_add_internal failed for axidma with -EEXIST, don't try to register thing s with the same name in the same directory. axidma: axidma_chrdev.c: axidma_chrdev_init: 584: Unable to create a device clas s. axidma: probe of amba_pl:axidma_chrdev@1 failed with error -38 -

сделать pipeline нельзя? разбить на 2-3 такта и добавить сигнал готовности для чего это если не секрет?

-

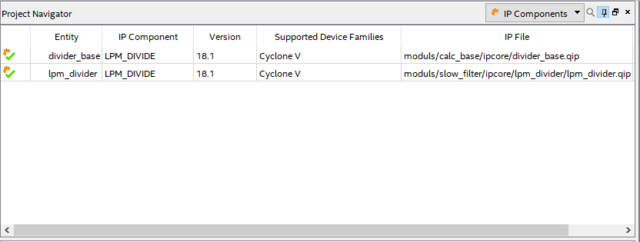

Убрал один модуль деления из проекта - моделсим компилирует... продолжу исследования))) PS где-то лажа... квартус <=> моделсим

-

У меня в проекте два делителя используется с разными параметрами для синтеза. Неужели я не могу более одного компонента использовать в проекте - бред какой то в первом описаном случае я не использую оптимизацию вообще - c.do файл. Оптимизацию добавляет native link (из квартуса) - prj_elvatech_run_msim_rtl_vhdl.do Как мне переделать проект чтобы не было повторов имен IP CORE LPM_DIVIDE? Cейчас ругается на имя divider_base которое дал визарду при создании IP CORE Но divider_base (см вложение первого поста) это обвертка в которой прописан LPM_DIVIDE с параметрами настроек. Аналогично и с lpm_divider Помниться я вначале 2000 годов (вначале своей карьеры) я моделировал схемы из схематик едитора - там то повторов IP CORE было множество... Что то получается я делаю не правильно, понять бы что и где

-

проблема с симуляцией

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый! Пытаюсь сделать симуляцию с библиотечными элементами (квартус 18.1). Написал do файл (вложение). Моделсим выдает странные ошибки: # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(66): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_drepresentation. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(67): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_hint. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(68): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_nrepresentation. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(69): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_pipeline. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(70): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_type. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(71): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_widthd. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # ** Error (suppressible): (vsim-10000) ./moduls/calc_base/ipcore/divider_base.v(72): Unresolved defparam reference to 'LPM_DIVIDE_component' in LPM_DIVIDE_component.lpm_widthn. # Time: 0 ps Iteration: 0 Instance: /dpp_vhd_tst/i1/b2v_inst8/divider_base_inst File: ./moduls/calc_base/ipcore/divider_base.v # Error loading design # Error: Error loading design # Pausing macro execution # MACRO ./c.do PAUSED at line 69 Ошибки в модуле который визард генерирует - на его параметры. alg_base_calc_1calc.v - модуль в который делитель (divider_base.v) входит как компонент c.do - произвожу запуск симуляции в моделсиме Пошел альтернативным путем: Пытался запустить симуляцию через native link (из квартуса): prj_elvatech_run_msim_rtl_vhdl.do - файл созданный квартусом для симуляции ошибки аналогичные: # vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cyclonev -L rtl_work -L work -voptargs="+acc" dpp_vhd_tst # vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cyclonev -L rtl_work -L work -voptargs=""+acc"" dpp_vhd_tst # Start time: 19:33:40 on Nov 15,2022 # ** Note: (vsim-3812) Design is being optimized... # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(66): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(67): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(68): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(69): Invalid reference 'lpm_pipeline' in defparam; target resolves below VHDL scope 'LPM_DIVIDE_component'. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(69): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(70): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(71): Invalid reference 'lpm_widthd' in defparam; target resolves below VHDL scope 'LPM_DIVIDE_component'. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(71): Illegal target for defparam. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(72): Invalid reference 'lpm_widthn' in defparam; target resolves below VHDL scope 'LPM_DIVIDE_component'. # ** Error: D:/hdl_projects/Elvatech/prj_elvatech/moduls/calc_base/ipcore/divider_base.v(72): Illegal target for defparam. # Optimization failed # Error loading design # Error: Error loading design # Pausing macro execution # MACRO ./prj_elvatech_run_msim_rtl_vhdl.do PAUSED at line 59 Подскажите пожалуйста как исправить ошибки в моделсиме? divider_base_inst.v divider_base.qip divider_base.v divider_base_bb.v alg_base_calc_1calc.v c.do prj_elvatech_run_msim_rtl_vhdl.do -

проблема была в том что в do файле я случайно для верилог файла написал команду для vhdl файла было vcom -2008 -work work {./moduls/calc_base/alg_base_calc_1calc.v} надо: vlog -work work {./moduls/calc_base/alg_base_calc_1calc.v} на скрине ошибки это видно)))

-

не увидел, спасибо))

-

Добрый! Помогите пожалуйста исправить ошибку в моделсиме, квартус компилирует без проблем Ошибка; Файл во вложении PS уже жаже переписал на английской клавиатуре всю первую строку - думал что кирилица где-то есть Хотя бы мысли, где копать подскажите пожалуйста alg_base_calc_1calc.v