-

Постов

3 865 -

Зарегистрирован

Весь контент Maverick_

-

Дополню задачу - внесу более четкость Выход каждого модуля это порт памяти с которого необходимо прочитать результат обработки после ready = '1' Давайте пока считать что только 1 ready = '1' может быть Предыдущий пост дополнил для ясности задачи

-

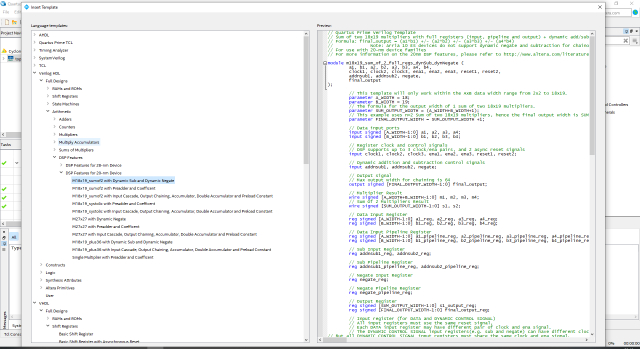

des00 спасибо за подсказку... Добрый день. (update) есть несколько индентичных модулей (размножены с помощью generic). Модуль выдает ready как данные готовы. Все модули ready выдать одновремнно не могут - только один срабатывет Выход каждого модуля это порт памяти с которого необходимо прочитать результат обработки после ready = '1'. Вопрос как мне определить с какого модуля мне надо забрать данные и как построить мультиплексор к портам памяти (возможно есть другие красивые решения). Мое решение сложное - как по мне: ниже ход мыслей Объеденяем все ready от модулей в один регистр, далее module bitscan (req,sel); parameter WIDTH = 16; input [WIDTH-1:0] req; output [WIDTH-1:0] sel; assign sel = req & ~(req-1); endmodule (что делает этот модуль во вложении картинка) от результата отнимаем 1 и считаем количество едениц ответом и будет номер модуля с какого модуля мне надо забрать данные в котором сработал ready Потом мультиплексор ... library ieee ; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity mux4 is port( d0 : in std_logic_vector(1 downto 0); d1 : in std_logic_vector(1 downto 0); d2 : in std_logic_vector(1 downto 0); d3 : in std_logic_vector(1 downto 0); s : in std_logic_vector(1 downto 0); m : out std_logic_vector(1 downto 0)); end mux4; architecture rtl of mux4 is type t_array_mux is array (0 to 3) of std_logic_vector(1 downto 0); signal array_mux : t_array_mux; begin array_mux(0) <= d0; array_mux(1) <= d1; array_mux(2) <= d2; array_mux(3) <= d3; m <= array_mux(to_integer(unsigned(s))); end rtl; Для шины адреса и данных - необходимых для чтения из памяти (BRAM) Интересуют идеи по реализации.

-

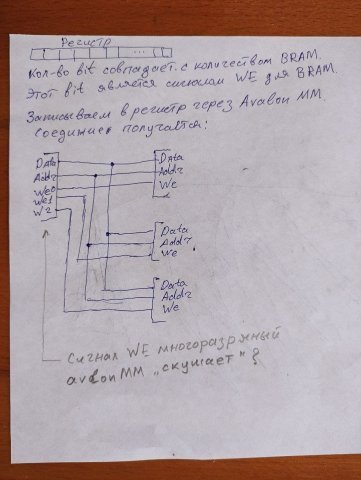

Насчет возможности с помощью Core Generator я знаю... Начал сомневаться что описать память с Chip select можно - только через Core Generator Вот еще архитектура для записи - вложение

-

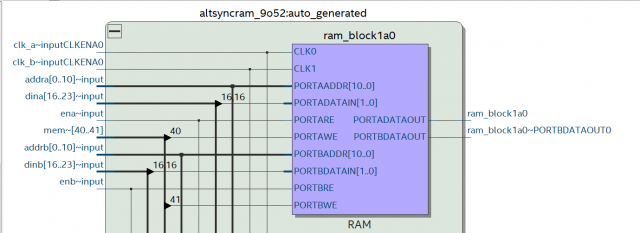

описание двухпортовой памяти с CS

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день подскажите пожалуйста как правильно описать двухпортовую память с CS(Chip select) (altera) такое решение library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity bram_tdp is generic ( DATA : integer := 32; ADDR : integer := 12 ); port ( -- Port A a_clk : in std_logic; ena : in std_logic;-- a_wr : in std_logic; a_addr : in std_logic_vector(ADDR-1 downto 0); a_din : in std_logic_vector(DATA-1 downto 0); a_dout : out std_logic_vector(DATA-1 downto 0); -- Port B b_clk : in std_logic; enb : in std_logic;-- b_wr : in std_logic; b_addr : in std_logic_vector(ADDR-1 downto 0); b_din : in std_logic_vector(DATA-1 downto 0); b_dout : out std_logic_vector(DATA-1 downto 0) ); end bram_tdp; architecture rtl of bram_tdp is -- Shared memory type mem_type is array ( (2**ADDR)-1 downto 0 ) of std_logic_vector(DATA-1 downto 0); FUNCTION initialize_ram return mem_type is variable result : mem_type; BEGIN FOR i IN ((2**ADDR)-1) DOWNTO 0 LOOP result(i) := std_logic_vector( to_unsigned(natural(i), natural'((DATA)))); END LOOP; RETURN result; END initialize_ram; shared variable mem : mem_type := initialize_ram; --shared variable mem : mem_type := (others => (others => '0')); -- := initialize_ram; begin -- Port A process(a_clk) begin if(a_clk'event and a_clk='1') then if ena = '1' then -- if(a_wr='1') then mem(conv_integer(a_addr)) := a_din; end if; a_dout <= mem(conv_integer(a_addr)); end if; -- end if; end process; -- Port B process(b_clk) begin if(b_clk'event and b_clk='1') then if enb = '1' then -- if(b_wr='1') then mem(conv_integer(b_addr)) := b_din; end if; b_dout <= mem(conv_integer(b_addr)); end if; -- end if; end process; end rtl; мне кажется не коректным т.к. не задействуется порт CS (technology viewer) - вложение. Основной вопрос как осуществить доступ к нескольким портам памяти (BRAM) имея один вход: Шина данных Шина адреса Сигнал WE Решение через сигнал WE мне кажется не очень быстродейственным - большой mux. Мне надо соедениться с 16 памятями - чтобы их инициализировать Можно конечно сделать pipeline. Может у кого есть более оригинальные решения? PS Для avalon MM для соединения мастера со многими слейвами MM - все намного проще "Chip select signal to the slave. The slave port should ignore all other Avalon signal inputs unless chipselect is asserted." -

я бы на счетчике это сделал

-

Помощь с скачиванием xapp от Xilinx

Maverick_ ответил Maverick_ тема в Документация

спасибо -

Помощь с скачиванием xapp от Xilinx

Maverick_ ответил Maverick_ тема в Документация

прошу помощи скачать zip архив исходников для https://www.xilinx.com/support/documentation/application_notes/xapp1151_Param_CAM.pdf Заранее благодарен -

как можно так выпускать продукт? где банальное тестирование ПО? PS я в шоке

-

-

-- Measure the pulse length library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity pulse_len_measure is generic ( N : integer:=8); port ( i_clk : in std_logic; i_rstb : in std_logic; i_input : in std_logic; o_pulse_len_hi : out std_logic_vector(N-1 downto 0); o_pulse_len_lo : out std_logic_vector(N-1 downto 0)); end pulse_len_measure; architecture rtl of pulse_len_measure is constant C_MAX_COUNT : unsigned(N-1 downto 0):=(others=>'1'); signal r_count_hi_ena : std_logic; signal r_count_hi : unsigned(N-1 downto 0); signal r_count_lo : unsigned(N-1 downto 0); signal r_count_lo_ena : std_logic; signal r_rise : std_logic; signal r_fall : std_logic; signal p_input : std_logic_vector(0 to 2); -- input pipe begin p_edge_detector : process(i_clk,i_rstb) begin if(i_rstb='0') then r_rise <= '0'; r_fall <= '0'; p_input <= (others=>'0'); elsif(rising_edge(i_clk)) then r_rise <= not p_input(2) and p_input(1); r_fall <= not p_input(1) and p_input(2); p_input <= i_input&p_input(0 to p_input'length-2); end if; end process p_edge_detector; p_count_hi : process(i_clk,i_rstb) begin if(i_rstb='0') then r_count_hi_ena <= '0'; r_count_hi <= to_unsigned(1,N); o_pulse_len_hi <= (others=>'0'); elsif(rising_edge(i_clk)) then if(r_rise='1') then r_count_hi_ena <= '1'; elsif(r_fall='1') then r_count_hi_ena <= '0'; o_pulse_len_hi <= std_logic_vector(r_count_hi); end if; if(r_count_hi_ena='1') then if(r_count_hi<C_MAX_COUNT)then r_count_hi <= r_count_hi + 1; end if; else r_count_hi <= to_unsigned(1,N); end if; end if; end process p_count_hi; p_count_lo : process(i_clk,i_rstb) begin if(i_rstb='0') then r_count_lo_ena <= '0'; r_count_lo <= to_unsigned(1,N); o_pulse_len_lo <= (others=>'0'); elsif(rising_edge(i_clk)) then if(r_fall='1') then r_count_lo_ena <= '1'; elsif(r_rise='1') then r_count_lo_ena <= '0'; o_pulse_len_lo <= std_logic_vector(r_count_lo); end if; if(r_count_lo_ena='1') then if(r_count_lo<C_MAX_COUNT) then r_count_lo <= r_count_lo + 1; end if; else r_count_lo <= to_unsigned(1,N); end if; end if; end process p_count_lo; end rtl; как тут правильно писал Nick_K лучше это делать с помощью PLL но так как Вы новичок в FPGA то попробуйте вначале менее точное измерение и проверьте в работе, а потом уже поменяете... ниже пример с применением PLL: пример (здесь еще есть нюансы - поддержка платы этого варианта)

-

например

-

Попробуйте записать - читать с BRAM, если все норм то можно фифо самому описать... или взять готовое описание...

-

Еще добавлю описывать логику работы в FPGA на порядок сложнее чем писать ПО для микропроцессоров. Также необходимо учитывать, что время разработки для FPGA дольше, особенно если нет опыта. Для старта посмотрите платы до 500$ например на базе Zynq (логика + ARM A9) - попробуйте там свои первые шаги. И то проверки на плате можно делать только после моделирования и никак не наоборот. Когда пройдете так сказать путь "молодого бойца" у Вас появиться осознанное понимание выбора FPGA для конкретной задачи...

-

testbench (vhdl)

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Flip-fl0p и vt313 спасибо, возьму на заметку -

testbench (vhdl)

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Спасибо за помощь Вроде работает сделал следующим образом LIBRARY ieee; USE ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.math_real.all; use std.textio.all; ..... -- convert an unsigned value(4 bit) to a HEX digit (0-F) function to_HexChar(Value : UNSIGNED) return CHARACTER is constant HEX : STRING := "0123456789ABCDEF"; begin if (Value < 16) then return HEX(to_integer(Value)+1); else return 'X'; end if; end function; -- return TRUE, if input is a power of 2 function div_ceil(a : NATURAL; b : POSITIVE) return NATURAL is -- calculates: ceil(a / b) begin return (a + (b - 1)) / b; end function; -- return log2; always rounded up function log2ceil(arg : positive) return natural is variable tmp : positive; variable log : natural; begin if arg = 1 then return 0; end if; tmp := 1; log := 0; while arg > tmp loop tmp := tmp * 2; log := log + 1; end loop; return log; end function; -- format a std_logic_vector as HEX string function raw_format_slv_hex(slv : STD_LOGIC_VECTOR) return STRING is variable Value : STD_LOGIC_VECTOR(4*div_ceil(slv'length, 4) - 1 downto 0); variable Digit : STD_LOGIC_VECTOR(3 downto 0); variable Result : STRING(1 to div_ceil(slv'length, 4)); variable j : NATURAL; begin Value := STD_LOGIC_VECTOR (resize(unsigned(slv), Value'length)); j := 0; for i in Result'reverse_range loop Digit := Value((j * 4) + 3 downto (j * 4)); Result(i) := to_HexChar(unsigned(Digit)); j := j + 1; end loop; return Result; end function; и сам процесс write_to_file0: process(all) variable outdata_line: line; variable outdata : STRING(1 to 32); file output_data_file: text open write_mode is "huffman_bitsream_final_out.txt"; begin if rising_edge(clk) then if huffman_bitsream_final_out.valid = '1' then outdata := raw_format_slv_hex( STD_LOGIC_VECTOR (huffman_bitsream_final_out.bitstream)); write(outdata_line,outdata); writeline(output_data_file,outdata_line); end if; end if; end process; -

testbench (vhdl)

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

вот другая функция function hex (lvec: in std_logic_vector) return string is variable text: string(lvec'length / 4 - 1 downto 0) := (others => '9'); subtype halfbyte is std_logic_vector(4-1 downto 0); begin assert lvec'length mod 4 = 0 report "hex() works only with vectors whose length is a multiple of 4" severity FAILURE; for k in text'range loop case halfbyte'(lvec(4 * k + 3 downto 4 * k)) is when "0000" => text(k) := '0'; when "0001" => text(k) := '1'; when "0010" => text(k) := '2'; when "0011" => text(k) := '3'; when "0100" => text(k) := '4'; when "0101" => text(k) := '5'; when "0110" => text(k) := '6'; when "0111" => text(k) := '7'; when "1000" => text(k) := '8'; when "1001" => text(k) := '9'; when "1010" => text(k) := 'A'; when "1011" => text(k) := 'B'; when "1100" => text(k) := 'C'; when "1101" => text(k) := 'D'; when "1110" => text(k) := 'E'; when "1111" => text(k) := 'F'; when others => text(k) := '!'; end case; end loop; return text; end function; все равно ошибка та же самая - записівать файл не хочет (vcom-1360) Array type of "outdata" does not have an index constraint. сам процесс стал write_to_file0: process(all) variable outdata_line: line; variable outdata : STRING; file output_data_file: text open write_mode is "bitsream_final_out.txt"; begin if rising_edge(clk) then if huffman_bitsream_final_out.valid = '1' then outdata := hex( STD_LOGIC_VECTOR (bitsream_final_out.bitstream)); write(outdata_line,outdata); writeline(output_data_file,outdata_line); end if; end if; end process; -

testbench (vhdl)

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день Есть результаты в виде 128 битных данных, мне их надо записать в файл в hex формате. Написал функции для этого ---------------------------------------------------------------------- -- convert an unsigned value(4 bit) to a HEX digit (0-F) function to_HexChar(Value : UNSIGNED) return CHARACTER is constant HEX : STRING := "0123456789ABCDEF"; begin if (Value < 16) then return HEX(to_integer(Value)+1); else return 'X'; end if; end function; -- return TRUE, if input is a power of 2 function div_ceil(a : NATURAL; b : POSITIVE) return NATURAL is -- calculates: ceil(a / b) begin return (a + (b - 1)) / b; end function; -- return log2; always rounded up function log2ceil(arg : positive) return natural is variable tmp : positive; variable log : natural; begin if arg = 1 then return 0; end if; tmp := 1; log := 0; while arg > tmp loop tmp := tmp * 2; log := log + 1; end loop; return log; end function; -- format a std_logic_vector as HEX string function raw_format_slv_hex(slv : STD_LOGIC_VECTOR) return STRING is variable Value : STD_LOGIC_VECTOR(4*div_ceil(slv'length, 4) - 1 downto 0); variable Digit : STD_LOGIC_VECTOR(3 downto 0); variable Result : STRING(1 to div_ceil(slv'length, 4)); variable j : NATURAL; begin Value := STD_LOGIC_VECTOR (resize(unsigned(slv), Value'length)); j := 0; for i in Result'reverse_range loop Digit := Value((j * 4) + 3 downto (j * 4)); Result(i) := to_HexChar(unsigned(Digit)); j := j + 1; end loop; return Result; end function; но моделсим ругается (vcom-1360) Array type of "outdata" does not have an index constraint. вот процесс LIBRARY ieee; USE ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.math_real.all; use std.textio.all; ....... write_to_file0: process(all) variable outdata_line: line; variable outdata : STRING; file output_data_file: text open write_mode is "final_out.txt"; begin if rising_edge(clk) then if huffman_bitsream_final_out.valid = '1' then outdata := raw_format_slv_hex( STD_LOGIC_VECTOR (bitsream_final_out.bitstream)); write(outdata_line,outdata); writeline(output_data_file,outdata_line); end if; end if; end process; Подскажите пожалуйста, что нужно сделать чтобы была заись в файл в hex формате? -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

Крутое решение имея fpga покупать логику на микросхемах. -

Добрый день Взможно ли работать с SFP модулем в плис с помощью Triple-Speed Ethernet ? (плис arria10) Кто то так пытался делать? PS догадываюсь что так возможно никто не делал и возможно это" изврат"

-

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

цитата понравилась... Всем: Прошу закачивать дебаты высказываться только по существу -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

Давайте по существу общаться -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

я уже подумываю перевести этот топик в В помощь начинающему -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

можно купить такую плату процессор, память и экран Совет: Начните с простого. Для начала берите готовую плату, дальше только разработка программного обеспечения -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

Посмотрите пожалуйста на плату которую я Вам посоветовал. Там хард процессор уже имеется (stm32) на мой взгляд излишен. Память к процессору подключена, а fpga может к ней обращаться через DMA. HDMI на борту платы имеется... PS не изобретайте себе трудности там где они не должны быть... -

Возможно ли?

Maverick_ ответил turnip тема в Работаем с ПЛИС, области применения, выбор

попробуйте посмотреть на эту плату https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=205&No=1046&PartNo=2 DMA поможет обращаться к памяти процессора... FPGA на плате топовая