-

Постов

3 864 -

Зарегистрирован

Весь контент Maverick_

-

возможно и больше судя

-

Посмотрите референс дизайн

-

https://support.xilinx.com/s/article/1651?language=en_US

-

работа с waveform vivado

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здраствуйте Подскажите может кто-то знает - у меня много модулей которые размножаются через for как вывести все модули на waveform vivado Думаю это как-то через tcl делается или какой-то другой метод передовой есть который я не знаю. сейчас пробую так # Открываем или создаем новую волновую форму open_waveform # Получаем список всех объектов сигналов set signals [get_wave_objects] # Проходим по всем модулям и добавляем их сигналы на волновую форму foreach module [get_cells] { # Получаем имя текущего модуля set module_name [get_property CELLNAME $module] # Добавляем все сигналы текущего модуля на волновую форму foreach signal $signals { if {[string match "*$module_name*" [get_property OBJECT_NAME $signal]]} { add_wave -divider "Module: $module_name" $signal } } } # Сохраняем текущую конфигурацию волновой формы в файл write_wave_config waves.wcfg # Отображаем волновую форму waveform пока работать не хочет PS может у кого-то есть проверенный скрипт для такого решения... -

Большое спасибо

-

спасибо, но у меня не откривается архив

-

архив xapp854

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

всем привет помогите найти/скачать архив для https://docs.xilinx.com/v/u/en-US/xapp854 -

посмотри Figure 3-1: The functional block diagram of the FPGA AD Testing я б делал по блок схеме

-

Lookup table синуса

Maverick_ ответил Kirill.L тема в Языки проектирования на ПЛИС (FPGA)

Мое описание не вариант? там автоматически генерируется второй вариант через матлаб скрипт - инициализируете память -

Lookup table синуса

Maverick_ ответил Kirill.L тема в Языки проектирования на ПЛИС (FPGA)

library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; use ieee.math_real.all; entity dds_sine is port( i_clk : in std_logic; i_rstb : in std_logic; i_sync_reset : in std_logic; i_fcw : in std_logic_vector(31 downto 0); i_start_phase : in std_logic_vector(31 downto 0); o_sine : out std_logic_vector(13 downto 0)); end dds_sine; architecture rtl of dds_sine is constant C_LUT_DEPTH : integer := 2**13; -- 8Kword constant C_LUT_BIT : integer := 14; -- 14 bit LUT type t_lut_sin is array(0 to C_LUT_DEPTH-1) of std_logic_vector(C_LUT_BIT-1 downto 0); -- quantize a real value as signed function quantization_sgn(nbit : integer; max_abs : real; dval : real) return std_logic_vector is variable temp : std_logic_vector(nbit-1 downto 0):=(others=>'0'); constant scale : real :=(2.0**(real(nbit-1)))/max_abs; constant minq : integer := -(2**(nbit-1)); constant maxq : integer := +(2**(nbit-1))-1; variable itemp : integer := 0; begin if(nbit>0) then if (dval>=0.0) then itemp := +(integer(+dval*scale+0.49)); else itemp := -(integer(-dval*scale+0.49)); end if; if(itemp<minq) then itemp := minq; end if; if(itemp>maxq) then itemp := maxq; end if; end if; temp := std_logic_vector(to_signed(itemp,nbit)); return temp; end quantization_sgn; -- generate the sine values for a LUT of depth "LUT_DEPTH" and quantization of "LUT_BIT" function init_lut_sin return t_lut_sin is variable ret : t_lut_sin:=(others=>(others=>'0')); -- LUT generated variable v_tstep : real:=0.0; variable v_qsine_sgn : std_logic_vector(C_LUT_BIT-1 downto 0):=(others=>'0'); constant step : real := 1.00/real(C_LUT_DEPTH); begin for count in 0 to C_LUT_DEPTH-1 loop v_qsine_sgn := quantization_sgn(C_LUT_BIT, 1.0,sin(MATH_2_PI*v_tstep)); ret(count) := v_qsine_sgn; v_tstep := v_tstep + step; end loop; return ret; end function init_lut_sin; -- initialize LUT with sine samples constant C_LUT_SIN : t_lut_sin := init_lut_sin; signal r_sync_reset : std_logic; signal r_start_phase : unsigned(31 downto 0); signal r_fcw : unsigned(31 downto 0); signal r_nco : unsigned(31 downto 0); signal lut_addr : std_logic_vector(12 downto 0); signal lut_value : std_logic_vector(13 downto 0); begin p_nco : process(i_clk,i_rstb) begin if(i_rstb='0') then r_sync_reset <= '1'; r_start_phase <= (others=>'0'); r_fcw <= (others=>'0'); r_nco <= (others=>'0'); elsif(rising_edge(i_clk)) then r_sync_reset <= i_sync_reset ; r_start_phase <= unsigned(i_start_phase); r_fcw <= unsigned(i_fcw); if(r_sync_reset='1') then r_nco <= r_start_phase; else r_nco <= r_nco + r_fcw; end if; end if; end process p_nco; p_rom : process(i_clk) begin if(rising_edge(i_clk)) then lut_addr <= std_logic_vector(r_nco(31 downto 19)); lut_value <= C_LUT_SIN(to_integer(unsigned(lut_addr))); end if; end process p_rom; p_sine : process(i_clk,i_rstb) begin if(i_rstb='0') then o_sine <= (others=>'0'); elsif(rising_edge(i_clk)) then o_sine <= lut_value; end if; end process p_sine; end rtl; у меня так сделано PS при симуляции не забудь сделать o_sine : out std_logic_vector(13 downto 0)); => signed иначе будете наблюдать в Analog представлении не синус -

Lookup table синуса

Maverick_ ответил Kirill.L тема в Языки проектирования на ПЛИС (FPGA)

Задавать начальную фазу как планируете в интеполяционной реализации? -

про тестбенч и почитайте про Finite state machines Без моделирования далеко не "уедите" при разработке на FPGA PS По ссылке я дал описание от производителя думаю оно рабочее и представленное описание формирует правильную циклограмму работы с микросхемой FT601.

-

мой Вам совет сделайте : Один буфер на прием другой на передачу. Проверьте на симуляции(через написание тестбенча), посмотрите RTL как Ваше описание понял синтезатор (наличие BRAM) Затем опишете работу двунаправленного порта через FSM например - таким образом получите управление буферами ниже описание двух портовой памяти - используйте как компонент - обратите внимание память двухклоковая, т.е. писать/читать можно на разных частотах (не забываем про CDC)... library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity bram_tdp is generic ( DATA : integer := 32; ADDR : integer := 12 ); port ( -- Port A a_clk : in std_logic; --ena : in std_logic; a_wr : in std_logic; a_addr : in std_logic_vector(ADDR-1 downto 0); a_din : in std_logic_vector(DATA-1 downto 0); a_dout : out std_logic_vector(DATA-1 downto 0); -- Port B b_clk : in std_logic; --enb : in std_logic; b_wr : in std_logic; b_addr : in std_logic_vector(ADDR-1 downto 0); b_din : in std_logic_vector(DATA-1 downto 0); b_dout : out std_logic_vector(DATA-1 downto 0) ); end bram_tdp; architecture rtl of bram_tdp is -- Shared memory type mem_type is array ( (2**ADDR)-1 downto 0 ) of std_logic_vector(DATA-1 downto 0); -- FUNCTION initialize_ram return mem_type is variable result : mem_type; -- variable v_TEMP : std_logic_vector(((DATA/2)-1) downto 0); -- BEGIN -- v_TEMP := (others => '1'); -- FOR i IN ((2**ADDR)-1) DOWNTO 0 LOOP -- result(i) := v_TEMP & std_logic_vector( to_unsigned(natural(i), natural'((DATA/2)))); -- END LOOP; -- RETURN result; -- END initialize_ram; FUNCTION initialize_ram return mem_type is variable result : mem_type; BEGIN FOR i IN ((2**ADDR)-1) DOWNTO 0 LOOP result(i) := std_logic_vector( to_unsigned(natural(i), natural'((DATA)))); END LOOP; RETURN result; END initialize_ram; shared variable mem : mem_type := initialize_ram; -- shared variable mem : mem_type := (others => (others => '0')); -- := initialize_ram; begin -- Port A process(a_clk) begin if(a_clk'event and a_clk='1') then -- if ena = '1' then if(a_wr='1') then mem(conv_integer(a_addr)) := a_din; end if; a_dout <= mem(conv_integer(a_addr)); -- end if; end if; end process; -- Port B process(b_clk) begin if(b_clk'event and b_clk='1') then --- if enb = '1' then if(b_wr='1') then mem(conv_integer(b_addr)) := b_din; end if; b_dout <= mem(conv_integer(b_addr)); -- end if; end if; end process; end rtl; описание двунаправленного порта - используйте как компонент -- -- The following represents the connectivity of the registered -- bi-directional I/O example -- ______ -- | | -- |-------|D | -- | | Q|-----input_signal -- | clock_|\ | -- ________________ | |/ | -- / top_level_port \______| |_____| -- \________________/ | -- | -- | /| -- |____/ |____________________ -- \ | _____ | -- _____ |\| | | | -- | | | out_sig-|D Q|----| -- output_enable_sig-|D Q|____| | |output_tmp_signal -- | | clock_|\ | -- clock_|\ | |/ | -- |/ | |_____| -- |_____| -- -- -- The following represents the connectivity of the unregistered -- bi-directional I/O example -- -- |----------input_signal -- | -- | -- ________________ | -- / top_level_port \______| -- \________________/ | -- | -- | /| -- |____/ |______output_signal -- \ | -- |\| -- | -- |---output_enable_signal library ieee; use ieee.std_logic_1164.all; entity top_bi_dir is port(T : in std_logic; I : in std_logic; O_NEW : out std_logic; IO : inout std_logic); end top_bi_dir; architecture archi of top_bi_dir is begin IO <= I when T = '0' else 'Z'; O_NEW <= IO; end archi; PS смотрели реализацию

-

мой совет опишите отдельным компонентом двупортовую память и сделайте логику записи и чтения в буффер. Я б на Вашем месте сделал бы две памяти одна на запись, другая чтение с/в inout порта. В данном Вашем описании Вы можете писать и читать одновременно потому что у Вас вход inout (можете сделать только вход и думаю все будет симулироваться). опишите корректно получение данных с inout порта. Управления переключения с чтения на запись и наоборот я в Вашем описании не вижу для буффера

-

замените fifo_buffer_src(test_cnt) <= std_ulogic_vector(to_unsigned( test_cnt, fifo_buffer_src(test_cnt)'length)); на fifo_buffer_src(test_cnt) <= std_logic_vector(to_unsigned( test_cnt, fifo_buffer_src(test_cnt)'length)); зачем вам тип std_ulogic_vector почему не использовать просто std_logic_vector ???

-

посмотрите алгоритм и его реализуйте пошагово. Там пример есть - добейтесь соответствия в симуляторе для начала для данного примера... Определитесь с архитектурой FSM или pipeline реализации.

-

добавьте клок напишите констрейн и посмотрите что дает тайминг анализ при больших количествах єлементов в массиве (16 и больше)?

-

скачать книгу

Maverick_ ответил Maverick_ тема в Документация

Помогите найти книгу https://www.amazon.com/Generalized-architecture-Modulation-Demodulation-Techniques/dp/3659339326 -

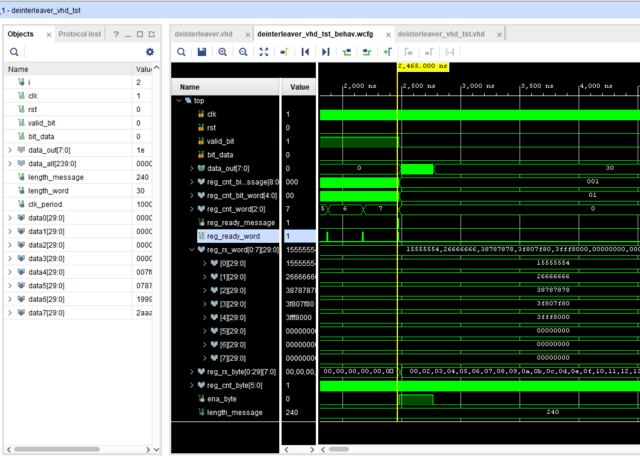

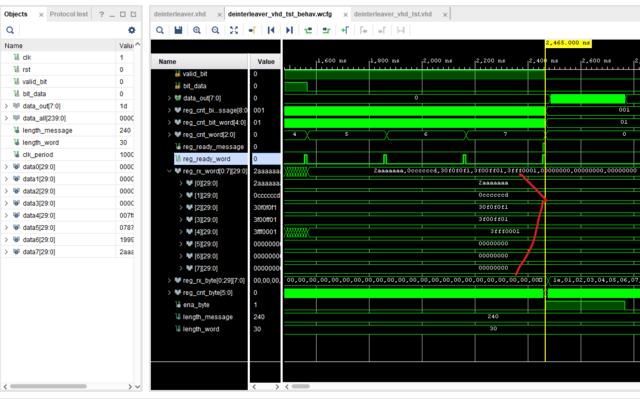

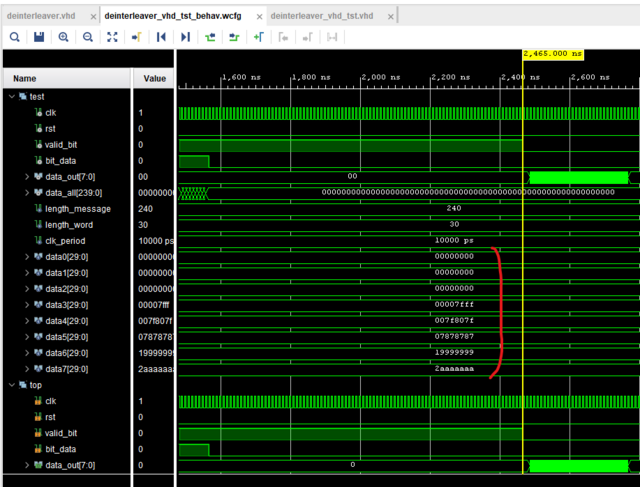

изменения каснулись в основном тестбенча и исправил ошибку в deinterleaver.vhd реверс бит надо было включить для єлементов массива reg_rx_word и все вроде совпадает, т.е. работает (в симулятор vivado реверс бит встроен) ---- reverse bit order ---------------------------------------------------------- function Reverse(constant X : in std_logic_vector) return std_logic_vector is alias alX : std_logic_vector(X'length - 1 downto 0) is X; variable Y : std_logic_vector(alX'range); begin for i in alX'range loop Y(i) := alX(alX'left - i); end loop; return Y; end; -- example work function: -- a = 01011111100110101; -- b = Reverse(a); -- b = 10101100111111010; --------------------------------------------------------------------------------- des00 спасибо за помощь deinterleaver.vhd deinterleaver_vhd_tst.vhd par2ser.vhd

-

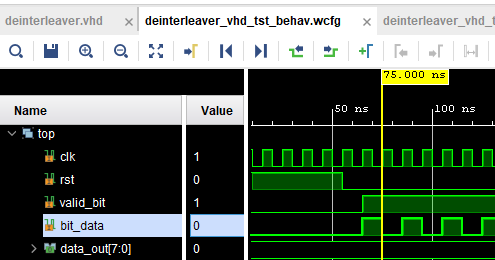

знаю, но время против меня работает... поспешишь людей насмешишь ... исправил в тестбенче на -- valid_bit <= '1'; valid_bit0: process begin valid_bit <= '0'; wait for 60 ns; wait until clk'event and clk = '1'; valid_bit <= '1'; wait for 2405 ns; wait until clk'event and clk = '1'; valid_bit <= '0'; wait; end process; все равно совпадения нет... сейчас

-

serial to parallel (vhdl)

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

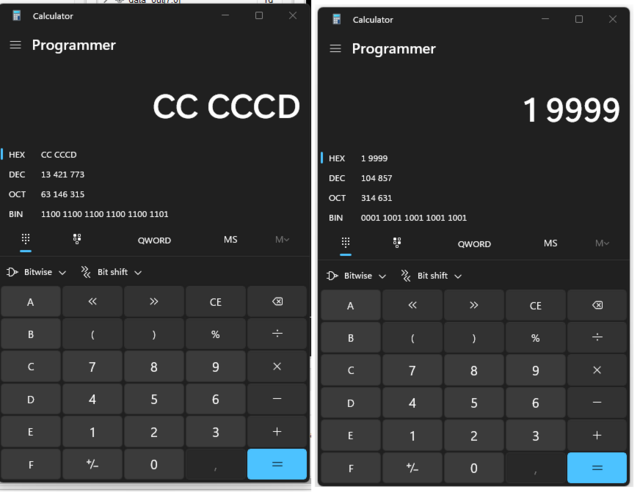

Всем привет не могу придумать как исправить - не производиться запись одного бита Массив данных которые записались - выделил красной скобкой данные котрые я подавал с тестбенча - - выделил красной скобкой в тестбенче - єти данные следующие: constant data0 : std_logic_vector(29 downto 0) := "000000000000000000000000000000"; constant data1 : std_logic_vector(29 downto 0) := "000000000000000000000000000000"; constant data2 : std_logic_vector(29 downto 0) := "000000000000000000000000000000"; constant data3 : std_logic_vector(29 downto 0) := "000000000000000111111111111111"; constant data4 : std_logic_vector(29 downto 0) := "000000011111111000000001111111"; constant data5 : std_logic_vector(29 downto 0) := "000111100001111000011110000111"; constant data6 : std_logic_vector(29 downto 0) := "011001100110011001100110011001"; constant data7 : std_logic_vector(29 downto 0) := "101010101010101010101010101010"; я сравнил побитно одни данные я думаю проблема в 254 строке описания => reg_rx_word(to_integer(unsigned(reg_cnt_word)))(to_integer(unsigned(reg_cnt_bit_word))) <= bit_data; вернее в том как считают счетчики reg_cnt_word и reg_cnt_bit_word я так думаю, но как исправить не могу понять. Прошу помощи Обратите внимание data7 с тестбенча записались коректно у reg_rx_word(0), а далше нет deinterleaver.vhd deinterleaver_vhd_tst.vhd -

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

спасибо за помощь des00 -

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

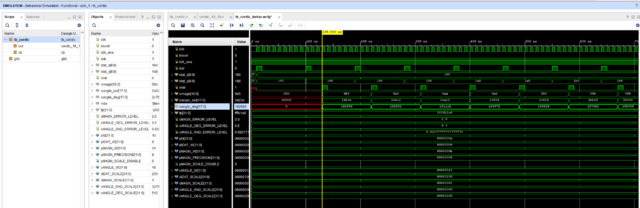

запустил по умолачанию (вообще не было проблем с запуском) как я понял с описания описание - pipeline если можно поясните пожалуйста параметры parameter int pN = 8 , // 0...15 parameter int pIDAT_W = 9 , parameter int pMAGN_W = pIDAT_W + 2 , parameter int pMAGN_PRECISION = pN , // 0..pN parameter bit pMAGN_SCALE_DISABLE = 0 pN - задаем разрядность данных pMAGN_PRECISION - точность ? что остальные обозначают? ))) -

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Огромное спасибо!!!! сейчас запущу симуляцию... PS Посмотрел время созданя поста - 10 лет прошло да и к сожалению память подводит - все не упомнишь ... Добавил в ветку Ссылки на готовые описания модулей на форуме - в первом сообщении Так не забудиться))) -

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

не мой Вы правы des00 мне надо вичислять φ = arctan( Q/I) и желательно в пайплайне... понял корка кривая... жаль... (в очередной раз убеждаюсь что OpenCores доверять надо на 1%) Может кто-то может поделиться рабочей коркой?