-

Постов

3 864 -

Зарегистрирован

Весь контент Maverick_

-

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

прошу помогите разобраться - время не мой друг сейчас... -

Помощь с core atan

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

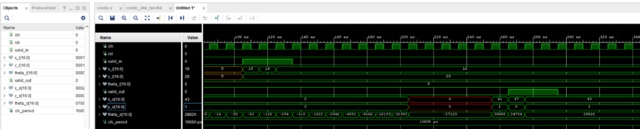

наконец появилось время доразобраться написал тестбенч для define RADIAN_16... получил как проверить выходные данные на "калькуляторе" не соображу/запутался... в матлабе для первой пары данных atan(15/20)=0.6435 сделал мат операции с результатом симуляциии 24734/32768=0.7548 24734/65636=0.3774 2^16=65636 2^15=32768 числа разные на симуляции и в матлабе ... или погрешность вычисления в кордике? или я не правильно считаю? cordic.v cordic_vhd_tst.vhd -

у Вас память описана как компонент/модуль? в проект подключается как компонент/модуль?

-

поробуйте так http://www2.mbari.org/~coletti/dropbox/Altera Quartus II Version 9.0/quartusii_handbook_9.0.pdf стр 273 module clear_ram ( input clock, input reset, input we, input [7:0] data_in, input [4:0] address, output reg [7:0] data_out ); reg [7:0] mem [0:31]; integer i; always @ (posedge clock or posedge reset) begin if (reset == 1'b1) mem[address] <= 0; else if (we == 1'b1) mem[address] <= data_in; data_out <= mem[address]; end endmodule

-

а Wizard/Core Generator нету? сгенерировали б и проблем нет

-

Всем спасибо)))

-

что именно?

-

реализация IIR - 3 порядка

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здраствуйте! подскажите как оптимально описать такую функцию в потоковом описании (pipeline) y[n] = a2 * x[n-2] + a1 * x[n-1] + a0 * x[n] - 2 * y[n-1] - y[n-2] где a1, a2, a0 коеф-ти я подумываю описывать нападобии library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity moving_average is generic ( G_NBIT : integer := 8; G_AVG_LEN_LOG : integer := 2 ); port ( i_clk : in std_logic; i_rstb : in std_logic; i_sync_reset : in std_logic; -- input i_data_ena : in std_logic; i_data : in std_logic_vector(G_NBIT-1 downto 0); -- output o_data_valid : out std_logic; o_data : out std_logic_vector(G_NBIT-1 downto 0)); end moving_average; architecture rtl of moving_average is type t_moving_average is array (0 to 2**G_AVG_LEN_LOG-1) of signed(G_NBIT-1 downto 0); signal p_moving_average : t_moving_average; signal r_acc : signed(G_NBIT+G_AVG_LEN_LOG-1 downto 0); -- average accumulator signal r_data_valid : std_logic; begin p_average : process(i_clk,i_rstb) begin if(i_rstb='0') then r_acc <= (others=>'0'); p_moving_average <= (others=>(others=>'0')); r_data_valid <= '0'; o_data_valid <= '0'; o_data <= (others=>'0'); elsif(rising_edge(i_clk)) then r_data_valid <= i_data_ena; o_data_valid <= r_data_valid; if(i_sync_reset='1') then r_acc <= (others=>'0'); p_moving_average <= (others=>(others=>'0')); elsif(i_data_ena='1') then p_moving_average <= signed(i_data)&p_moving_average(0 to p_moving_average'length-2); r_acc <= r_acc + signed(i_data)-p_moving_average(p_moving_average'length-1); end if; o_data <= std_logic_vector(r_acc(G_NBIT+G_AVG_LEN_LOG-1 downto G_AVG_LEN_LOG)); -- divide by 2^G_AVG_LEN_LOG end if; end process p_average; end rtl; описание которой реализована по формуле вычисления среднего но пока не придумал как єто сделать -

посмотрите (не использовал, просто нашел)

-

DSP блоки, ПЛИС

Maverick_ ответил lexa95 тема в Работаем с ПЛИС, области применения, выбор

Вам надо работать с проектом в целом - сделать сигнал разрешения работы для всех модулей - чтобы все модули работали когда должны, в другое время триггеры не должны"щелкать"(переключаться по тактовой частоте). Возможно перейти на потоковое (возможно с распаралеливанием вычислений) решение в котором вычисления производятся постоянно с приходом данных - с решения в котором пытаетесь за короткий промежуток времени все посчитать, потому что нужно "втиснуться" во временной интервал... Пересмотрите Ваш алгоритм обработки еще раз, возможно сделать потоковое вычисление с возможным распаралеливанием вычислений чтобы снизить тактовую частоту... -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

в самое яблочко))) Спасибо Денис -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

еще вопрос - подскажите пожалуйста, как правильно описать pipeline задержку чтоби она размещалсь на LUTRAM файл верхнего уровня library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity pipeline_delay_bus is generic ( NUM_INSTANCES : integer := 4; PIPELINE_STAGES : integer := 4; RESET_ACTIVE_LEVEL : std_logic := '1' ); port ( Clock : in std_logic; Reset : in std_logic; valid : in std_logic; Sig_in : in std_logic_vector(NUM_INSTANCES-1 downto 0); Sig_out : out std_logic_vector(NUM_INSTANCES-1 downto 0); ready : out std_logic ); end entity pipeline_delay_bus; architecture behavioral of pipeline_delay_bus is begin gen_pipeline_inst : for i in 0 to NUM_INSTANCES-1 generate pipeline_inst : entity work.pipeline_delay generic map ( PIPELINE_STAGES => PIPELINE_STAGES, RESET_ACTIVE_LEVEL => RESET_ACTIVE_LEVEL ) port map ( Clock => Clock, Reset => Reset, ena => valid, Sig_in => Sig_in(i), Sig_out => Sig_out(i) ); end generate gen_pipeline_inst; process(all) begin if Reset = '1' then ready <= '0'; elsif rising_edge(Clock) then ready <= valid; end if; end process; end architecture behavioral; файл самой задержки library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity pipeline_delay is generic ( PIPELINE_STAGES : integer; RESET_ACTIVE_LEVEL : std_logic := '1' ); port ( Clock : in std_logic; Reset : in std_logic; ena : in std_logic; Sig_in : in std_logic; Sig_out : out std_logic ); end entity; architecture rtl of pipeline_delay is signal pl_regs : std_logic_vector(1 to PIPELINE_STAGES); begin process(all) begin if Reset = RESET_ACTIVE_LEVEL then pl_regs <= (others => '0'); elsif rising_edge(Clock) then if ena = '1' then if PIPELINE_STAGES = 1 then pl_regs(1) <= Sig_in; else pl_regs <= Sig_in & pl_regs(1 to pl_regs'high-1); end if; end if; end if; Sig_out <= pl_regs(pl_regs'high); end process; end architecture; ситуация следующая если я в компоненте pipeline_delay комментирую строку -- if ena = '1' then то я у меня вивадо 2019,1 делает на LUtRAM если нет то на регистрах. как сделать сдвигающий регистр на SRL на LUTRAM с сигналом разрешения работи(valid)? PS https://docs.xilinx.com/r/en-US/ug901-vivado-synthesis/32-Bit-Shift-Register-Coding-Example-One-VHDL видел... -

Огромное спасибо, помогло.... прямо в цель))))

-

ошибка в ISIM vivado

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем привет есть проект - компилируется... когда запускю симуляцию, то появляется ошибка Starting static elaboration ERROR: [VRFC 10-1378] slice direction differs from its index type range [D:/project/xilinx/hdl/correlation_demodulator/source_hdl/shift_srl_delay_bus.vhd:76] ERROR: [VRFC 10-664] expression has 32 elements ; expected 16 [D:/project/xilinx/hdl/correlation_demodulator/source_hdl/shift_srl_delay_bus.vhd:76] ERROR: [XSIM 43-3322] Static elaboration of top level Verilog design unit(s) in library work failed. как испраивить не пойму... в проекте используется package library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; package mod_pkg is constant NUM_INSTANCES : integer := 128; constant NUM_PIPELINE : integer := 32; constant PIPELINE_STAGES : integer := 15; constant RESET_ACTIVE_LEVEL : std_logic := '1'; constant AWIDTH : integer := NUM_PIPELINE/2; --:= 16; constant BWIDTH : integer := NUM_PIPELINE/2; --:= 16; type arr_reg_const is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(NUM_PIPELINE-1 downto 0); type arr_comlex_reg_re is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(AWIDTH-1 downto 0); -- (AWIDTH-1 downto 0) type arr_comlex_reg_im is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(BWIDTH-1 downto 0); -- (BWIDTH-1 downto 0) type arr_comlex_result_re is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(AWIDTH+BWIDTH downto 0); type arr_comlex_result_im is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(AWIDTH+BWIDTH downto 0); end modulator_pkg; в топе компонент обявлен: component shift_srl_delay_bus is generic ( NUM_INSTANCES : integer := 128; NUM_PIPELINE : integer := 32; PIPELINE_STAGES : integer := 15; RESET_ACTIVE_LEVEL : std_logic := '1' ); port ( clk : in std_logic; rst : in std_logic; valid : in std_logic; data_in : in std_logic_vector(NUM_PIPELINE-1 downto 0); data_re_out : out arr_comlex_reg_re; data_im_out : out arr_comlex_reg_im ); end component; ----- shift_srl_delay_bus_inst : shift_srl_delay_bus generic map ( NUM_INSTANCES => NUM_INSTANCES, NUM_PIPELINE => NUM_PIPELINE, PIPELINE_STAGES => PIPELINE_STAGES, RESET_ACTIVE_LEVEL => '1' ) port map( clk => clk, rst => rst, valid => valid, data_in => data_in, data_re_out => reg_data_re, data_im_out => reg_data_im ); само описание компонента library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; library work; use work.mod_pkg.all; entity shift_srl_delay_bus is generic ( NUM_INSTANCES : integer := 128; NUM_PIPELINE : integer := 32; PIPELINE_STAGES : integer := 15; RESET_ACTIVE_LEVEL : std_logic := '1' ); port ( clk : in std_logic; rst : in std_logic; valid : in std_logic; data_in : in std_logic_vector(NUM_PIPELINE-1 downto 0); data_re_out : out arr_comlex_reg_re; data_im_out : out arr_comlex_reg_im ); end entity shift_srl_delay_bus; architecture behavioral of shift_srl_delay_bus is type t_const is array (0 to (NUM_INSTANCES-1)) of std_logic_vector(NUM_PIPELINE-1 downto 0); signal reg_data_in : t_const; signal reg_data_out : t_const; --signal reg_data_re : std_logic_vector(AWIDTH-1 downto 0); --signal reg_data_im : std_logic_vector(BWIDTH-1 downto 0); begin gen_pipeline_bus_inst : for i in 0 to NUM_INSTANCES-1 generate pipeline_bus_inst : entity work.pipeline_delay_bus generic map( NUM_INSTANCES => NUM_PIPELINE, PIPELINE_STAGES => PIPELINE_STAGES,--3 RESET_ACTIVE_LEVEL => '1' ) port map( Clock => clk, Reset => rst, valid => valid, Sig_in => reg_data_in(i), Sig_out => reg_data_out(i), ready => open ); end generate gen_pipeline_bus_inst; process(all) begin if rst = '1' then reg_data_in <= (others => (others => '0')); data_re_out <= (others =>(others => '0')); data_im_out <= (others =>(others => '0')); elsif rising_edge(clk) then for i in reg_data_in'high downto reg_data_in'low + 1 loop --for i in 0 to (NUM_INSTANCES-1) loop reg_data_in(i) <= reg_data_out(i - 1); end loop; reg_data_in(reg_data_in'low) <= data_in; --data_out <= reg_data_out(reg_data_out'high); end if; for i in reg_data_in'high downto reg_data_in'low + 1 loop --for i in 0 to (NUM_INSTANCES-1) loop data_re_out(i) <= reg_data_in((NUM_PIPELINE/2)-1 downto 0)(i); --!!!!!!!! data_im_out(i) <= reg_data_in(NUM_PIPELINE-1 downto NUM_PIPELINE/2)(i); --!!!!!!!! end loop; end process; end architecture behavioral; ошибка в строке где в коментариях много !!!! подскажите пожалуйста как подправить -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

спасибо -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

огромное спасибо des00 - я упустил из виду такую возможность - заработался... действительно... -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

по другому я не знаю как сделать -

pipeline delay

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

update получился такой "монстр" library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; entity delay_line is generic ( W : integer := 8; -- data width L : integer := 10; -- delay length ); port( clk : in std_logic; rst : in std_logic; delay_len : in std_logic_vector(L-1 downto 0); -- delay length, shall be > 3 i_data : in std_logic_vector(W-1 downto 0); o_data : out std_logic_vector(W-1 downto 0)); end delay_line; architecture rtl of delay_line is --type t_ram is array (L-1 downto 0) of std_logic_vector(W-1 downto 0); type t_ram is array ((2**L)-1 downto 0) of std_logic_vector(W-1 downto 0); signal m_ram : t_ram; signal r_addr_wr : unsigned(L-1 downto 0); signal r_addr_rd : unsigned(L-1 downto 0); signal r_enable_read : std_logic; signal reg_data1 : std_logic_vector(W-1 downto 0); signal reg_data2 : std_logic_vector(W-1 downto 0); signal reg_data : std_logic_vector(W-1 downto 0); signal reg_o_data : std_logic_vector(W-1 downto 0); signal reg_o_data1 : std_logic_vector(W-1 downto 0); signal reg_o_data2 : std_logic_vector(W-1 downto 0); signal reg_o_data3 : std_logic_vector(W-1 downto 0); begin process (all) begin if(rst = '1') then reg_data1 <= (others => '0'); reg_data2 <= (others => '0'); reg_data <= (others => '0'); reg_o_data1 <= (others => '0'); reg_o_data2 <= (others => '0'); reg_o_data3 <= (others => '0'); elsif rising_edge(clk) then if unsigned(delay_len) = 1 then reg_o_data1 <= i_data; elsif unsigned(delay_len) = 2 then reg_data1 <= i_data; reg_o_data2 <= reg_data1; elsif unsigned(delay_len) = 3 then reg_data1 <= i_data; reg_data2 <= reg_data1; reg_o_data3 <= reg_data2; else reg_data <= i_data; end if; end if; end process; process (all) begin -- if(rst = '1') then -- reg_o_data1 <= (others => '0'); -- reg_o_data2 <= (others => '0'); -- reg_o_data3 <= (others => '0'); -- elsif rising_edge(clk) then if unsigned(delay_len) = 1 then o_data <= reg_o_data1; elsif unsigned(delay_len) = 2 then o_data <= reg_o_data2; elsif unsigned(delay_len) = 3 then o_data <= reg_o_data3; else o_data <= reg_o_data; end if; -- end if; end process; p_write : process (all) begin if(rst = '1') then r_addr_wr <= (others => '0'); r_enable_read <= '0'; elsif rising_edge(clk) then m_ram(r_addr_wr) <= reg_data; if(r_addr_wr < unsigned(delay_len)) then r_addr_wr <= r_addr_wr + 1; else r_addr_wr <= (others => '0'); r_enable_read <= '1'; -- enable reading section end if; end if; end process p_write; p_read : process (all) begin if(rst = '1') then r_addr_rd <= (others => '0'); reg_o_data <= (others => '0'); elsif rising_edge(clk) then if(r_enable_read = '1') then reg_o_data <= m_ram(r_addr_rd) ; -- additional delay if(r_addr_rd < unsigned(delay_len)) then r_addr_rd <= r_addr_rd + 1; else r_addr_rd <= (others => '0'); end if; end if; end if; end process p_read; end rtl; -

pipeline delay

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем привет Мне надо разработать настраеваемую задержку сигнала, т.к. задержка максимальная большая больше 1000 может принимать значение, то решил делать на BRAM library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; entity delay_line is generic( W : integer := 8; -- data width L : integer := 1200); -- delay length, shall be > 3 port( i_clk : in std_logic; i_sync_reset : in std_logic; i_data : in std_logic_vector(W-1 downto 0); o_data : out std_logic_vector(W-1 downto 0)); end delay_line; architecture rtl of delay_line is type t_ram is array (L-2 downto 0) of std_logic_vector(W-1 downto 0); signal m_ram : t_ram; signal r_addr_wr : integer range 0 to L-2; signal r_addr_rd : integer range 0 to L-2; signal r_enable_read : std_logic; begin p_write : process (i_clk) begin if rising_edge(i_clk) then if(i_sync_reset='1') then r_addr_wr <= 0; r_enable_read <= '0'; else m_ram(r_addr_wr) <= i_data; if(r_addr_wr<L-2) then r_addr_wr <= r_addr_wr + 1; else r_addr_wr <= 0; r_enable_read <= '1'; -- enable reading section end if; end if; end if; end process p_write; p_read : process (i_clk) begin if rising_edge(i_clk) then if(i_sync_reset='1') then r_addr_rd <= 0; else if(r_enable_read='1') then o_data <= m_ram(r_addr_rd) ; -- additional delay if(r_addr_rd<L-2) then r_addr_rd <= r_addr_rd + 1; else r_addr_rd <= 0; end if; end if; end if; end if; end process p_read; end rtl; но в описании есть для меня ограничение что delay length, shall be > 3 Это связано с тем, что для обеспечения корректной работы задержки необходимо иметь как минимум 2 разных значения в памяти, а также задержать входной сигнал на минимум 1 такт. L я сделаю как вход... Как посоветуете лучше сделать чтоби обойти ограничение? Мне надо с L = 1, 2 и более Думаю вначале поставить мультиплексор process (all) begin if L = 0 then o_data <= i_data; elsif L = 1 then reg_data1 <= i_data; elsif L = 2 then reg_data2 <= i_data; elsif L = 3 then reg_data3 <= i_data; else reg_data <= i_data; end if; end process; в котором для задержек меньше равно 3 - организовать свои задержки -

скачать книгу

Maverick_ опубликовал тема в Документация

помогите пожалуйста скачать https://books.google.com.ua/books?hl=uk&lr=&id=16PV-fhKasoC&oi=fnd&pg=PR15&dq=ground+penetrating&ots=u-dCXpZ0xc&sig=QAaYTvYjgzWzwrlHH3PYpalVQ8U&redir_esc=y#v=onepage&q=ground penetrating&f=false или отсюда https://www.scribd.com/document/51544215/387580689 может у кого то есть 2тома - поделитесь пожалуйста -

как насчет расстояния от первого максимума?

-

update https://www.xilinx.com/content/dam/xilinx/support/documents/sw_manuals/xilinx14_1/plugin_ism.pdf стр 82 Limitations HWCoSim has the following limitations: • Only one instance in a design can be selected for hardware co-simulation, and it cannot be the top-level test bench itself. • The selected instance for hardware co-simulation must be able to be synthesized using XST, and must be able to be implemented on the target FPGA device of the selected board. The lockstep hardware co-simulation has additional restrictions on clocking and I/Os: • The co-simulation instance in hardware is clocked with an emulated clock source that ISim controls, and is asynchronous to the simulation. Thus, the co-simulation does not exactly model the design scenario running in hardware, or serve as a timing simulation. • The instance under co-simulation cannot have access to external I/Os or Multi-Gigabit Transceivers (MGTs), nor can it instantiate primitives (such as DCMs/ PLLs) that require a continuous clock or a clock at a specific frequency. • All ports of the instance under co-simulation must be routable to a slice register or LUT. Certain resources on the FPGA require dedicated routes, such as to an IOB or to certain port of a primitive, and thus cannot be wired to any port of the instance under co-simulation. Задам с тестбенча второй клок...

-

проблема с симуляцией в isim (vivado)

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

привет возникла проблема с симуляцией в isim Внутри проекта стоит PLL (ip core) - клок в симуляции виден, но логика от єтого PLL не работает (желтеют сигнали). Интересует как исправить? Логика с клоком заданного в тестбенче работает. Может какой - то атрибут записать сугубо для симуляции для клока от PLL??? Как вариант исправления - задать клок с тестбенча без использования PLL (ip core), но тогда будет разница проекта для синтеза и симуляции