lyaksandrov

Участник-

Постов

23 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о lyaksandrov

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Двухступенчатый Д-триггер

lyaksandrov ответил lyaksandrov тема в Схемотехника

Не понял вас. -

Двухступенчатый Д-триггер

lyaksandrov ответил lyaksandrov тема в Схемотехника

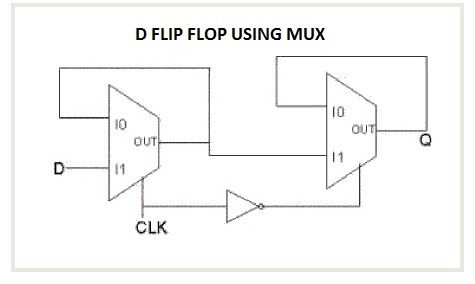

Это обычный двухступенчатый Д триггер, а мне нужно с мультиплексором на входе, я нашел схему на мультиплексорах, но теперь нужно как-то правильно установить срабатывающие по фронту с вход установки Set и вход сброса Reset -

Двухступенчатый Д-триггер

lyaksandrov опубликовал тема в Схемотехника

Всем привет, можете ли вы помочь или рассказать мне, как выглядит логическая схема двухступенчатого D-триггера (триггера) с мультиплексором из 2 в 1 на входе, срабатывающий по фронту с входами установки Set и сброса Reset? -

Я понимаю, что сам не потяну, поэтому и обратился на форум за помощью. Я понимаю логику, как должно все работать, но так как не хватает званий в программировании не могу реализовать это сам. Если бы было больше времени, я и бы смог осилить это, но к сожалению его нет, так как это задание по учебе). На счет скорости, я понимаю, что нужно сделать мультиплексор, на него подавать значения полученные делителем при разных скоростях и потом выбирать нужную скорость. Не было бы проблем, если бы нужно было бы сделать на 1 скорости, я бы смог это реализовать используя разные источники. Но как сделать переключатель программно, не понимаю. Преподаватель объяснил схемотехнику, ну а остальное дело за мной, но что-то как-то не выходит(

-

Здравствуйте, я посмотрел код, который вы прислали, действительно все работает, но не немного не могу понять как, особенно в тестбенче. И можно спросить еще, что нужно исправить что бы принималось не 8 бит данных, а 6. Еще на счет скорости хотел узнать, можно ли сделать что бы она переключалась допустим значение 1 это будет скорость 57600, а значение 0 будет 115600?

-

Не могу понять, как мне сделать переключение скорости. Нужна переменная любая, в которую я могу до запуска программы записать 1 или 0, это и будут скорости, а как мне в тестбенче это сделать? Я понимаю, что нужно задавать условие, но не знаю как это написать( С четностью разобрался

-

Написал код, все работает, но мне теперь нужно сделать, чтобы можно было переключать скорость передачи данных (скорость 57600 либо 115200 кбит.с). Далее необходимо сделать проверку на бит четности, посчитать количество едениц записанных в data и вывести результат если нечетное количество то все верно, если четное то неверно. Можете подтолкнуть или направить как можно сделать это? На приемник присылаю 111111 Код: module uart_rx (clk, rx, data, data_ready); input wire clk; input wire rx; output reg [5:0] data; output data_ready; reg rx_ff1; // защелка для старта передачи always @(posedge clk) begin rx_ff1 <= rx; end // отлавливаем старт-бит wire spad = ~rx_ff1; // состояние приемника reg receive; // для корректной симуляции initial receive = 0; //если старт бит то включаем режим приема //если приняли выключаем always @(posedge clk) if (spad) receive <= 1'b1; else if (data_ready) receive <= 1'b0; //cигнал начала приема //Для инициализации счетчиков wire start = ~receive & spad; //поскольку у нас clk в 2 раза быстрее rx, делаем делитель reg [2:0] count_os; always @(posedge clk) if (start) count_os <= 4'b101; else if(receive) count_os <= count_os + 1'b1; //при переполнении счетчика-делителя выводим бит из входных данных wire get_bit = ~|count_os; //счетчик принятых данных // Как примем 6 бит можно останавливаться reg [3:0] count_byte; always @(posedge get_bit or posedge start) begin if (start) count_byte <= 0; else count_byte <= count_byte + 4'b1; end wire data_ready = (count_byte == 7); //сдвигаем регистр данных на одну позицию вправо, //и пишем принятый бит в старший бит always @(posedge get_bit) if (!data_ready) data <= {rx_ff1, data[5:1]}; endmodule module test_uart_rx; reg clk; reg rx; wire data_received; wire [5:0] data_in; uart_rx u_rx (clk, rx, data_in, data_received); always #11 clk = ~clk; initial begin clk = 0; rx = 1; #205 rx = 0; #173 rx = 1; #173 rx = 1; #173 rx = 1; #173 rx = 1; #173 rx = 1; #173 rx = 1; end initial #2000 $finish; endmodule

-

Вообщем много что перечитал, попробовал сделать, вроде что-то получилось, но не знаю так ли это должно работать))? Делал со скоростью 57600 module RS232Receive( input clk, input rx, output reg [5:0] data, //liniya dannix output reg dataReady, //liniya gotovnosti output reg error //signal oshibki ); parameter Idle = 2'b00; //ojidanie parameter StartBit = 2'b01; //startbit parameter DataBit = 2'b10; // bit dannix parameter StopBit = 2'b11; //stopbit parameter Divider = 16'd278; //delitel schetchika reg [3:0] state, nextState; //registri sostoyaniya 1 tekyshee i 2 sledyeshee reg [3:0] bitCount; //schetchik bit reg [8:0] tickCount; //schetchik impylsov kvarcovogo generatora reg [5:0] rData; //reg sbora prinyatogo bayta initial begin //NASHALNOE SOSTOYANIE REGISTROV state = Idle; nextState = Idle; rData = 0; bitCount = 4'b0000; tickCount = 0; error = 1'b0; end always @(posedge clk) //po perednemy fronty taktovogo signala prisvaivaem tekyshemy sostoyaniya begin state = nextState; case(state) //sostoyanie ojidaniya Idle: begin rData = 8'h00; //sostoyanie ojidanie sbrasivaem registr prinyatogo bayta tickCount = 0; bitCount = 4'b0000; error = 1'b0; if (rx == 1'b0) begin nextState = StartBit; end //esli na vhode 0, to sledyysheem sostoyaniem bydet startbit end StartBit: begin //shitaem impylsi, esli ih polovina ot vsei dlitelnosti bita to proveryaem sostoyanie linii dannix tickCount = tickCount + 1; if (tickCount[8:0] == Divider[15:1]) begin if (rx == 1'b0) //esli 0 to oshibki net begin error = 1'b0; end else begin error = 1'b1; //esli 1 to oshibka i perehodim s sostoyanie ojidaniya nextState = Idle; end end else if (tickCount == Divider) //esli doshitali do konca bita, to sbrasivaem chetchiki i perehodim v sostoyanie priema begin tickCount = 0; nextState = DataBit; end end DataBit: begin tickCount = tickCount + 1; if (tickCount[8:0] == Divider[15:1]) //takje schitaem do chentra bita begin rData[bitCount] = rx; // v registr ykladivaem kajdii schitaniy bit bitCount = bitCount + 1; //shitaem biti end else if (tickCount==Divider) // kak doshli do konca bita begin tickCount = 0; //sbrasivaem schetchik esli prishlo eshe ne 6 bit to ostaemsya tyt je if (bitCount == 6) begin bitCount = 0; nextState = StopBit; end //esli prishlo 6, to perehodim k priemy stop bit else nextState = DataBit; end end StopBit: begin tickCount = tickCount + 1; if (tickCount[8:0] == Divider[15:1]) begin if (rx == 1'b1) //proverka sostoyaniya vhodnoi linii, esli 1 to vse OK, esli 0 to oshibka begin error = 1'b0; data = rData; //vistavlyaem na vihod registr prinyatogo bayta dataReady = 1'b1; //signal gotov end else begin error = 1'b1; //oshibka dataReady = 1'b0; nextState = Idle; //perehodim v ojidanie end end else if (tickCount == Divider) begin dataReady = 1'b0; tickCount = 0; nextState = Idle; end end default: state = Idle; endcase end endmodule //////////////////////////////////////////// module RS232Receive_tb; reg clk; wire [5:0] data; wire dataReady; wire error; reg rx; RS232Receive r( .clk(clk), .data(data), .dataReady(dataReady), .error(error), .rx(rx) ); always #5 clk = ~clk; initial begin clk = 0; #5; rx = 1; #520800; rx = 0; #52080; //start rx = 0; #52080; rx = 1; #364560; rx = 1; #260400; end endmodule

-

Конфигурируемый приемник RS-232

lyaksandrov опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем, привет. Сразу скажу, что в проектировании на ПЛИС я полный 0. Но выпала такая потребность (для учебы) создать приемник rs 232. Посмотрел много всего, но так и не разобрался и ни один код не заработал. Требуемые параметры 16 МГц Скорости 57600 и 115200, Бит четности Odd 6. Может кто направить или подсказать с чего начать делать? Возможно у кого-то есть свои наработки. Язык использую Verilog. -

Подключение нескольких ЦАП к СТМ32

lyaksandrov ответил lyaksandrov тема в ARM, 32bit

Независимые каналы должны быть, тк течет ток и снимается напряжение по 4х проводной схеме измерения сопротивления -

Подключение нескольких ЦАП к СТМ32

lyaksandrov ответил lyaksandrov тема в ARM, 32bit

Где можно посмотреть или почитать как и куда подключать sync к микроконтроллеру? -

Подключение нескольких ЦАП к СТМ32

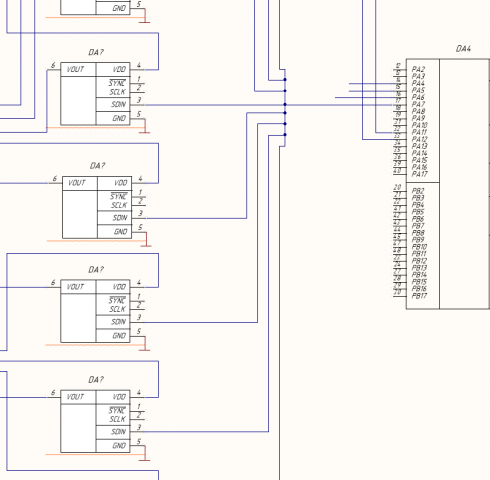

lyaksandrov ответил lyaksandrov тема в ARM, 32bit

ЦАПы все одной разрядности, если можно, можете поподробнее про SYNC и GPIO? Это значит просто подключать их к пинам у которых тип I/O? Все 8 пинов MOSI ЦАПА подключать к одному пину MOSI (PA7) микроконтроллера? Так будет правильно? -

Подключение нескольких ЦАП к СТМ32

lyaksandrov опубликовал тема в ARM, 32bit

Всем привет, возник вопрос как подключить 8 отдельных ЦАП (AD5621BKSZ-500RL7) к микроконтроллеру stm32f103c8t7? -

Помогите разобраться с ОУ

lyaksandrov ответил lyaksandrov тема в Схемотехника

Нужно доработать эту, понять почему напряжение смещается, а не остается в 0 -

Помогите разобраться с ОУ

lyaksandrov опубликовал тема в Схемотехника

Всем привет, хочу понять, почему так ведет себя схема на ОУ, а именно есть генератор импульсных сигналов от 0 до 3В, при подаче на 1 усилитель я меняю среднюю точку на 10В, далее сигнал попадает на 2 усилитель, где усиливается сигнал от 0 до 20В, затем идет на преобразователь напряжения в ток. Но когда меняю на генераторе импульсных сигналов напряжение от 0.5 до 2.5В, то есть оставляю среднюю точку 1.5В, затем подаю сигнал на 1 усилитель, тем самым поднимаю среднюю точку до 10В, далее когда сигнал переходит на 2 усилитель и усиливает сигнал от 2.45 до 16.45В. И самое главное вопрос! почему сигнал не остался в 0, а сместился до 2.45В, и как-нибудь можно это исправить, чтоб он оставался в 0?