-

Постов

3 861 -

Зарегистрирован

Весь контент Maverick_

-

Так можно долго ждать :)

-

Отдельно мастер записи работает. Вместе я не проверял работу. Запуск автоматов делается программно и даже в отдельных программах. Сейчас не работает автомат чтения. если работает, да значит 0 во вложении мастер чтения vga_generator.vhd

-

Добрый день коллеги Сделал в qsys SOC систему (циклон 5 SOC ) в котором есть 2 dma мастера (разные компоненты в qsys ) - один на чтение, второй на запись. Эти мастера подсоеденены на один порт DDR памяти. На запись мастер работает без проблем. Когда начал запускать второй мастер на чтение данных из DDR памяти то у меня на шине авалон постоянно waiterequest = "1" Хотя эти мастера не работают одновременно. В чем может быть проблема? ЗЫ Сейчас думаю эти мастера посадить на разные порты DDR памяти

-

StewartLittle спасибо большое

-

Там какой то скрипт надо запустить для развертывания проекта для eclipce nios, но как это сделать не понимаю у меня 18,1 квартус я качал проект For Cyclone V SoC :

-

Всем привет Надо воссоздать проект https://www.intel.com/content/www/us/en/programmable/support/support-resources/design-examples/intellectual-property/embedded/nios-ii/exm-spi-bridge.html Но у меня не получется создать проект для ниоса (eclipse - nios) Прошу помощи... PS если будут проблемы с скачиванием проекта по ссылки - сообщите - предоставлю файлы PS PS очень надо...

-

Вопрос решен...

-

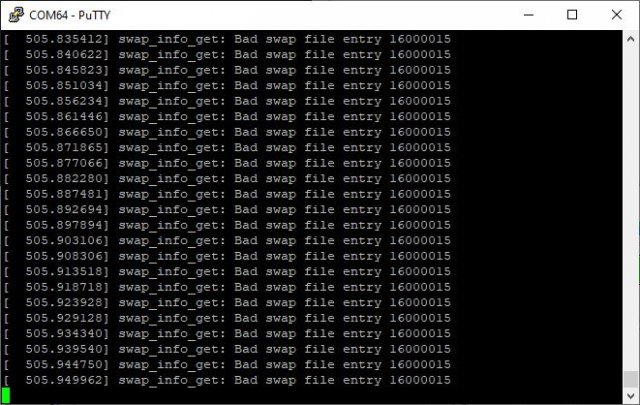

Зависание линукс

Maverick_ опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

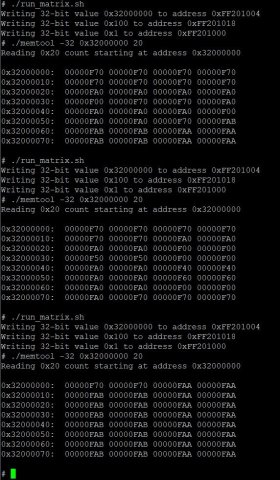

Есть SOC система на cyclon V SOC Все работало, просто сбоило передача данных по DMA Нашел вроде свою ошибку в fpga части что я к ipcore двухклоковое фифо я подключился к wrused. Решил исправить на rdused - пересоздал корку фифо и скомпилировал проект. После этого линукс на арм процессоре начал выдавать следующее - вложение Подскажите пожалуйста где я не прав? Как исправить это зависание? -

Добрый день Роман

Прошу помощи с remoute update

Письмо отправил

От кого: Alex <[email protected]>Кому: "Roman Zolotukho" <[email protected]>Тема: remoute update fpgaДата: 14 января 2021, 13:42:53Буду очень благодарен за помощь. -

у меня квартус 17.1 стандарт Как это если сборка ситемы проводилась в родном qsys???

-

Remote update cyclone4

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

Создал проект в qsys в котором используются ipcore altera_remoute_update и altera_serial_flash_controller. Генерация hdl в qsys проходит без ошибок. Но на этапе синтеза появляется ошибка: Как эту ошибку побороть не пойму, прошу помощи... PS https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altremote.pdf Есть слова Я их в проекте делал... -

Да, интересно становиться...

-

Адресация 4 байтная

-

Проблема с фифо

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

Есть проект в котором я принимаю данные с клоком (72,5 МГц) с фотосенсора и дальше на двухклоковое фифо. С другого конца работает автомат мастера авалон шины который пишет принятые данные в DDR память. Проблема заключаеться в том что на сигналтабе я вижу правильные данные. В памяти почему то сдвоенные данные. Можете подсказать в чем проблема? Description1.docx -

конвертация из схематика

Maverick_ ответил ysmat тема в Среды разработки - обсуждаем САПРы

Полная конвертация только ручками. Конвертор это сделает как схему содинений библиотечных примитивов на verilog или VHDL -

library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; entity delay_line is generic( W : integer := 8; -- data width L : integer := 1200); -- delay length, shall be > 3 port( i_clk : in std_logic; i_sync_reset : in std_logic; i_data : in std_logic_vector(W-1 downto 0); o_data : out std_logic_vector(W-1 downto 0)); end delay_line; architecture rtl of delay_line is type t_ram is array (L-2 downto 0) of std_logic_vector(W-1 downto 0); signal m_ram : t_ram; signal r_addr_wr : integer range 0 to L-2; signal r_addr_rd : integer range 0 to L-2; signal r_enable_read : std_logic; begin p_write : process (i_clk) begin if rising_edge(i_clk) then if(i_sync_reset='1') then r_addr_wr <= 0; r_enable_read <= '0'; else m_ram(r_addr_wr) <= i_data; if(r_addr_wr<L-2) then r_addr_wr <= r_addr_wr + 1; else r_addr_wr <= 0; r_enable_read <= '1'; -- enable reading section end if; end if; end if; end process p_write; p_read : process (i_clk) begin if rising_edge(i_clk) then if(i_sync_reset='1') then r_addr_rd <= 0; else if(r_enable_read='1') then o_data <= m_ram(r_addr_rd) ; -- additional delay if(r_addr_rd<L-2) then r_addr_rd <= r_addr_rd + 1; else r_addr_rd <= 0; end if; end if; end if; end if; end process p_read; end rtl; library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity moving_average is generic ( G_NBIT : integer := 8; G_AVG_LEN_LOG : integer := 2 ); port ( i_clk : in std_logic; i_rstb : in std_logic; i_sync_reset : in std_logic; -- input i_data_ena : in std_logic; i_data : in std_logic_vector(G_NBIT-1 downto 0); -- output o_data_valid : out std_logic; o_data : out std_logic_vector(G_NBIT-1 downto 0)); end moving_average; architecture rtl of moving_average is type t_moving_average is array (0 to 2**G_AVG_LEN_LOG-1) of signed(G_NBIT-1 downto 0); signal p_moving_average : t_moving_average; signal r_acc : signed(G_NBIT+G_AVG_LEN_LOG-1 downto 0); -- average accumulator signal r_data_valid : std_logic; begin p_average : process(i_clk,i_rstb) begin if(i_rstb='0') then r_acc <= (others=>'0'); p_moving_average <= (others=>(others=>'0')); r_data_valid <= '0'; o_data_valid <= '0'; o_data <= (others=>'0'); elsif(rising_edge(i_clk)) then r_data_valid <= i_data_ena; o_data_valid <= r_data_valid; if(i_sync_reset='1') then r_acc <= (others=>'0'); p_moving_average <= (others=>(others=>'0')); elsif(i_data_ena='1') then p_moving_average <= signed(i_data)&p_moving_average(0 to p_moving_average'length-2); r_acc <= r_acc + signed(i_data)-p_moving_average(p_moving_average'length-1); end if; o_data <= std_logic_vector(r_acc(G_NBIT+G_AVG_LEN_LOG-1 downto G_AVG_LEN_LOG)); -- divide by 2^G_AVG_LEN_LOG end if; end process p_average; end rtl;

-

Всем спасибо за ответы - пока буду читать и разбираться :)

-

МОжно подробнее?

-

Работа с DDR памятью

Maverick_ опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день Есть глюки в работе DDR, подскажите пожалуста как можно узнать происходит ли Refresh данных? -

скачать http://en.pudn.com

Maverick_ ответил Maverick_ тема в Документация

большое спасибо -

скачать http://en.pudn.com

Maverick_ опубликовал тема в Документация

добрый день у кого то есть возможность скачать http://en.pudn.com/Download/item/id/3984573.html буду премного благодарен -

Добрый день Нашел в документации https://www.intel.com/content/www/us/en/programmable/documentation/sss1411439280066.html "Parallel Flash Loader Intel FPGA IP Core User Guide" Там в списке есть флеш память которая мне нужна: 128 Mbit S29GL128S 256 Mbit S29GL256S 512 Mbit S29GL512S Прочитал внимательней документцию - как я понял с помощью этой корки можно програмировать ПЛИС или саму флеш память А мне надо просто писать и читать (сохранять данные) ... Подскажите пожалуйста какую корку надо выбрать для работы с этой флеш памятью Работаю в квартус 17,1 - надо добавить в платформ дизайнер (qsys) PS Может у кого то есть пример работы...

-

Почему бы не реализовать таймер на логике, который счтал бы такты при передаче данных, а потом просто значение считать? PS просто на логике будет более достоверный результат

-

вы смотрели https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an755.pdf#unique_5 и https://www.altera.com/en_US/others/literature/an/an755_jesd204b_arm_avsoc_ref_design.zip не помогло?

-

Жаль...