-

Постов

3 861 -

Зарегистрирован

Весь контент Maverick_

-

проверьте еще питание fpga, для pll вчастности...

-

круто!!!

-

понял, спасибо за предупреждение и пояснение

-

Всем спасибо. - не увидел, спасибо что обратили внимание. Исправил, тактовая частота повысилась.

-

Мне остался по наследству модуль module alg_integrator_smart (clk, reset, start, base, data_in, data_slow, ready_const, clk_const, addr_const, data_const, tdpp, data_out, int_out, int_diff, tau_out); input clk, reset, start; input signed [15:0] data_in; input signed [47:0] data_slow; input signed [23:0] base; input ready_const, clk_const; input [5:0] addr_const; input [15:0] data_const; input signed [15:0] tdpp; output signed [47:0] data_out; output signed [15:0] int_out; output signed [15:0] int_diff; output signed [23:0] tau_out; reg signed [23:0] r_base = 24'sd51200; reg signed [47:0] resalt_r, sample_data; reg signed [63:0] resalt, resalt_i; reg [1:0] front_start; reg signed [23:0] tau_coeff = 24'sd117500;// 917.97 *128 reg signed [23:0] tau_calc = 24'sd117500;// 917.97 *128 reg signed [16:0] k1 = 17'sd0; reg signed [16:0] k2 = 17'sd0; reg tau_calc_en = 1'b0;// default reg signed [39:0] tau_acc; reg signed [16:0] tdpp_delta; //******************************************************* reg signed [23:0] fifo_amp [2:0]; reg signed [47:0] buf2; reg start_prev = 1'b0; reg signed [63:0] int_prev; reg signed [63:0] delta; //******************************************************* // process for update constants always @(posedge clk_const) begin if (ready_const) case (addr_const) 6'd2: tau_coeff[15:0] <= data_const; 6'd3: tau_coeff[23:16] <= data_const[7:0]; 6'd23: tau_calc_en <= data_const[3];// customize[3] -> + 8 6'd25: begin k2[15:0] <= data_const; k2[16] <= 1'b0; end// coefficient (top_discriminator) 6'd26: begin k1[15:0] <= data_const; k1[16] <= 1'b0; end// base temperature (bottom_discriminator) default: begin tau_coeff <= tau_coeff; tau_calc_en <= tau_calc_en; k2 <= k2; k1 <= k1; end endcase end // process tau calculation always@(negedge clk) begin tdpp_delta <= tdpp - k1; if (tau_calc_en == 1'b1) begin if (k1 > 0) // tau_calc <= tau_acc >>> 16; tau_calc <= tau_acc >>> 15; else tau_calc <= tau_coeff; end else tau_calc <= tau_coeff; end always@(posedge clk) begin // tau_acc <= (tau_coeff <<< 16) + k2 * tdpp_delta; tau_acc <= (tau_coeff <<< 15) + k2 * tdpp_delta; end // main process of integrator always@(posedge clk or negedge reset) begin if(reset == 1'b0) begin : resetting resalt <= 64'sd0; resalt_i <= 64'sd0; //resalt_r <= 48'sd0; buf2 <= 48'sd0; end else begin : calculating // input signal buffer fifo_amp[0] <= (data_in <<< 8) - r_base; fifo_amp[1] <= fifo_amp[0]; fifo_amp[2] <= fifo_amp[1]; // buf2 <= fifo_amp[0] * tau_coeff; buf2 <= fifo_amp[0] * tau_calc; if ((start_prev == 1'b1) & (start == 1'b0)) resalt_i <= resalt_i + buf2 - sample_data; else resalt_i <= resalt_i + buf2; resalt <= resalt_i + (fifo_amp[2] <<< 22); end end always@(posedge clk or negedge reset) if(reset == 1'b0) r_base <= r_base; else if ((start_prev == 1'b1) & (start == 1'b0)) r_base <= base; else r_base <= r_base; // process for update slow data always@(posedge clk or negedge reset) if (reset == 1'b0) sample_data <= 48'd0; else sample_data <= data_slow; // process for generate start vector always@(posedge clk) begin //front_start[0] <= start; //front_start[1] <= front_start[0]; start_prev <= start; end // process for calculate delta INT always@(posedge clk) begin delta <= resalt - int_prev; int_prev <= resalt; end // connect outputs assign data_out = resalt; assign int_out = resalt_i >>> 30; assign int_diff = delta >>> 30; assign tau_out = tau_calc; endmodule естественно разработчика я не застал, мои попытки увеличить тактовую хотя бы на 30-40 МГц не принесли результатов проблема в арифметике: buf2 <= fifo_amp[0] * tau_calc; if ((start_prev == 1'b1) & (start == 1'b0)) resalt_i <= resalt_i + buf2 - sample_data; else resalt_i <= resalt_i + buf2; resalt <= resalt_i + (fifo_amp[2] <<< 22); Квартус 18.1 для циклон5 дает 102MHz ... Да описание написано лет десять назад... работало на циклон3 я смог добиться 114МГц module alg_integrator_smart (clk, tau_coeff,k1,k2,tau_calc_en, reset, start, base, data_in, data_slow, ready_const, addr_const, data_const, tdpp, data_out, int_out, int_diff, tau_out); input clk, reset, start; input signed [15:0] data_in; input signed [47:0] data_slow; input signed [23:0] base; input ready_const; input [5:0] addr_const; input [15:0] data_const; input signed [23:0] tau_coeff; // = 24'sd117500;// 917.97 *128 input signed [16:0] k1; // = 17'sd0; input signed [16:0] k2; // = 17'sd0; input tau_calc_en; // = 1'b0;// default input signed [15:0] tdpp; output signed [47:0] data_out; output signed [15:0] int_out; output signed [15:0] int_diff; output signed [23:0] tau_out; reg signed [47:0] reg_data_slow; reg signed [23:0] r_base = 24'sd51200; reg signed [47:0] resalt_r, sample_data; reg signed [63:0] resalt, resalt_i; reg signed [63:0] resalt_a, resalt_b; reg signed [47:0] resalt0; reg [1:0] front_start; //reg signed [23:0] tau_coeff = 24'sd117500;// 917.97 *128 reg signed [23:0] tau_calc = 24'sd117500;// 917.97 *128 //reg signed [16:0] k1 = 17'sd0; //reg signed [16:0] k2 = 17'sd0; //reg tau_calc_en = 1'b0;// default reg signed [39:0] tau_acc; reg signed [31:0] tau_acc0; reg signed [31:0] tau_acc1; reg signed [16:0] tdpp_delta; //******************************************************* reg signed [23:0] fifo_amp [2:0]; reg signed [47:0] buf2; reg start_prev = 1'b0; reg signed [63:0] int_prev; reg signed [63:0] delta; //******************************************************* // process for update constants //always @(posedge clk) //clk_const //begin // if (ready_const) // case (addr_const) // 6'd2: tau_coeff[15:0] <= data_const; // 6'd3: tau_coeff[23:16] <= data_const[7:0]; // 6'd23: tau_calc_en <= data_const[3];// customize[3] -> + 8 // 6'd25: begin k2[15:0] <= data_const; k2[16] <= 1'b0; end// coefficient (top_discriminator) // 6'd26: begin k1[15:0] <= data_const; k1[16] <= 1'b0; end// base temperature (bottom_discriminator) // default: // begin // tau_coeff <= tau_coeff; // tau_calc_en <= tau_calc_en; // k2 <= k2; // k1 <= k1; // end // endcase //end // process tau calculation always@(negedge clk) begin tdpp_delta <= tdpp - k1; if (tau_calc_en == 1'b1) begin if (k1 > 0) // tau_calc <= tau_acc >>> 16; tau_calc <= tau_acc >>> 15; else tau_calc <= tau_coeff; end else tau_calc <= tau_coeff; end always@(posedge clk) begin // tau_acc <= (tau_coeff <<< 16) + k2 * tdpp_delta; //tau_acc <= (tau_coeff <<< 15) + k2 * tdpp_delta; tau_acc <= tau_acc0 + tau_acc1; end always @( posedge clk) begin tau_acc0 <= tau_coeff <<< 15; end always @( posedge clk) begin tau_acc1 <= k2 * tdpp_delta; end // main process of integrator always@(posedge clk or negedge reset) begin if(reset == 1'b0) begin : resetting resalt <= 64'sd0; resalt_i <= 64'sd0; //resalt_r <= 48'sd0; //buf2 <= 48'sd0; end else begin : calculating // input signal buffer fifo_amp[0] <= (data_in <<< 8) - r_base; fifo_amp[1] <= fifo_amp[0]; fifo_amp[2] <= fifo_amp[1]; // buf2 <= fifo_amp[0] * tau_coeff; if ((start_prev == 1'b1) & (start == 1'b0)) //resalt_i <= resalt_i + buf2 - sample_data; resalt_i <= resalt_a; else resalt_i <= resalt_b; resalt <= resalt_i + (fifo_amp[2] <<< 22); end end always @( posedge clk) begin resalt_a <= resalt_a + resalt0; //sample_data; end always @( posedge clk) begin resalt_b <= resalt_b + buf2; //sample_data; end always @( posedge clk) begin //reg_data_slow <= data_slow; resalt0 <= buf2 - data_slow; //sample_data; end always @( posedge clk) begin buf2 = fifo_amp[0] * tau_calc; end always@(posedge clk or negedge reset) if(reset == 1'b0) r_base <= r_base; else if ((start_prev == 1'b1) & (start == 1'b0)) r_base <= base; else r_base <= r_base; //// process for update slow data //always@(posedge clk or negedge reset) // if (reset == 1'b0) // sample_data <= 48'd0; // else // sample_data <= data_slow; // process for generate start vector always@(posedge clk) begin //front_start[0] <= start; //front_start[1] <= front_start[0]; start_prev <= start; end // process for calculate delta INT always@(posedge clk) begin delta <= resalt - int_prev; int_prev <= resalt; end // connect outputs assign data_out = resalt; assign int_out = resalt_i >>> 30; assign int_diff = delta >>> 30; assign tau_out = tau_calc; endmodule и то я изменил немного матемтику она не соответствует первоначальной (это видно в моем описании выше): if ((start_prev == 1'b1) & (start == 1'b0)) resalt_i <= resalt_i + buf2 - sample_data; else resalt_i <= resalt_i + buf2; я сделал вычисления в условиях независимыми, что есть не совсем правильным этот always я уберу - эти регистры будут инициализироваться по авлон ММ шине в одном модуле - в этот модуль будут приходить как входные данные (в моем варианте этот процесс уже закоментирован): // process for update constants always @(posedge clk_const) begin if (ready_const) case (addr_const) 6'd2: tau_coeff[15:0] <= data_const; 6'd3: tau_coeff[23:16] <= data_const[7:0]; 6'd23: tau_calc_en <= data_const[3];// customize[3] -> + 8 6'd25: begin k2[15:0] <= data_const; k2[16] <= 1'b0; end// coefficient (top_discriminator) 6'd26: begin k1[15:0] <= data_const; k1[16] <= 1'b0; end// base temperature (bottom_discriminator) default: begin tau_coeff <= tau_coeff; tau_calc_en <= tau_calc_en; k2 <= k2; k1 <= k1; end endcase end Буду рад конструктивным предложениям/мыслям по увеличению тактовой частоты хотя бы до 130-140МГц ...

-

Работа с case

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

напишите задачу в целом что необходимо реализвать? многим так будет проще помочь -

что за корку Вы хотите использовать? корка платная/бесплатная проверяли?

-

Спасибо...

-

Подскажите пожалуйста файл rsc_dec_extr_ram.v в каком архиве/проекте? их у Вас там много)))

-

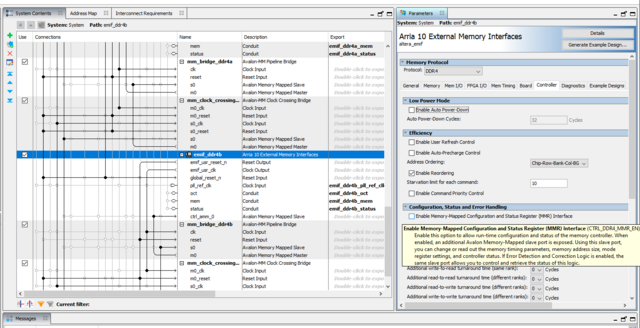

Спрашу еще раз (я не могу разобраться) Добрый день! Подскажи пожалуйста как подключить покупную планку памяти DDR4 (sodimm, udimm) к FPGA? как узнать тайминги? Распарсивание содержимого из eeprom (SPD (Serial Presence Detect)) не дает всех таймингов которые необходимо внести в External Memory Interfaces Intel Arria10. (возможно я парсер spd не правильный использовал) Может есть какое то другое решение? Прошу хотя бы намекнуть на путь ...

-

Подскажите пожалуйста - имеются ли у кого то парсер/декодер для вычитанных данных eeprom (serial presence detect (SPD)) ??? Serial Presence Detect (SPD) for DDR4 SDRAM Modules - документ(стандарт) во вложении

-

Можно сделать чтение процессором епром памяти The SPD EEPROM is accessed over a System Management Bus (SMB), which is a derivative of I2C. I'll use Intel's I2C master core in Platform Designer to connect to the SMB. This has two input signals for serial data and clock suffixed _sda_in and _scl_in, and two output signals also for serial data and clock suffixed _sda_oe and _scl_oe. These need to be connected to the SMB bidirectional DDR4 pins using tristate buffers. For example: wire i2c_sda_oe, i2c_scl_oe; assign DDR4B_SCL = i2c_scl_oe ? 1'b0 : 1'bz; assign DDR4B_SDA = i2c_sda_oe ? 1'b0 : 1'bz; niostest qsys0 ( .clk_clk (clk_100), .i2c_serial_sda_in (DDR4B_SDA), .i2c_serial_scl_in (DDR4B_SCL), .i2c_serial_sda_oe (i2c_sda_oe), .i2c_serial_scl_oe (i2c_scl_oe), .reset_reset (!reset_n_100) ); Варианты: 1. распарсить и вручную ввести данные в emif ddr4 контроллер 2. Попробовать использовать порт который выделен желтой подписью сообщением выше - записав по нему прчитанные данные PS таблица и описание регистров

-

был не внимателен, можно и наверное с использованием внешней логики которая будет читать и потом по авалон ММ писать в контроллер DDR4 (желтое на скрине)

-

в арии10 тоже пока это делается вручную (как я понял) Вначале тайминги с планки считываем по I2C подобному интерфейсу из eeprom (есть исключение) Затем считанные данные вручную ввести в корку emif PS но Zynq MPSoC вроде уже позволяет... Иначе не знаю как работать если планка памяти ddr4 (sodimm, udimm) будет покупная, а плата собственного "приготовления"... Может есть другие варианты?

-

может и скорее всего так оно и есть. Может ли FPGA (intel arria10) автоматически применить настройки(тайминги) из eeprom? или надо делать отдельно вычитку настроек памяти и самому их записывать в emif IP core? UPdate Разобрался...

-

Добрый день! Подскажите пожалуйста как подключить покупную планку памяти (sodimm, udimm) к FPGA? как узнать тайминги? Ответ нашел здесь https://www.ixbt.com/mainboard/spd.shtml Может ли FPGA (intel arria10) автоматически применить настройки(тайминги) из eeprom? или надо делать отдельно вычитку настроек памяти и самому их записывать в emif IP core?

-

всем добрый день есть пример с hdr видео и пример проекта "Silver Award : Real-time HDR video" https://www.innovatefpga.com/cgi-bin/innovate/teams2018.pl?Id=EM076 для платы https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=1046 скачать диск можно http://download.terasic.com/downloads/cd-rom/de10-nano/ где в примерах будет проект hdr видео где используется 2 камеры гитхаб https://github.com/innovatefpga/2018-EM076 здесь прием видео с камер и для вас возможно предварительная обработка... вот еще интересный проект на гитхабе https://github.com/davemuscle/camera_journey для передачи на ПК можно использовать https://www.ftdichip.com/old2020/Products/ICs/FT600.html там в режиме FIFO есть даже пример для FPGA

-

Интересная у Вас работа)

-

Моя реализация не позволит обеспечивать CDC... Надо немного по другому описать/добавить логику...

-

Понял спасибо Я просто выделил несколько файлов и перетащил...

-

Добрый день. Здесь выложил несколько файлов В результате для скачивания получилась "цельная строка": Мне кажется если файлы для скачивания будут представлены в виде столбца будет лучше

-

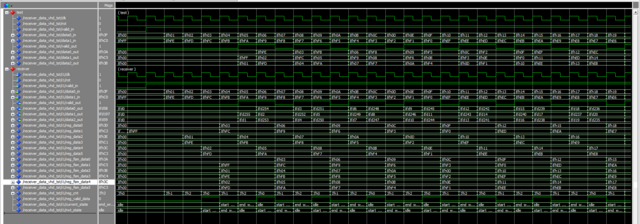

des00 за намек спасибо. Ниже скрин симуляции: файлы реализации и тестбенча во вложении wave.do c.do receiver_data.vhd receiver_data_vhd_tst.vhd Решение я уже привел, я не знаю как по другому пояснить задачу, которую мне надо было реализовать... Сформулируйте Вы - интересна Ваша формулировка моей задачи...

-

Не понял Вас ... Если можно поясните пожалуйста Спасибо, попробую

-

pipeline 2 bytes to 3 bytes

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день Что-то я не могу придумать как сделать. Мне надо принимать паралельно 2 байта, а выдавать паралельно 3 байта: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity receiver_data is generic ( BYTE_WIDTH : integer := 8; BYTES : natural := 1 ); Port ( clk : in std_logic; rst : in std_logic; valid_in : in std_logic; data0_in : in std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data1_in : in std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); valid_out : out std_logic; data0_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data1_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); data2_out : out std_logic_vector((BYTE_WIDTH*BYTES-1) downto 0); ); end receiver_data; Подскажите пожалуйста как такое реализовать?