Поиск

Показаны результаты для тегов 'intel'.

-

Привет всем! У меня накопилось много редких микросхем. Сам электроникой не занимаюсь, только продаю её. Это излишки, которые накопились за какое-то время. Все детали новые, не распечатанные. Продаю как частное лицо, готов отдать каждое наименование ниже рынка, все цены по согласованию. Во вложении перечень. Если кому-то что-то интересно, пишите в личку. Излишки.docx

-

Прошивка ПЛИС с помощью МК

mysol опубликовал тема в Работаем с ПЛИС, области применения, выбор

Друзья, здравствуйте! Подскажите, пожалуйста, можно ли заливать прошивку в ПЛИС из флеш памяти контроллера? Какие используются механизмы? Нет ли примеров/туториалов? В частности в Cyclone 10 LP. Спасибо! -

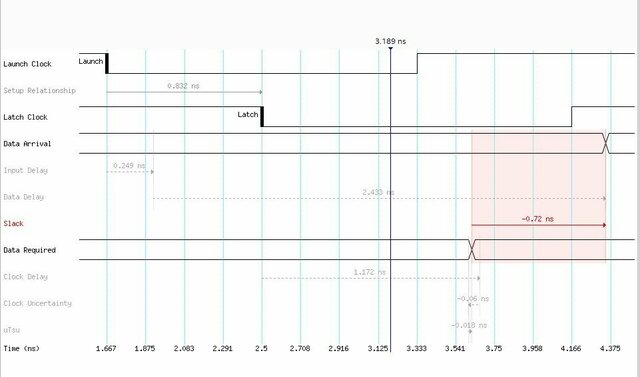

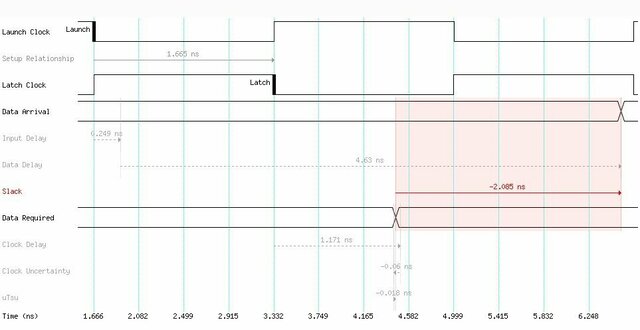

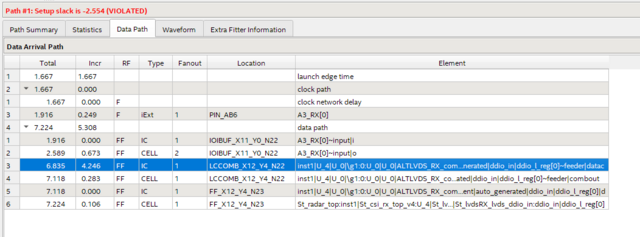

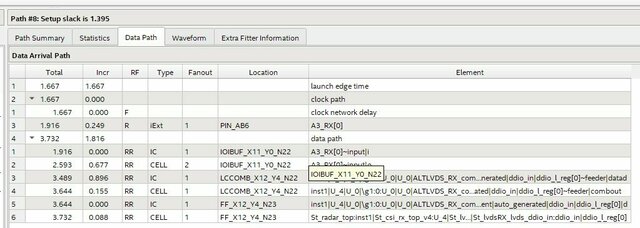

Добрый день! В проекте есть приемник CSI2 на частоте на частоте 300 МГц, 600 Мбит/с в режиме ДДР соответственно. Для приема используется блок altlvds_rx c десериализацией 8. Входной клок заведен на отдельную PLL, и c[0] используется чтобы латчить входные данные. Данные center-aligned, задержки прописаны по методичке ddr-timing-cookbook. В PLL ставлю нулевую задержку. Собираю, смотрю тайминги Слак по setup. Напрашивается добавить фазы в PLL. Добавляю 90гр и смотрю опять Фаза накрутилась, но квартус зачем-то навалил и задержки по данным. Сперва решил, что он куда-то регистры разместил далеко, залокейтил их как в первой сборке, но оказалось он впихнул на вход комбинационную логику которая делает DOUT = DIN и тупо добавляет задержки данных. Ставил 120гр фазы, квартус уменьшает задержку комбинационной логики, фазы PLL хватает чтоб слак по setup убрать, но теперь надо бороться с холдом... ок, вижу что там нужно вписать теперь мультицикл, так как фронт вылез за launch, вписываю, собираю - он опять увеличил комбинационную задержку так что и по сетапу прослакано... Можно ли сделать так, чтобы квартус не довавлял/убавлял по свой прихоти эту комбинационную логику пустую? Или я что то не так трактую? Вот таблицы DataPath из репорта до и после добавления мультицикла. +3.5 нс на ровном месте Я не специалист по заданию ограничений но может как-то это решается? Если нет, то каким путем нужно идти, чтобы добиться сходимости таймингов? PS Проект достался по наследству, он как-то работал в железе до тех пор пока не потребовалось сделать пару изменений. После сборки данные перестали приниматься. Оказалось нет входных констрейнов. Я немного слышал о ПЛИС и решил, что смогу быстренько подчинить, а он как уж на сковороде

- 11 ответов

-

- intel

- cyclone 10 lp

-

(и ещё 1 )

C тегом:

-

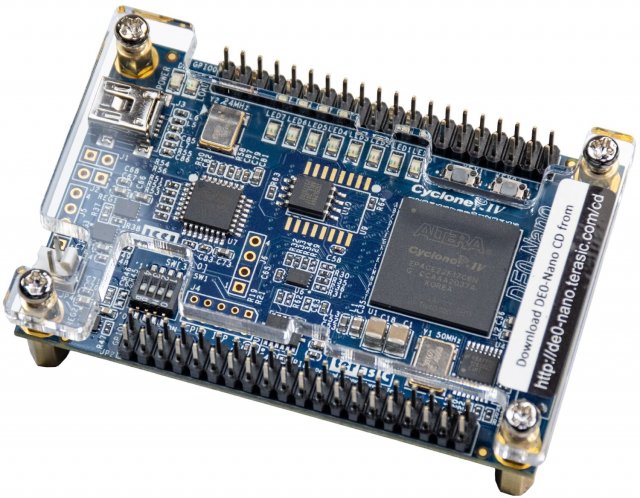

Отладочная плата Terasic DE0-Nano с ПЛИС Cyclone IV (Москва)

pavlovconst опубликовал тема в Продам

Продаю свою отладочную плату. Состояние - идеальное, все работает. Комплект: Без коробки, кабелей, стоечек и акриловой накладки. USB-Blaster интегрирован на плате, поэтому идет в комплекте ;) Цена 9999 р. Для сравнения, цены в магазинах: https://www.chipdip.ru/product/de0-nano https://www.terraelectronica.ru/product/675579 Технические характеристики: -

Макро Групп – официальный дистрибьютор HiTech Global, производителя плат на ПЛИС Xilinx и Intel FPGA (Altera) Подробнее

-

- плис

- fpga xilinx

-

(и ещё 4 )

C тегом:

-

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Ищу сотрудника. СПБ.

PLISovik опубликовал тема в Предлагаю работу

На полную занятость ищем сотрудника. Санкт-Петербург. Требуемый опыт работы: 3–6 лет Полная занятость, полный день Обязанности: Определение требований к проекту ПЛИС; Определение методик и принципов разработки; Разработка архитектуры проекта ПЛИС, функциональных и структурных моделей; Разработка проектов ПЛИС; Кодирование на языке описания аппаратуры; Создание симуляционных моделей; Участие в процессе верификации разработанных проектов; Участие в испытаниях целевого оборудования; Сопровождение изготовления образцов изделия; Участие в проведении испытаний; Участие в проведении работ по сертификации. Требования: Высшее профессиональное (техническое) образование; Опыт работы с ПЛИС фирм XILINX, Altera (Intel); Знание принципов цифровой схемотехники; Знание САПР: Quartus; Vivado Design Suite; Знание System Verilog/Verilog или VHDL; Опыт работы с высокоскоростными интерфейсами; Опыт моделирования, верификации и отладки проекта; Опыт написания testbench; Практические навыки использования Git/SVN. Знание английского языка в объеме, необходимом для чтения и понимания технической литературы по направлению деятельности. Плюсом является: Опыт разработки на ПЛИС семейства Altera: Arria10, Cyclone10 и ПЛИС Xilinx: Zynq-7000, Virtex-7, Kintex-7; Знание современных сетевых технологий Ethernet, STM, SDH, OTN, DWDM; Опыт работы с интерфейсами DDR2/DDR3/DDR4, PCI Express, 1G/10G/100G Ethernet; Знание криптографических алгоритмов и протоколов; Опыт программирования на C. Условия: Оформление в соответствии с ТК РФ, социальные гарантии (больничный, ежегодный оплачиваемый отпуск). З/п по результатам собеседования. От 100 тыс. руб Контакты: [email protected]- 1 ответ

-

- fpga ddr3/ddr4 pcie usb

- fpga

-

(и ещё 2 )

C тегом:

-

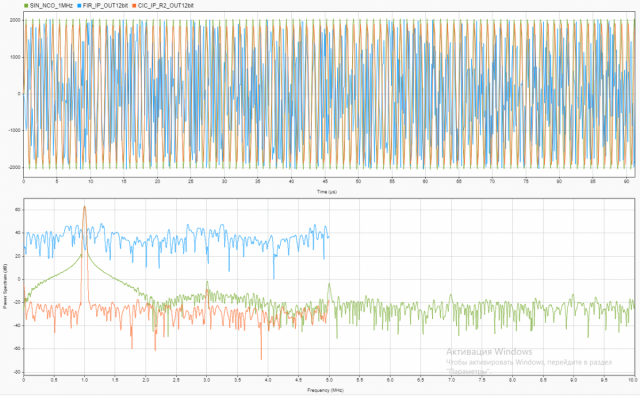

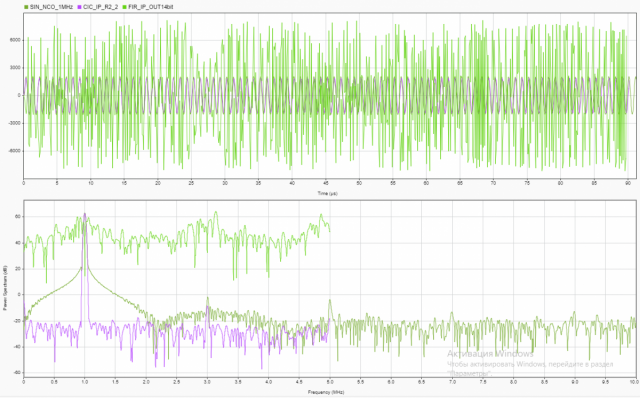

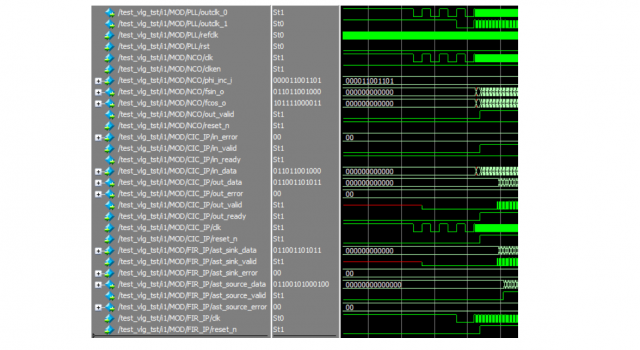

Всем доброго времени суток! Никогда ранее не обращался на форумы, но в данной ситуации ответа на свой вопрос в Сети не смог найти. Кратко введу в курс дела. Использую: 1) САПР для проектирования на ПЛИС - Quartus Prime Standart Edition 18.0.0 build 614 2) САПР для симуляции Verilog кода - ModelSim INTEL FPGA Starter Edition 10.5b Revision: 2016.10. (Данная версия поставляется вместе с Quartus на сайте https://fpgasoftware.intel.com/) 3) Для проверки результатов симуляции использую MATLAB 9.8 (2020a). В MATLAB на данный момент использую Signal Analyzer для просмотра спектра сигналов полученных в результате работы программного(-ых) модулей. Все программные модули пишу на Verilog (начал его изучать первым, на данный момент с VHDL знаком лишь отчасти). Опыт. Увлекся ПЛИС на 3 курсе университета. Специальных предметов по тематике ПЛИС на моем направлении не было, поэтому изучал все по видео/статьям/книгам/форумам. Увлечение переросло в желание написать диплом по ПЛИС. Таким образом, знаком с ПЛИС в районе 1,5 лет, из которых в учебное время не было слишком серьезных задач, а если и были, то решались они для моего уровня так, как мог их решить (костыли и тд). Вторым увлечением была ЦОС, в которой знания и опыт черпал из тех же источников, что и по тематике ПЛИС. Сейчас же появилась задача следующего плана. Занимаюсь QPSK демодуляцией. Разделим данный процесс на 3 этапа 1) Использование гетеродина для переноса на более низкую частоту. Тут все как обычно. Гетеродин и два умножителя для двух каналов (синфазного и квадратурного). 2) Децимация. Перед непосредственно реализацией дециматора окунулся в эту тематику. Знаком с статьей Hogenauer'a, а также с другой информацией на эту тему (ru.dsplib.org, dspguru.com), а также информацией с других сайтов. Имея начальное представление решил попробовать сделать, в итоге все получилось и CIC-фильтр работает так, как и ему положено. 3) Фильтрация. Компенсация искажений АЧХ после CIC-фильтра и последующая низкочастотная фильтрация. Так как в качестве САПР для проектирования на ПЛИС я использую Quartus, то было решено не использовать MATLAB без необходимости и решить задачу децимации и фильтрации с помощью встроенных в Quartus IP-ядер, а именно CIC и FIR II. В процессе работы с ядром проектирования CIC фильтра, есть возможность (ядро само сделает все необходимые файлы) сделать примерный вариант CIC фильтра, учитывая имеющиеся параметры. Одним из файлов является код MATLAB, который позволяет рассчитать коэффициенты компенсирующего FIR фильтра. В процессе выполнения скрипта задается количество и "битность" коэффициентов фильтра, а также - "FIR filter sample rate in Hz before decimation (80e6 as default): 20e6 (я указал 20 МГц)", что говорит нам о частоте дискретизации входного сигнала ПЕРЕД децимируюшим фильтром; - "FIR filter cutoff frequency in Hz (4e6 as default): 1.2 МГц". Частота среза компенсирующего FIR фильтра (в моем случае 1.2 МГц). После чего скрипт формирует текстовый файл с коэффициентами корректирующего FIR фильтра, которые загружаются позже в ядре FIR II. Исходя из коэффициентов ядро автоматически строит АЧХ,ФЧХ и ИХ получившегося фильтра. И вот мы дошли до самой сути моей проблемы. Все идет хорошо ровно до момента с компенсирующим FIR фильтром. По временным диаграммам в ModelSim (скриншот прикрепил) работа NCO, CIC и FIR фильтра прекрасна, то есть они работают и никто из них не простаивает и т.д. Ввиду того, что очень долго ковыряюсь с этой проблемой была сделана простая схема (скриншот из RTL Viewer из Quartus'а прикрепил), которая подает синусоиду с частотой 1 МГц и частотой дискретизации 20 МГц на вход CIC фильтра. Настройки CIC ядра: - Filter type - Decimator; - Number of Stages - 5; - Differential Delay - 1 cycles - Rate change factor - 2; - Input data width - 12 bit - Output Rounding Method - Hogenauer Pruning; - Output data width - 12 bit. Имея такие настройки CIC фильтр отлично отрабатывает и не искажает спектр в требуемом 1 МГц (скриншот прикрепил). Далее исходя из этих настроек был сделан скрипт, в котором задавал следующее: - Number of filter coefficients (31 as default): *оставил default значение*; - FIR filter sample rate in Hz before decimation (80e6 as default): 20e6; - FIR filter cutoff frequency in Hz (4e6 as default): 1.2e6 - Number of bits to represent the filter coefficients (16 as default): *оставил default значение*. После этого были сформированы коэффициенты и теперь надо настроить ядро FIR II. Настройки в нем задавал следующие: - Filter Type - Single Rate; - Interpolation / Decimation Factor - 1; - Clock Rate - 10 MHz; - Input Sample Rate (MSPS) - 10; - Coefficient Width - 16 bits; - Input Width - 12 bit; - Output Width - 14 bit; - Specifies whether to truncate or saturate the MSB - Truncation (аналогично для такого же параметра, но для LSB); - MSB Bits to Remove - 10; - LSB Bits to Remove - 9. Если не обрезать MSB и LSB, то на выходе ядро рекомендует ширину в 33 бита, что много и существенной разницы между 14 и 33 битами я не увидел (при увеличении доли MSB в сигнале растет мощность в дБ на спектре и все). Да, я пробовал 33 бита, однако желательно уходит от такой большой разрядности. Имея такие настройки, мы имеем следующую картину в спектроанализаторе Signal Analyzer (скриншот прикрепил). Как видно из рисунков спектр после FIR фильтра больше похож на шум, чем на что-то осмысленное. Промучавшись долго с этим ядром я решил, что необходимо попробовать сделать CIC и FIR в MATLAB и сравнить результат. При даже меньшей разрядности FIR фильтр выдал необходимый мне спектр и отработал так, как я и хотел (аналогично и CIC) (скриншот сравнения MATLAB'овского компенсирующего FIR и генерируемого ядром не смог прикрепить, однако и видно даже на первый взгляд, что разница имеется). Таким образом, вопрос. Знает ли кто-то в чем заключается проблема с FIR II ядром и почему (вроде бы нигде не ошибаясь) я получаю такой отрицательный результат? Заранее благодарю за уделенное время и оказанную помощь Что получилось загрузить

-

Доброго времени суток! Поставили быструю задачу: сделать энергонезависимую плату с ПЛИС на борту, как расширитель для последовательного интерфейса (читай регистр сдвига). На вход приходит "псевдо SPI" (протокол похож, но работает по-своему плюс дополнительная минимальная логика). На плату решили поставить MAX 10 из-за его энергонезависимой памяти прошивки и наличия ADC (который в результате не пригодился). Проблема в том, что никто не хочет ставить генератор опорной частоты. Есть конечно вариант задействовать внутренный генератор, но там очень неточная частота от серии к серии, плюс входной интерфейс имеет частоту порядка 20MHz, а внутренний генератор даёт от 60 до 110 MHz. Сначала была идея сделать умножитель частоты (или работать по обоим фронтам) и дальше как обычно разложить логику. Но всё же здравый смысл подсказывает, что не нужно изобретать велосипед и затактировать всю синхронную логику от входного клока SPI, а остальная комбинаторика будет себе подвешена наобум. Проблема что я никогда не имел дел с синхронным интерфейсом с такими "дырками" (частота может быть от 1kHz до 20MHz, при этом установка выходных значений должна быть синхронной - разбег до десятых микросекунд) и честно говоря понятия не имею как констрейнить. Буду благодарен за любой гайд или ссылку. Для понимания задачи, нужно реализовать такую синхронную логику + комбинаторику: