rloc

Модератор-

Постов

3 249 -

Зарегистрирован

-

Победитель дней

14

Весь контент rloc

-

Брал кто нибудь TCXO с Алиэкспресс ?

rloc ответил TOG тема в Схемотехника

Как мне показалось, речь об определенном наименовании и фирме. -

Брал кто нибудь TCXO с Алиэкспресс ?

rloc ответил TOG тема в Схемотехника

https://www5.epsondevice.com/en/products/tcxo/tg5035ce.html -

Там же по библиотекам

-

На этом участке уровень шума (фликкер) не зависит от обратных связей и определяется самим усилителем, режимом его работы Full/Low Power. В такой ситуации - или менять сам усилитель, или параллелить несколько 2/4/8, соответственно с выигрышем 3/6/9дБ по напряжению шума. Для участка 0.01Гц и ниже возможно потребуется термостабилизировать схему.

-

Ethernet 2.5G PHY

rloc ответил rloc тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Задам другой вопрос. Кто может поделиться даташитом на AQR113/114/115? -

Ethernet 2.5G PHY

rloc опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Такой вопрос: бывают ли в природе phy 2.5GBASE-T с host-интерфейсом со скоростью 2.5Gb на линию и ниже? Допустим с интерфейсом TBI. В FPGA Xilinx US+ не осталось лишних трансиверов. Немного погуглил, вроде есть внешние SERDES, но с потреблением более 200мВт или в продаже найти сложно. -

Работа сайта и сервера

rloc ответил admin тема в Новости и обсуждения сайта и форума

Не хватает терпения смотреть на крупные шрифты, кнопки, листать бесконечные страницы. Вопрос был скорее риторический, хозяин - барин. У себя на телефоне принудительно сделал, чтобы всем сообщал что он десктоп и не понимаю, почему разработчики с упорством борются с блокировками мобильности. -

Работа сайта и сервера

rloc ответил admin тема в Новости и обсуждения сайта и форума

Форум образца 10-летней давности разве был плох для чтения/редактирования с мобильника? На мой взгляд, любая мобильная тема уступает по удобству. Всегда был новатором, но что касается оформления форума хочется побыть немного консерватором. -

Категорически против "спасибо", "лайков" и прочей мишуры. Откровенно отвлекает от обсуждения. На форуме огромное количество хороших специалистов, которые редко пишут, но от этого ценность их сообщений нисколько не меньше. Пусть каждый лично составит "рейтинги" на основе своего опыта общения.

-

До 24г планов нет.

-

Шансов никаких. MacOS отсутствует в списке доступных операционных систем. Есть призрачные шансы у Arm v8 RHEL, выборочных продуктов, и скорее не PCB софта.

-

Работа сайта и сервера

rloc ответил admin тема в Новости и обсуждения сайта и форума

Развалился Классический стиль на Mozilla FF 100.0 W10, работает пока только Мобильный. -

Дело наживное, работаю со всеми ПЛИС и с Xilinx и с Altera. Серия Artix7 - одна из наиболее беспроблемных, а Fudan считайте полной копией. После воронежских ПЛИС, любая покажется совершенной. Если денег не жалко, есть такие платы на Ali.

-

Формально платы с 484 фудановским артиксом есть, но наверное для автора темы не совсем актуальны при отсутствии PCIe разъема. Вот с шагом - есть засада, тоже ожидал 1.0мм. Можно копнуть среди инженерных образцов у Xilinx, мне кажется были там корпуса с 0.8мм. Можете закинуть на файлообменник доки с распиновкой и габаритами?

-

Присоединяюсь к рекомендации. Вроде по последнему семинару доступны для заказа. Более детально - к Эпсилон (С.-Петербург) и Феникc (Ижевск).

-

Могу только предположить, что плата собрана на совместимом с FTDI контроллере и поэтому: https://wiki.sipeed.com/hardware/en/tang/Tang-Nano-Doc/install-the-ide.html#Programmer-application Этот кабель (FT232H) определяется в Gowin.

-

Микросхеме лет 7. Хороша для квадратурной модуляции, живьем наблюдал подавление зеркального канала и гетеродина лучше 60дБ. По потреблению ядра DDS думаю никто не подскажет. А зачем? Разрядность ЦАП 10бит

-

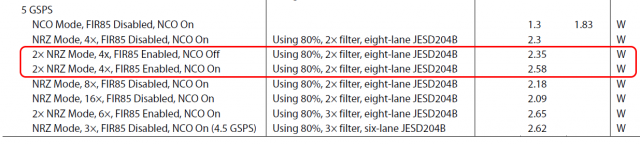

Аналоговая часть остается в активном состоянии во всех случаях, приведенных в таблице. Дело в том, что указанная микросхема представляет из себя ЦАП + встроенный DDS + набор интерполирующих фильтров. 0.23Вт - это потребление именно цифровой части DDS. Если интересно, то из этой таблицы видно, что потребление аналоговой части ЦАП составляет около 1Вт, цифровой части фильтра FIR85 (возможно вместе с интерфейсом JESD204) - 1.35Вт. Поэтому и пишу подробно о составе модуля DDS. Как можете видеть, потребление достаточно низкое и таблица LUT скромного размера, а основное потребление приходится на аппроксимацию по ряду Тейлора в виде 2-х умножителей, но опять же оно небольшое (0.23Вт), особенно на фоне интерполирующих фильтров.

-

Виталий, возьмите для сравнения более современный AD9162-64. Табл. 3 стр. 7 из даташита: Где потребление DDS (=NCO) составляет около 0.23Вт на фоне общего потребления ~2.5Вт. Учитывая генерацию DDS на частоте 5ГГц, количество одновременно работающих ядер должно быть около 8-16 шт, в зависимости от технологии CMOS. Из своего опыта реализации DDS на FPGA, ресурсы на одно ядро, при динамике ~120дБ по спурам, составляют: одна таблица LUT 512x32 и два умножителя 18x18 (по основным ресурсам). Думаю, можно отдельно взять ЦАП и RS-триггер, и потом просуммировать. Выход RS-триггера просуммировать с выходом ЦАП. Для простоты рассмотрения.

-

JLCPCB - карты UnionPay

rloc ответил IgorAVR2 тема в Изготовление ПП - PCB manufacturing

Насколько я понимаю, блокировка идет по БИНу карты (первые пять цифр), а он у всех карт банка одной платежной системы одинаковый. -

Согласование логических уровней 1.8В и 3.0В

rloc ответил Alt.F4 тема в Схемотехника

Не вижу общей базы, все выводы плавают. Но дело даже не в этом, насытить биполярный транзистор можно в любом включении и схема выше не исключение. С LTspice слабо знаком, не знаю насколько корректно он умеет симулировать задержку при насыщении, если она вообще фигурирует в модели транзистора. Вы бы написали, зачем нужны сложности с дискретными элементами? -

Согласование логических уровней 1.8В и 3.0В

rloc ответил Alt.F4 тема в Схемотехника

Процесс рассасывания неизбежен после насыщения, даже при закорачивании базы. -

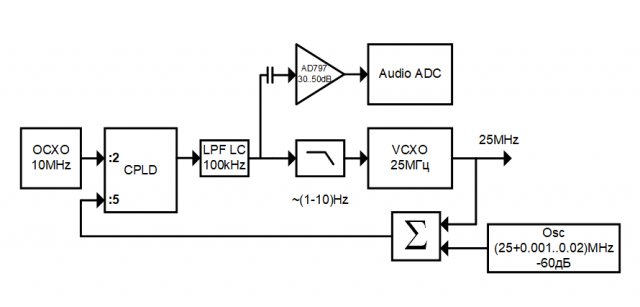

Примерно так: По материалам, аппноута AN1639 an1639.pdf ФД с делением, но и частота, по которой калибровка, тоже делится и в относительных единицах ФШ должен иметь одинаковое смещение. Прошу еще раз проверить.