rloc

Модератор-

Постов

3 197 -

Зарегистрирован

-

Победитель дней

12

Весь контент rloc

-

-

Ошибка кроется на системном уровне. Для умножения без потерь, шумы ГУН должны быть лучше шумов умноженной опоры 10МГц за пределами ПИ-фильтра. А ГУН на CPLD, пусть и с кварцевым резонатором, сделать малошумящим не получится, как по причине высоких собственных шумов, так и избыточного набега фазы из-за большой задержки.

-

Признаюсь не работал с этим ЦАП. Можете сказать в каком режиме работаете с JESD? Подкласс 0/1? Используете SYSREF с привязкой к тактовой частоте ЦАП?

-

Грустно смотреть на Charles Tumbaga, можно заменить на общую фотографию разработчиков?

-

Давно применяем в L-диапазоне Type-N на мощностях 4кВт, правда импульсных, средняя 80Вт. Разъемы холодные с любым диэлектриком.

-

Можете продублировать через скриншот или сохранение страницы? Нет доступа после регистрации.

-

Как я понял, автор пытается засинхронизировать приемник и передатчик одним клоком. Тогда зачем восстанавливать клок, если его можно передавать со стороны передатчика/приемника напрямую на высокой частоте, а не пытаться умножать на PLL из низкой частоты?

-

На вход АЦП нужно подать перестраиваемую частоту, проверить по 5-6 точкам, а в режиме измерения IMD - две частоты с небольшим разносом, дельта = (1-1000) кГц, уже сложнее собрать коллекцию кварцевых генераторов. Кратко резюмируя, генератор с низкими шумами в диапазоне до 2ГГц нужен как хлеб и вода. Александр, попробуйте найти на рынке лабораторный генератор с -170дБн/Гц@100МГц. Linkedin заблокирован у нас Роскомнадзором ) Уж не знаю чем он помешал, чтобы зарубежные компании не утаскивали ведущих российских специалистов )

-

Расчет простой, допустим есть АЦП с СПМШ около -160дБн/Гц при подаче синуса, близкого к полной шкале. А такие АЦП есть, -157дБн/Гц точно. Для того, чтобы опорные генераторы не повлияли на результат измерения, они должны на 20дБ быть ниже по шумам, относительно собственного шума АЦП. Да, есть способы вычитания шумов опорных генераторов, но сама методика более сложная и вызывает много спорных вопросов при анализе результата. Если есть возможность сразу "в лоб" измерить, такой путь предпочтителен.

-

Про него и речь, он шумит. Принимается, зачетный делитель, пусть и до 32 коэффициент деления. И на 2ГГц пишут -164дБн/Гц, фантастика. Подумываю, не слишком ли скромно -170дБн/Гц, может поднять до -175дБн/Гц? ) Вот уж действительно рекомендован для тестирования АЦП.

-

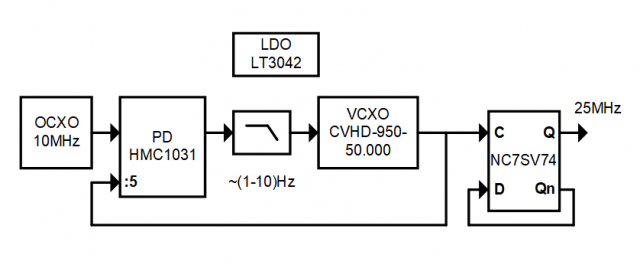

Такие есть на СВЧ и не мало, предполагаю проблема в оконечном триггере. Еще такой вопрос: кто применял LTC6953? Достаточно близко к -170дБн/Гц, потребление 2Вт, но что делать.

-

Высокое сопротивление (низкий ток потребления). Т.е. в первую очередь тепловые шумы, про дальние отстройки.

-

Со своей стороны кину клич (вопрос ко всем), что можно придумать для малошумящего деления частоты с 2ГГц и ниже? Коэффициенты деления 2, 4, 8 ..., чтобы расширить диапазон вниз до единиц кГц. Для тестирования современных АЦП не хватает -170дБн/Гц по ФШ/АШ на 100МГц чтобы достоверно оценить SNR. Известный нам регенеративный делитель пока отложим на полочку, полоса узкая. Параллельное включение нескольких делителей принимается, но с пометкой сложности синхронизации. Какие еще можно предложить варианты?

-

Xilinx IBIS Ultrascale+

rloc опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, у кого есть доступ или верифицированный корпоративный аккаунт, помогите с моделями IBIS и IBIS-AMS на всю серию Ultrascale+. Надеюсь там должны быть модели на новые Artix US+, включая S4P модели корпусов. В крайнем случае подойдут от Kintex US+ или Zynq US+, чтобы от чего-то отталкиваться. Хочу исследовать характеристики GTH и GTY трансиверов и влияние корпусов. https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-ami/ultrascale-plus-devices.html https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-models/ultrascale-plus-fpgas.html https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-models/zynq-ultrascale-plus-mpsoc.html В моем случае, при отправке запроса на доступ к моделям сначала приходит письмо с просьбой ожидания решения до 2 рабочих дней, а потом: Но при этом на загрузку последних Vivado/Vitis ограничений нет. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Я бы сказал на все 400% -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Да, что-то не сходится. По логике нужно развернуть трансформатор. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

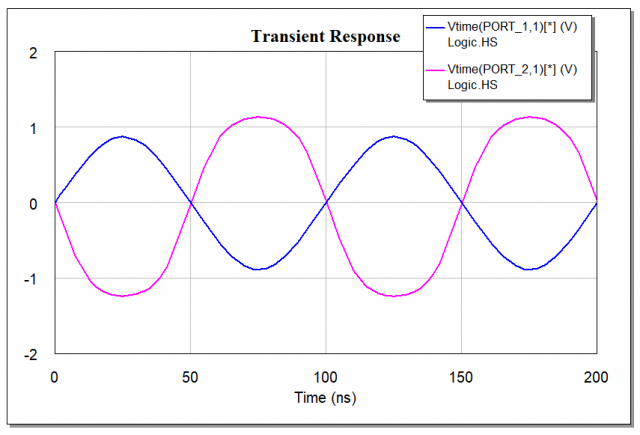

Взял топологическую модель от производителя, не тянет 10x усиление на 50 Ом, максимум раза в 2, не хватает крутизны хар-ки. Но как повторитель-ограничитель с повышением крутизны фронтов вполне подойдет: Можно конечно включить параллельно 3 инвертора, но с MMIC проще. Примерно что-то ERA-3SM+ должен подойти, Дарлингтон на InGaP (на насыщению немного лучше Si и SiGe), с усилением 20дБ на 10МГц (10 раз по напряжению). С низкоомным резистором в обратной связи сопротивление приближается к активному, не стал приводить, и скорее с некоторым повышением КШ. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

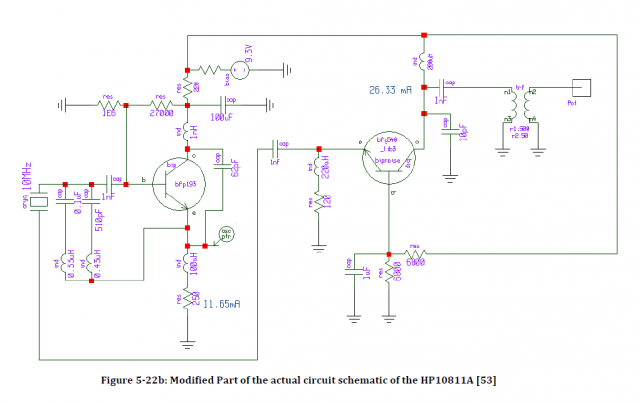

Больше тянет на кандидатскую, по моему представлению. Слабовата для докторской, много заимствованного материала и мало предшествующих печатных трудов. По большому счету прослеживается "рука" Ульриха Роде, научного руководителя ) Для уровня несущей не пишут в единицах плотности мощности, потому что от плотности по частотной оси он не меняется. Формально мог записать и -10дБм/Гц, тоже справедливо. И что интересно, в результате вычитания получаются дБн/Гц, при размерности слагаемых дБм и дБм/Гц. Такой казус. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

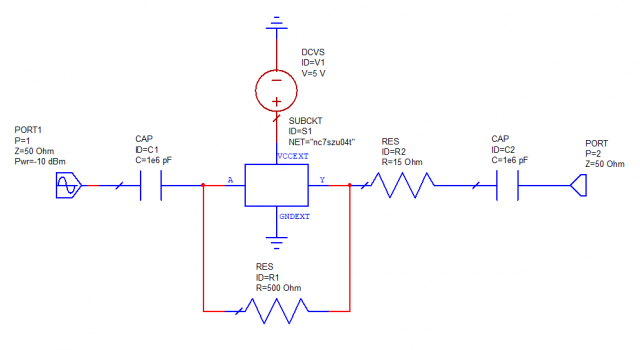

На входе у Вас сигнал с амплитудой 0.1В или что тоже самое -10дБм. Уровень теплового ФШ составляет -177дБм/Гц. Вычитаем одно из другого, получаем -167дБн/Гц - наилучший уровень ФШ, который может быть у источника. Поэтому сильно стараться нет смысла. Низкий вносимый шум получают с буфером на одном транзисторе примерно так: Если вырвать отдельно буфер, то нужно добавить трансформатор 4:1 на вход по сопротивлению, и на выходе можно такой же использовать. Более детально схема оптимизируется в SPICE-программе: по рабочей точке, отсутствию насыщения и согласованию. Оригинал источника: https://opus4.kobv.de/opus4-btu/files/5138/Anisha_Apte.pdf Автор статьи - Аниша, девушка, победитель студенческого конкурса на IMS2016 с призовым фондом. Схему можно дальше развивать в сторону каскодного построения с одним или двумя дополнительными транзисторами. Мне кажется, при входном уровне 0.1В не стоит сильно заморачиваться, логический элемент nc7szu04 имеет собственный КШ на уровне 1-2дБ, как большинство полевых транзисторов. -

Для того, чтобы воспользоваться готовой программой управления, меньше забивать голову распределением ресурсов, удаленный рабочий стол X11 на котором можно наблюдать ход выполнения программы.

-

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Да уж, не заметил, что мы в разделе ОУ. Значит ничего другого не подойдет. Автору, ссылка на внутренности MXO37/14D и схема. Буфер - nc7szu04, частота 80MHz, выход - синус 10дБм typ (1В на 50Ом) при питании 4-5В. На 10МГц в 10 раз усилит. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Если взять конкретно nc7svu04 - это пара комплементарных CMOS транзисторов, сложно назвать "операционником". Без "u" - с дополнительным буферным каскадом. В ОУ транзисторов значительно больше, и больше количество последовательных каскадов. Главный вопрос зачем? Чтобы сохранить синусоидальную форму сигнала? Помню Вашу схему кварцевого генератора ) Приводил молодым дарованиям в качестве примера грамотного проектирования. Наилучшие результаты в буферном усилении показывают простые схемы на BJT с ОБ и низким входным сопротивлением (в каком-то смысле часть CFA). Но поскольку в теме нет высот типа -190дБн/Гц, то не хочется углубляться в тему.