rloc

Модератор-

Постов

3 153 -

Зарегистрирован

-

Победитель дней

12

Весь контент rloc

-

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Я бы сказал на все 400% -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Да, что-то не сходится. По логике нужно развернуть трансформатор. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

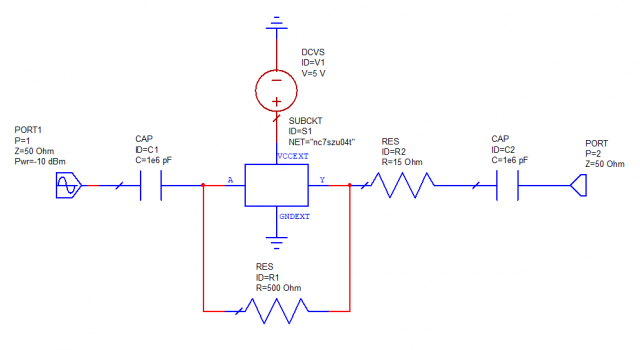

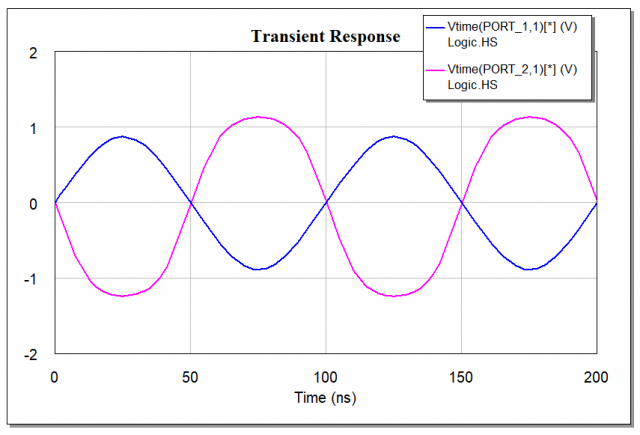

Взял топологическую модель от производителя, не тянет 10x усиление на 50 Ом, максимум раза в 2, не хватает крутизны хар-ки. Но как повторитель-ограничитель с повышением крутизны фронтов вполне подойдет: Можно конечно включить параллельно 3 инвертора, но с MMIC проще. Примерно что-то ERA-3SM+ должен подойти, Дарлингтон на InGaP (на насыщению немного лучше Si и SiGe), с усилением 20дБ на 10МГц (10 раз по напряжению). С низкоомным резистором в обратной связи сопротивление приближается к активному, не стал приводить, и скорее с некоторым повышением КШ. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Больше тянет на кандидатскую, по моему представлению. Слабовата для докторской, много заимствованного материала и мало предшествующих печатных трудов. По большому счету прослеживается "рука" Ульриха Роде, научного руководителя ) Для уровня несущей не пишут в единицах плотности мощности, потому что от плотности по частотной оси он не меняется. Формально мог записать и -10дБм/Гц, тоже справедливо. И что интересно, в результате вычитания получаются дБн/Гц, при размерности слагаемых дБм и дБм/Гц. Такой казус. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

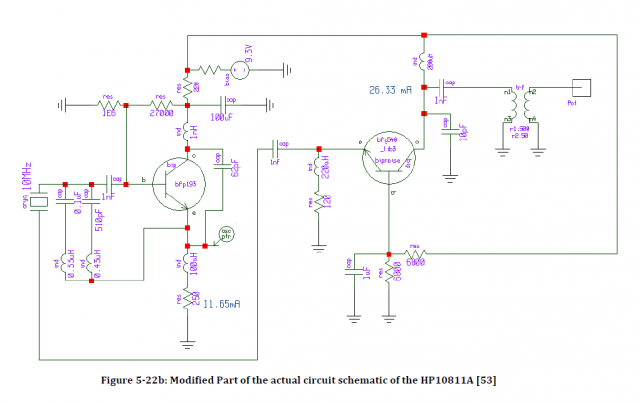

На входе у Вас сигнал с амплитудой 0.1В или что тоже самое -10дБм. Уровень теплового ФШ составляет -177дБм/Гц. Вычитаем одно из другого, получаем -167дБн/Гц - наилучший уровень ФШ, который может быть у источника. Поэтому сильно стараться нет смысла. Низкий вносимый шум получают с буфером на одном транзисторе примерно так: Если вырвать отдельно буфер, то нужно добавить трансформатор 4:1 на вход по сопротивлению, и на выходе можно такой же использовать. Более детально схема оптимизируется в SPICE-программе: по рабочей точке, отсутствию насыщения и согласованию. Оригинал источника: https://opus4.kobv.de/opus4-btu/files/5138/Anisha_Apte.pdf Автор статьи - Аниша, девушка, победитель студенческого конкурса на IMS2016 с призовым фондом. Схему можно дальше развивать в сторону каскодного построения с одним или двумя дополнительными транзисторами. Мне кажется, при входном уровне 0.1В не стоит сильно заморачиваться, логический элемент nc7szu04 имеет собственный КШ на уровне 1-2дБ, как большинство полевых транзисторов. -

Для того, чтобы воспользоваться готовой программой управления, меньше забивать голову распределением ресурсов, удаленный рабочий стол X11 на котором можно наблюдать ход выполнения программы.

-

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Да уж, не заметил, что мы в разделе ОУ. Значит ничего другого не подойдет. Автору, ссылка на внутренности MXO37/14D и схема. Буфер - nc7szu04, частота 80MHz, выход - синус 10дБм typ (1В на 50Ом) при питании 4-5В. На 10МГц в 10 раз усилит. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Если взять конкретно nc7svu04 - это пара комплементарных CMOS транзисторов, сложно назвать "операционником". Без "u" - с дополнительным буферным каскадом. В ОУ транзисторов значительно больше, и больше количество последовательных каскадов. Главный вопрос зачем? Чтобы сохранить синусоидальную форму сигнала? Помню Вашу схему кварцевого генератора ) Приводил молодым дарованиям в качестве примера грамотного проектирования. Наилучшие результаты в буферном усилении показывают простые схемы на BJT с ОБ и низким входным сопротивлением (в каком-то смысле часть CFA). Но поскольку в теме нет высот типа -190дБн/Гц, то не хочется углубляться в тему. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Ключевой элемент имеет больше шансов не добавить собственных шумов. По схемотехнике буферов и изолирующих каскадов кварцевых генераторов наибольшее распространение получили ЛЭ и усилители класса-C. Для синуса есть ФНЧ. -

Операционник в качестве буфера

rloc ответил Prostograf тема в Операционные усилители и АЦП

Логика - это тоже усилитель, плюс ограничитель. Для примера - nc7sv04 (nc7svu04), инвертор, с резистором около 10к между входом и выходом. Шумы на уровне -175дБ/Гц. Усилителям свойственно насыщение при ограничении, убьете шумы. -

Ячейки Гильберта дают близкое к линейному перемножение. На LO можно подавать любой сигнал, с прямоугольным динамика выше, но появляются паразитные каналы приема/формирования на гармониках гетеродина. Конкретно по квадратурным смесителям-демодуляторам нужно смотреть, какого они типа. Есть с аналоговым вращением фазы, есть с цифровым. Первым требуется синус на LO, вторым - по большему счету безразлично, сигнал в любом случае внутри превращается в прямоугольный на логике.

-

Есть контроллеры, встроенные в ручной пульт. И автономность не повредит, чтобы не потерять, на каком месте остановился станок после пропадания питания. Можно копнуть немного глубже и окажется, что не все Ethernet контроллеры умеют так быстро работать, главным образом со стороны хоста. Видел много рекомендаций по читингу настроек драйверов, но подходит эта процедура далеко не всем. Есть черные списки по чипам, не рекомендованные к применению с LCNC. Но речь не об этом, были времена, когда SOC стоили в разы дороже, ситуация понятна.

-

Для обычного смесителя, например DBM, лучше меандр, динамика выше. Есть класс усилителей-ограничителей, предназначенных для преобразования синус->меандр перед LO. Для квадратурных смесителей (демодуляторов), построенных на аналоговом вращении фазы LO, обязательно подавать синус. В этом случае в спецификации можно увидеть требования к уровню гармоник.

-

Для SOC используются те же самые костыли. Плюс только в том, сам Linux легковесный, не обремененный обслуживаем лишней периферии. По части RT логика не сильно помогает, скорее позволяет решить вопросы с произвольной конфигурацией внешних устройств, нет никаких ограничений на кол-во счетчиков/таймеров, на скорость обработки и выдачу информации, нет задержек между ARM и логикой. Да, есть специалисты, которые портировали LCNC на малинку, и с тем тем же успехом отказались от x86 архитектуры.

-

На мой взгляд, наиболее красивое решение получается на SOC (в одном чипе ARM+FPGA). Вроде как очевидное решение, но пока не встречал контроллеров. Из готовых плат, покупал недавно платку на Ali с DDR3 256кБ и Ethernet 100М за 15$. Самостоятельно собирать, выйдет конечно дороже, около 50$. Есть Linux, на который портируется LCNC. Компактно, дешево и мало потребляет.

-

Я бы сказал, не одно софт-ядро интегрировали, со своей архитектурой и даже под TASM написали конфигурационный файл, чтобы на человеческом ассемблере писать. Но эти МК выполняют вспомогательные функции: конфигурация, обновление, а в остальном - чистый "hard metal" с фиксированным откликом.

-

По своему опыту, зависит от кол-ва обрабатываемых каналов. Скажем, захочет автор увеличить кол-во осей более 4-х, или оптические линейки поставить, или дискретность микрошагов увеличить до 204800 на оборот с частотой выдачи до 2МГц, тогда сложность разработки на микроконтроллере может многократно возрасти, если вообще будет выполнимой. В "серьезных" контроллерах применяют связку DSP+FPGA. Синтез одного или 100 счетчиков типа StepGen пройдут одинаково быстро, простые по архитектуре. Больших ПЛИС для подобных задач не требуется, поэтому и стоимость будет сравнима. Для примера, себестоимость контроллера типа Mesa 7i92 на Spartan6 около 20-30$.

-

Согласен. Мой вопрос изначально звучал так: что принципиально нового внесет микроконтроллер по сравнению с текущими решениями, вполне себе открытыми и доступными? Переформулирую "изобретение велосипеда". Не одни микроконтроллеры прогрессируют. Для описания аппаратуры набирает популярность Си++, впрочем и старый Verilog был сделан на базе C и не вызывает особых трудностей в освоении, особенно когда за плечами опыт работы с микроконтроллерами.

-

У автора в качестве примера были указаны контроллеры, применяемые в LinuxCNC и Mach3. Это системы, где расчетом траектории занимается хост-машина, а на контроллер возлагаются логические задачи. Для меня, вполне очевидным видится применение FPGA из самых простых и доступных серий.

-

Не из праздного любопытства, зачем изобретать велосипед? Вроде у MESA открыты исходники, повторяй, да расширяй систему. Оптимальность кода не вызывает никаких сомнений, видно, разрабатывали далеко не глупые люди. Сделать что-то свое, тем более на микроконтроллере, близкое по надежности и стабильности, очень сложно. По цене тоже не вижу выигрыша.