rloc

Модератор-

Постов

3 197 -

Зарегистрирован

-

Победитель дней

12

Весь контент rloc

-

Если переключать по цифровым входам, то вроде и парафазный выход не нужен. Допустимы отдельно ФД и делитель?

-

Или коммутировать цифровые входы REF/VCO, если мы говорим об отдельной микросхеме ФД.

-

Доплеровский измеритель скорости

rloc ответил SWAP тема в RF & Microwave Design

Дело не в постоянной времени, а в выборе оптимальной рабочей точки транзистора - чем ближе к точке срыва генерации, тем чувствительность выше. Чуть изменилась температура и автодин превращается в регенератор - это и была основная причина, почему в 40-50 гг отказались от автодинов. Обычно применяют два варианта решения - 1. АРУ (чего не вижу в схеме), 2. Самоподстройка автодина на оптимальный режим за счет колебаний около оптимальной точки (что и есть сверхрегенератор). По картинке - прерывистый режим генерации, чего можно добиться при наличии LRC в эмиттерной цепи и подбором смещения на базе. Как считать, подробно написано у Днищенко. -

Доплеровский измеритель скорости

rloc ответил SWAP тема в RF & Microwave Design

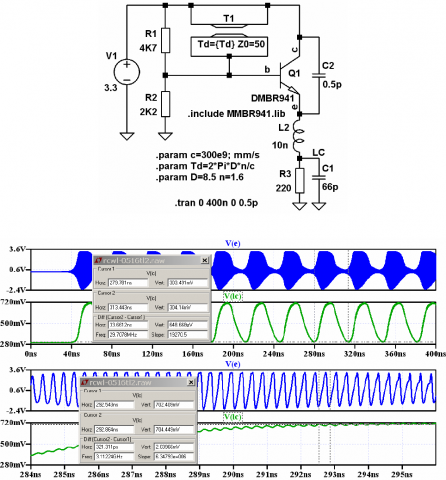

Мог бы поверить в это, но он не термостабилен. По информации в интернете, дальность обнаружения детектора может составлять до 5-10м - для такой чувствительности приемник должен работать близко к границе срыва генерации, и чтобы обеспечить такой режим работы (термостабильный) нужна обратная связь, постоянная подстройка. Да и работа в режиме, близком к срыву генерации - это достаточно линейный режим, сложно выделить разностную частоту. Сверхрегенератор - это не обязательно "пила" большой амплитуды, амплитуда напряжения суперизации может быть достаточно маленькой. Наткнулся на исследования работы похожего детектора, где автор показывает возможность работы в сверхрегенеративном режиме. https://www.researchgate.net/publication/322096918_Radar_Detector_RCWL-0516_generator_model -

Доплеровский измеритель скорости

rloc ответил SWAP тема в RF & Microwave Design

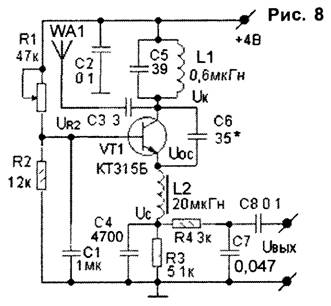

Мое предположение - это сверхрегенеративный приемник, где рабочая точка активного элемента колеблется между регенеративным и автодинным режимом, и именно эти низкочастотные колебания наблюдаются на выходе, а не доПлеровская частота (в русском языке принято писать с одной буквой "п" в отличии от Doppler). Приведу классическую схему сверхрегенератора на биполярном транзисторе: Днищенко В. "Принципы сверхрегенеративного приёма" (Радиомир, 2003, №1-5) http://www.radiolamp.ru/shem1/pages/72/ На частоте 3ГГц доплеровское смещение составит единицы-десятки Гц, выделить которое без кварцованного синтезатора с низким ФШ невозможно. -

Доплеровский измеритель скорости

rloc ответил SWAP тема в RF & Microwave Design

С чего вы взяли, что это доПлеровский датчик? -

R16 и выше - фантазии на этапе изучения современных алгоритмов FFT, увеличение основания не дает никакого выигрыша. GPU также была исключена из рассмотрения по двум причинам - большие накладные расходы на передачу данных в/из GPU и вероятно большую загрузку хоста, а не очень хочется, чтобы конечный пользователь испытывал нехватку производительности под свои задачи. Остановились на оптимальном алгоритме - R42 с учетом реализации в FPGA - конкретно тот вариант, который позволяет обрабатывать данные в потоке (streaming) из расчета по скорости 1:1 временной:частотный отсчет в единицу времени, с минимально возможной шириной полосы памяти на обработку (уменьшение потребления) и возможностью расширения по кол-ву точек обработки за счет дополнительного наращивания однотипных модулей, при исчерпании объема внутренней памяти. С ходу не могу сказать на каком конкретно алгоритме R42 остановились, человек пишет и надо понимать, разработка может растянутся на несколько лет.

-

Разрабатываем VCO

rloc ответил oleg-n тема в RF & Microwave Design

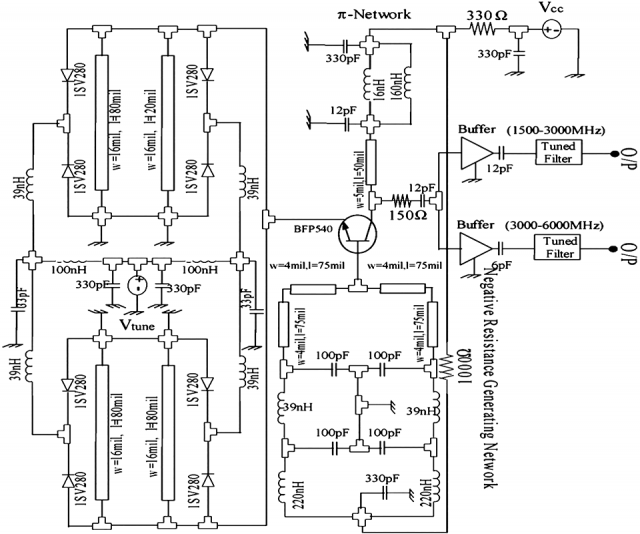

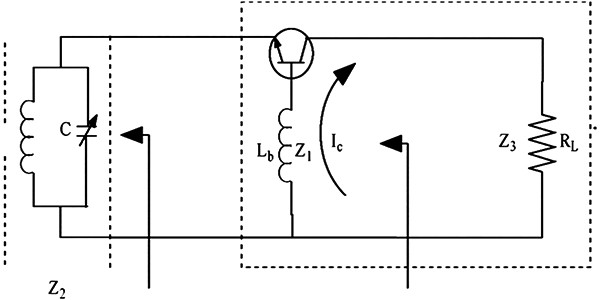

Очень близкая схема (диапазон 1-3ГГц или 3-6ГГц по второй гармонике), разница с DCYS300600 в ёмкостях варикапов, описана в следующей публикации (рис.7): 05755363.pdf Схема включения - с ОБ. ПОС образуется за счет индуктивности в базе. На диапазон частот 5-6 ГГц достаточно одинарных резонаторов, вместо сдвоенных. -

Разрабатываем VCO

rloc ответил oleg-n тема в RF & Microwave Design

На эти частоты скорее микросполоски. AWR, ADS, Genesys, Ansoft Designer помогут, но только для приблизительной оценки, согласования импедансов. За основу хорошо взять готовую схему, например DCYS300600-5 . Почему именно такую, можно обсудить, детально порисовать. -

Разрабатываем VCO

rloc ответил oleg-n тема в RF & Microwave Design

Обозначьте диапазон частот, ширину полосы перестройки, тип: LC, микрополосковый, ДР ... -

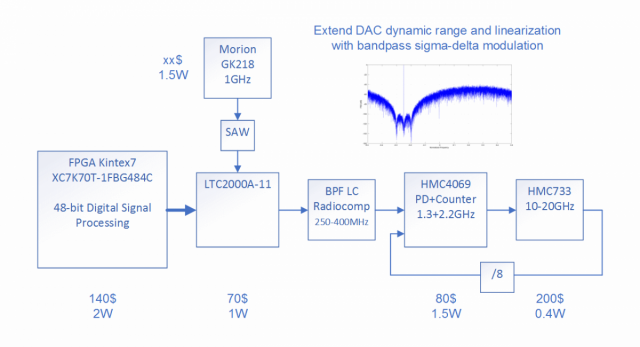

По практике, ранее в этой теме было формирование чистого сигнала на ЦАП, причем менее линейного: И далее пробные шаги в прямом умножении с фильтрацией на ЖИГ:

-

В эту цифру включены 2-я и 3-я гармоники. И выбрать диапазон, куда спуры низкой кратности не попадают, что вполне реально. LTC2000A хорош по линейности, чего не скажешь про шумы, но в данном случае вроде они не на первом месте.

-

От 20дБ до 50дБ выигрыш даст, нижняя граница - по спурам малой кратности, верхняя - по спурам высокой кратности. Во многих случаях этого вполне достаточно, чтобы не использовать сложные комбинационные схемы, и повысить быстродействие.

-

Причем здесь порядок и диапазон коэффициентов деления? В приведенном примере осуществляется амплитудная модуляция, не имеющая отношения ни к каким примерам. Причем модуляция однобитовая, а порядок 8-ой. Количество коэффициентов деления обычно берут столько, чтобы рекурсивный фильтр был устойчив.

-

В оригинале: https://ieeexplore.ieee.org/document/8088966 Альтернативно: http://circuits.ece.ntua.gr/documents/conferences/C80_Wide-Band Frequency Synthesis Using_Hardware-Efficient Band-Pass Single-Bit Multi-Step_Look-Ahead Sigma-Delta Modulators.pdf Примеров применения СДМ высокого порядка для частотной модуляции у меня нет, давно этим вопросом не интересовался.

-

Математика определяется не количеством переключаемых коэфф., а порядком и динамическим диапазоном. По определению, динамика 90дБ и более требует определенного кол-ва разрядов. Просто аккумулятор - это 0-ой порядок, что дает повод думать о простых вычислениях. 3-го или 4-го порядка иногда не хватает - многие видели, как в документации отдельной строкой прописываются дробные спуры - это нехватка ресурсов, недостаточная меширующая способность NTF (Noise Transfer Function). В современных FPGA реализуются ДСМ 8 порядка и выше.

-

Согласен, не самый удачный пример. Выводы основываются на знании архитектур современных скоростных ЦАП.

-

Уточню - на 2 умножить, с учетом разного масштаба. И после масштабирования 11 бит окажется более линейным. Pipeline DAC строятся по 2-х каскадной схеме, т.е. в преобразователе код-ток стоит не 2^N источников, а 2^N1 + 2^N2. 11-битный преобразователь может строится по однокаскадной схеме. Это все статическая линейность, динамическая выше и она опять меньше у 11-битного преобразователя, где гличи меньше, по причине меньшего кол-ва источников тока.

-

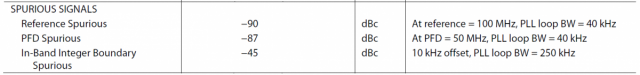

Многоразрядная математика и CPLD не совместимы. Для ДСМ и ФД, ДСМ был во внешней ПЛИС, полоса - около 1МГц, а с NB7N017M скорее шире не получится, переключение только между двумя коэффициентами деления. Мое представление о быстром однопетлевом ФАПЧ примерно такое, по опыту работы с ЦАП и ДСМ: Мало кто знает, или не встречали на практике, но с помощью ДСМ можно повышать динамику 8-ми и более разрядных преобразователей. На схеме указан ЦАП - LTC2000A 11-bit - по линейности он лучше, чем 14 или 16. Поясню на графике INL ниже: Для ФАПЧ вся полоса Найквиста не нужна, а сужение полосы при модуляции дает динамику не хуже, а скорее лучше, чем при 16 битах, но с сохранением более высокой линейности. В чем преимущество перед ДСМ в интегральных PLL? В PLL микросхемах ДСМ оперирует ~4-8 коэфф. деления, что соответствует ~2-3 разрядам, значит повышение ДД требует применения фильтров высокого порядка. В ЦАП ДД стартует с 11 бит. Плюс автоматически решается проблема с IBS. Без оглядки на ФШ, как-то так.

-

Да это же до боли знакомый прескалер NB7N017M на 3.5ГГц. Делал на нем ДСМ на 300МГц по ФД, до сих пор в некоторых изделиях идет. За счет того, что делитель пространственно отдален от ФД и ГУН уровень спур на 2 порядка ниже любого современного All-in-One, не говоря о быстродействии. На такой штуке уже более реалистичная картина с одной петлей ФАПЧ. Приятно удивлен, через десяток лет увидеть подобную схему. Заглянул в даташит, AD и не скрывает откровенно низкой ЭМС = высокий уровень IBS, опыт Linear пригодился бы к месту.

-

100% не получится. При коэффициенте умножения в петле 100-200 раз IBS встанут в полный рост. Как минимум стоит добавить пару-тройку переключаемых OCXO. Собирайте, посмотрим что из этого выйдет.

-

Проверьте напряжение питания усилителя и диапазон управления HMC733. По мутным картинкам PLL старается изо всех сил, но не может дотянуть до 19ГГц.

-

Шумы модулятора растут с космической скоростью после 2МГц. И для полосы 10МГц желательно найти PLL с более высокой частотой сравнения - 300 МГц и выше, заодно и шумы сдм сдвинутся выше.

-

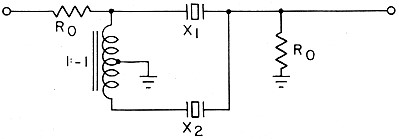

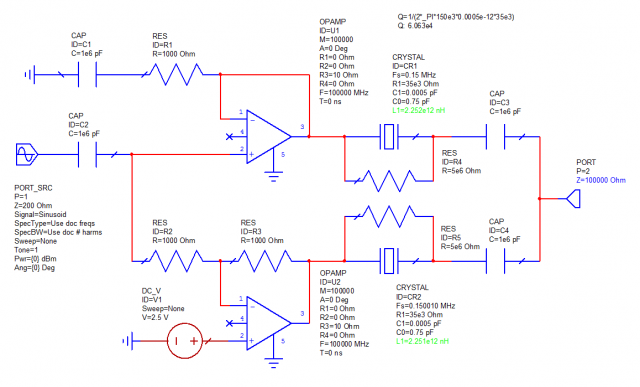

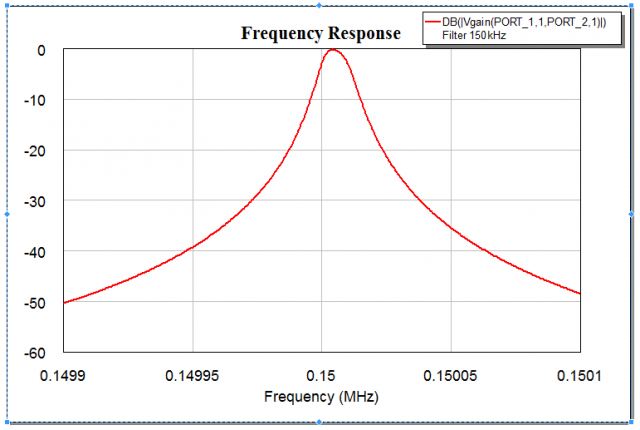

Не надо )) Не в упрек радиолюбителям, но многие собирают без понимания принципов работы и методики измерения. Встречаются и грамотные специалисты, но долго прогонять через себя поток информации и отсеивать 10%. Перерисовал схему в другом виде, чтобы резонаторы подключались к выходам, в предыдущем варианте были опасения по возбуждению. U1 работает в качестве повторителя с КУ=1, U2 - в качестве инвертора с КУ=-1. Вместе два усилителя образуют аналог полного дифференциального усилителя. Предполагается, что сопротивление нагрузки, порт 2, должно быть высоким, больше активного сопротивления резонаторов, а емкость - сравнима с емкостью электродов резонатора (~1-2пФ). В противном случае, желательно поставить промежуточный буфер. Конденсаторы С1-С4 разделяют по постоянной составляющей, ~1мкФ керамика. R1 нужен, чтобы выход U1 нагружался также, как выход U2. Резисторы R4 и R5 убирают постоянную составляющую на резонаторах, ~5МОм, так на резонаторы можно подать больше мощность. Источник V1 задает среднюю точку для работы усилителей при однополярном питании (резистивный делитель VCC/2 с большой фильтрующей емкостью). Такой вариант включения удобен тем, что емкости электродов взаимно компенсируют друг друга, с учетом того, что резонаторы из одной партии. Частоты должны немного, но отличаться. Допустим один резонатор отличается по частоте на +10Гц, тогда АЧХ будет выглядеть так: Хар-ка безусловно будет меняться по ширине и пульсациям в полосе в зависимости от разности частот. Но, к сожалению, поскольку коэфф. связи зависит от эквивалентных параметров (L и C), то он всегда фиксированный, соответственно с расширением полосы пульсации в полосе прозрачности (неравномерность) будут расти (двугорбая кривая). Можно в небольших пределах регулировать центральные частоты, если добавить последовательно к каждому резонатору подстроечный конденсатор. Функциональным аналогом является такая схема: Как уже правильно заметили, на частоте резонанса сопротивление становится чисто активным (по информации на конкретный китайский резонатор - это около 35кОм) и КУ = -R1/Rрез - это по предыдущей схеме. Самое худшее, что добавят резисторы, - это тепловые шумы. Если фаза и будет меняться, то только из-за температурного ухода самого резонатора.

- 44 ответа

-

- кварцевый резонатор

- узкополосный

-

(и ещё 1 )

C тегом:

-

Усилитель ограничитель

rloc ответил vanika тема в Предлагаю работу

Усилитель-ограничитель - логический инвертор с резистивным делителем на входе. Для ОУ режим ограничения не нормирован.