rloc

Модератор-

Постов

3 153 -

Зарегистрирован

-

Победитель дней

12

Весь контент rloc

-

Могу только предположить, что плата собрана на совместимом с FTDI контроллере и поэтому: https://wiki.sipeed.com/hardware/en/tang/Tang-Nano-Doc/install-the-ide.html#Programmer-application Этот кабель (FT232H) определяется в Gowin.

-

Микросхеме лет 7. Хороша для квадратурной модуляции, живьем наблюдал подавление зеркального канала и гетеродина лучше 60дБ. По потреблению ядра DDS думаю никто не подскажет. А зачем? Разрядность ЦАП 10бит

-

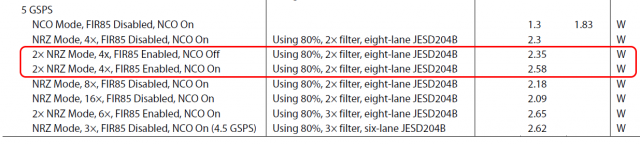

Аналоговая часть остается в активном состоянии во всех случаях, приведенных в таблице. Дело в том, что указанная микросхема представляет из себя ЦАП + встроенный DDS + набор интерполирующих фильтров. 0.23Вт - это потребление именно цифровой части DDS. Если интересно, то из этой таблицы видно, что потребление аналоговой части ЦАП составляет около 1Вт, цифровой части фильтра FIR85 (возможно вместе с интерфейсом JESD204) - 1.35Вт. Поэтому и пишу подробно о составе модуля DDS. Как можете видеть, потребление достаточно низкое и таблица LUT скромного размера, а основное потребление приходится на аппроксимацию по ряду Тейлора в виде 2-х умножителей, но опять же оно небольшое (0.23Вт), особенно на фоне интерполирующих фильтров.

-

Виталий, возьмите для сравнения более современный AD9162-64. Табл. 3 стр. 7 из даташита: Где потребление DDS (=NCO) составляет около 0.23Вт на фоне общего потребления ~2.5Вт. Учитывая генерацию DDS на частоте 5ГГц, количество одновременно работающих ядер должно быть около 8-16 шт, в зависимости от технологии CMOS. Из своего опыта реализации DDS на FPGA, ресурсы на одно ядро, при динамике ~120дБ по спурам, составляют: одна таблица LUT 512x32 и два умножителя 18x18 (по основным ресурсам). Думаю, можно отдельно взять ЦАП и RS-триггер, и потом просуммировать. Выход RS-триггера просуммировать с выходом ЦАП. Для простоты рассмотрения.

-

JLCPCB - карты UnionPay

rloc ответил IgorAVR2 тема в Изготовление ПП - PCB manufacturing

Насколько я понимаю, блокировка идет по БИНу карты (первые пять цифр), а он у всех карт банка одной платежной системы одинаковый. -

Согласование логических уровней 1.8В и 3.0В

rloc ответил Alt.F4 тема в Схемотехника

Не вижу общей базы, все выводы плавают. Но дело даже не в этом, насытить биполярный транзистор можно в любом включении и схема выше не исключение. С LTspice слабо знаком, не знаю насколько корректно он умеет симулировать задержку при насыщении, если она вообще фигурирует в модели транзистора. Вы бы написали, зачем нужны сложности с дискретными элементами? -

Согласование логических уровней 1.8В и 3.0В

rloc ответил Alt.F4 тема в Схемотехника

Процесс рассасывания неизбежен после насыщения, даже при закорачивании базы. -

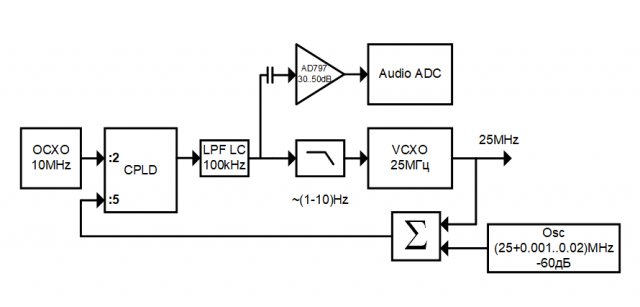

Примерно так: По материалам, аппноута AN1639 an1639.pdf ФД с делением, но и частота, по которой калибровка, тоже делится и в относительных единицах ФШ должен иметь одинаковое смещение. Прошу еще раз проверить.

-

Можно оценить ФШ по шуму на выходе ФД в рабочей схеме с CPLD. Подключить выход ФД на вход AD797, без разрыва петли, в прямом включении с ООС на 30/40/50 дБ и далее на вход любой звуковой карты. Калибровку по уровню можно сделать путем добавления к уровню несущей (25МГц) вспомогательной частоты с отстройкой на (1-20)кГц и с уровнем на 60дБ ниже уровня несущей.

-

-

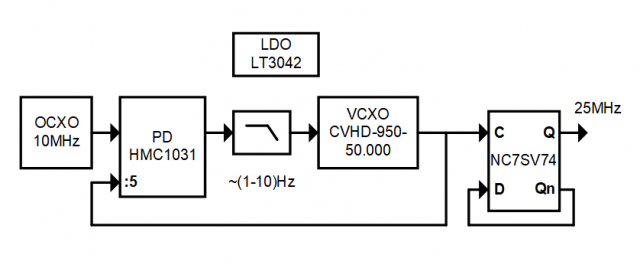

Ошибка кроется на системном уровне. Для умножения без потерь, шумы ГУН должны быть лучше шумов умноженной опоры 10МГц за пределами ПИ-фильтра. А ГУН на CPLD, пусть и с кварцевым резонатором, сделать малошумящим не получится, как по причине высоких собственных шумов, так и избыточного набега фазы из-за большой задержки.

-

Признаюсь не работал с этим ЦАП. Можете сказать в каком режиме работаете с JESD? Подкласс 0/1? Используете SYSREF с привязкой к тактовой частоте ЦАП?

-

Грустно смотреть на Charles Tumbaga, можно заменить на общую фотографию разработчиков?

-

Давно применяем в L-диапазоне Type-N на мощностях 4кВт, правда импульсных, средняя 80Вт. Разъемы холодные с любым диэлектриком.

-

Можете продублировать через скриншот или сохранение страницы? Нет доступа после регистрации.

-

Как я понял, автор пытается засинхронизировать приемник и передатчик одним клоком. Тогда зачем восстанавливать клок, если его можно передавать со стороны передатчика/приемника напрямую на высокой частоте, а не пытаться умножать на PLL из низкой частоты?

-

На вход АЦП нужно подать перестраиваемую частоту, проверить по 5-6 точкам, а в режиме измерения IMD - две частоты с небольшим разносом, дельта = (1-1000) кГц, уже сложнее собрать коллекцию кварцевых генераторов. Кратко резюмируя, генератор с низкими шумами в диапазоне до 2ГГц нужен как хлеб и вода. Александр, попробуйте найти на рынке лабораторный генератор с -170дБн/Гц@100МГц. Linkedin заблокирован у нас Роскомнадзором ) Уж не знаю чем он помешал, чтобы зарубежные компании не утаскивали ведущих российских специалистов )

-

Расчет простой, допустим есть АЦП с СПМШ около -160дБн/Гц при подаче синуса, близкого к полной шкале. А такие АЦП есть, -157дБн/Гц точно. Для того, чтобы опорные генераторы не повлияли на результат измерения, они должны на 20дБ быть ниже по шумам, относительно собственного шума АЦП. Да, есть способы вычитания шумов опорных генераторов, но сама методика более сложная и вызывает много спорных вопросов при анализе результата. Если есть возможность сразу "в лоб" измерить, такой путь предпочтителен.

-

Про него и речь, он шумит. Принимается, зачетный делитель, пусть и до 32 коэффициент деления. И на 2ГГц пишут -164дБн/Гц, фантастика. Подумываю, не слишком ли скромно -170дБн/Гц, может поднять до -175дБн/Гц? ) Вот уж действительно рекомендован для тестирования АЦП.

-

Такие есть на СВЧ и не мало, предполагаю проблема в оконечном триггере. Еще такой вопрос: кто применял LTC6953? Достаточно близко к -170дБн/Гц, потребление 2Вт, но что делать.

-

Высокое сопротивление (низкий ток потребления). Т.е. в первую очередь тепловые шумы, про дальние отстройки.

-

Со своей стороны кину клич (вопрос ко всем), что можно придумать для малошумящего деления частоты с 2ГГц и ниже? Коэффициенты деления 2, 4, 8 ..., чтобы расширить диапазон вниз до единиц кГц. Для тестирования современных АЦП не хватает -170дБн/Гц по ФШ/АШ на 100МГц чтобы достоверно оценить SNR. Известный нам регенеративный делитель пока отложим на полочку, полоса узкая. Параллельное включение нескольких делителей принимается, но с пометкой сложности синхронизации. Какие еще можно предложить варианты?

-

Xilinx IBIS Ultrascale+

rloc опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, у кого есть доступ или верифицированный корпоративный аккаунт, помогите с моделями IBIS и IBIS-AMS на всю серию Ultrascale+. Надеюсь там должны быть модели на новые Artix US+, включая S4P модели корпусов. В крайнем случае подойдут от Kintex US+ или Zynq US+, чтобы от чего-то отталкиваться. Хочу исследовать характеристики GTH и GTY трансиверов и влияние корпусов. https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-ami/ultrascale-plus-devices.html https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-models/ultrascale-plus-fpgas.html https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/ibis-models/zynq-ultrascale-plus-mpsoc.html В моем случае, при отправке запроса на доступ к моделям сначала приходит письмо с просьбой ожидания решения до 2 рабочих дней, а потом: Но при этом на загрузку последних Vivado/Vitis ограничений нет.