-

Постов

28 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Garik

-

Звание

Участник

Информация

-

Город

Array

-

Подкласс 1. По привязке к sysref не знаю, в регистрах этого пока не нашел.

-

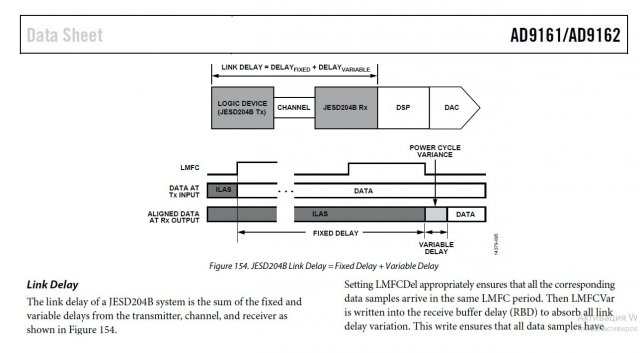

Здравствуйте. Коллеги помогите разобраться с проблемой. При каждой инициализации (при включении питания) ЦАП AD9162 разная задержка данных. Использую IP JESD204B от Xilinx. Алгоритм инициализации из даташита на чип. Расхождения могут быть в 50-70нс.

-

Победа SPI работает! Не работал стабилизатор AVDD3 3.3В на плате AD9680. Запитал от другого стаба - все ОК

-

К сожалению не реагирует. Проверял лично. Реагирует только хардварно пин 14(PDN/STBY), а софтварно по SPI нет.

-

Как сделано в проекте от АД. Первое что это читается Chip_id. Остальная инициализация после этого. dev = (struct ad9680_dev *)malloc(sizeof(*dev)); if (!dev) return -1; /* SPI */ ret = spi_init(&dev->spi_desc, &init_param->spi_init); ad9680_spi_read(dev, AD9680_REG_CHIP_ID_LOW, &chip_id); if(chip_id != AD9680_CHIP_ID) { printf("AD9680: Invalid CHIP ID (0x%x).\n", chip_id); return -1; } К сожалению ответа от АЦП нет. Сейчас я склоняюсь, что это неисправность чипа. Сегодня еще раз посмотрели микроскопом на пайку чипа, проверили питание, слок - все в норме, и ни каких зацепок.

-

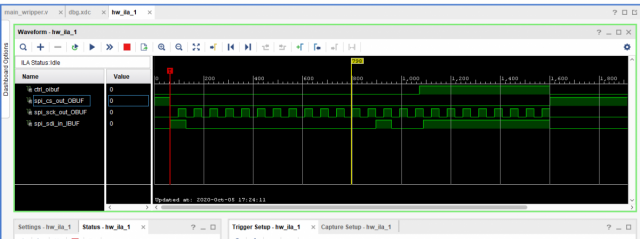

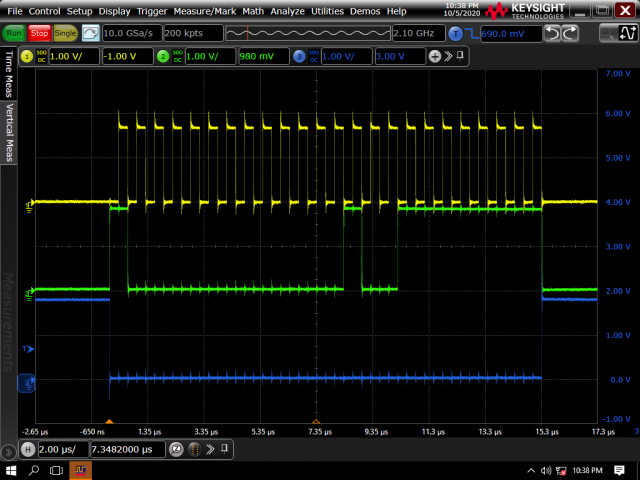

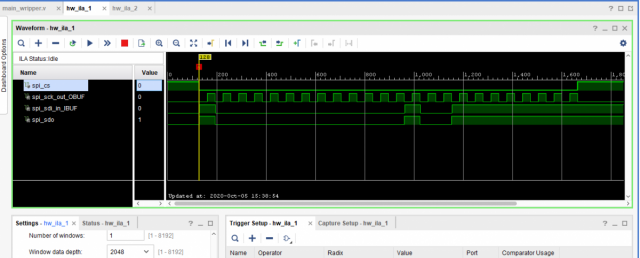

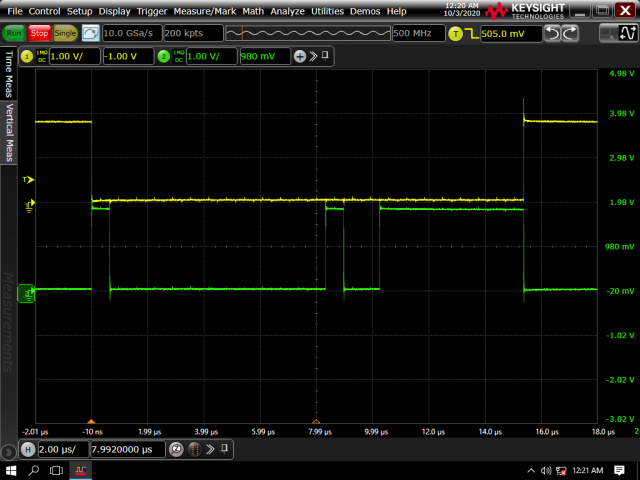

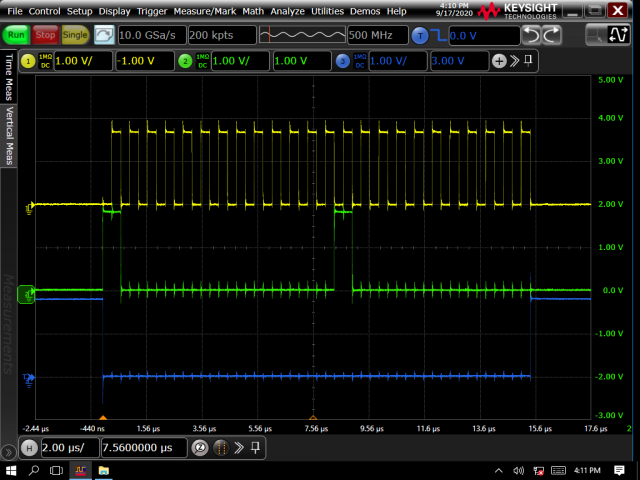

Это отладочная плата от AD. Мы ее сами не собирали. Тайминги все выдержаны! Осциллограмма непосредственно на пинах чипа АД. 37 CSB - синий 36 SCLK - желтый 35 SDIO - зеленый Ниже с логического анализатора Vivado. Передача от АЦП в последних 8 бит отсутствует. Скорость 1.6 Мб/с. чтение 4 регистра (Chip id) Все 0 или 1 быть не могут.

-

Выше!

-

Да без проблем. Как видно на осциллограмме AD9680 SDIO - не передает данные данные. Это 4 регистр (Chip ID) всех 0 или 1 быть не должно.

-

Не помню. Я экспериментировал в месте, где должны идти данные от AD. 0 и Z точно делал. Все что я отправляю 24 бита эхом приходит на приемник ПЛИС. А судя по осциллограмме пин АЦП да же и не пытается передавать.

-

Да в 0! Я выставлял и 0 и Z на вход буфера. Результат одинаковый - ответа нет. Все соответствует схеме. Если перемычка отсутствует то 0! Для работы пин должен быть в 0!

-

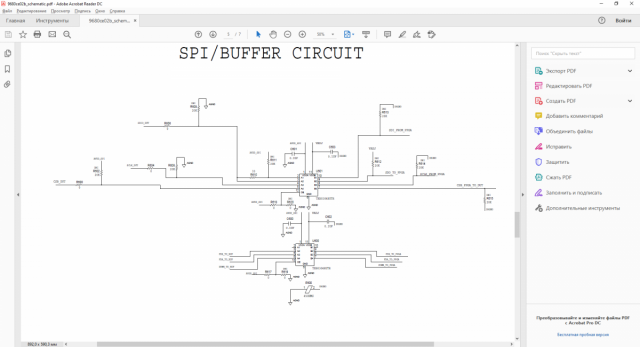

9680ce02b_schematic.pdf

-

На схеме нарисовано! Проблема, что чип не отвечает. Со стороны ПЛИС 4-х проводный SPI. 3-х пробовал это проблему не решает

-

Конечно припаяны это плата от AD. Самого ADIO на FPGA нет. Там 4-х проводный SPI. SDIO на чипе AD. Также на плате AD9680 есть буферы с преобразованием уровня, а также сделано разделение на SDI и SDO. Я передаю и принимаю данные по отдельным линиям. Единственное FPGA SDO (master), на время чтения от АЦП перевожу в Z. У самого АЦП только 3-х проводный - по пинам так.

-

Проблема с SPI АЦП AD9680

Garik опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую всех. Столкнулся с проблемой с SPI в AD9680. Не могу прочитать регистры чипа. Использую AD9680-LF500EBZ с Xilinx Artix-7 FPGA AC701. Подробнее о проблеме порт SDIO AD9680 не переходит на передачу данных при транзакции чтения регистров. Осциллограмма на выводах чипа - 35 – SDIO цвет зеленый; - 36 – SCLK цвет желтый; - 37 – CSB цвет синий. Транзакция 24 бита. Чтение 4-го регистра - Chip_ID. Старшие 16 бит команда, младшие 8 бит это ожидаемы данные от АЦП, которые всегда равны нулю. Передача данных осуществляется старшим битом вперед. Скорость передачи данных 1,6Mb/s. Прошу помощи?