-

Постов

3 861 -

Зарегистрирован

Весь контент Maverick_

-

мне надо чтобы были данные, а оставшиеся пространство памяти я заполняю нулями в приведенном примере у меня 28 нулей именно про них и речь сейчас мне постоянно надо считать оставшиеся свободное пространство и заполнять нулями я бы хотел автоматизацию типа (others=>"00000000000000000000000000000000"); и ниже N количество данных

-

инициализация блочной памяти, vhdl

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Например есть описание блочной памяти с инциализацией следующего вида library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity bram_test is generic ( DATA : integer := 32; ADDR : integer := 8 ); port ( -- Port A a_clk : in std_logic; a_wr : in std_logic; a_addr : in std_logic_vector(ADDR-1 downto 0); a_din : in std_logic_vector(DATA-1 downto 0); a_dout : out std_logic_vector(DATA-1 downto 0); -- Port B b_clk : in std_logic; b_wr : in std_logic; b_addr : in std_logic_vector(ADDR-1 downto 0); b_din : in std_logic_vector(DATA-1 downto 0); b_dout : out std_logic_vector(DATA-1 downto 0) ); end bram_test; architecture rtl of bram_test is -- Shared memory type mem_type is array ( (2**ADDR)-1 downto 0 ) of std_logic_vector(DATA-1 downto 0); -- FUNCTION initialize_ram return mem_type is variable result : mem_type; -- BEGIN -- FOR i IN ((2**ADDR)-1) DOWNTO 0 LOOP -- result(i) := std_logic_vector( to_unsigned(natural(i), natural'(DATA))); -- END LOOP; -- RETURN result; -- END initialize_ram; shared variable mem : mem_type := ( "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", "00000000000000000000000000000000", std_logic_vector(to_unsigned(1073741824, 32 )), --end commands, it is 30 bit = '1' --helper commands std_logic_vector(to_unsigned(16384, 32 )), -- '1'-on; '0'-off std_logic_vector(to_unsigned(64, 32 )), --commands --pause std_logic_vector(to_unsigned(100, 32 )), --pause_value std_logic_vector(to_unsigned(5, 32 )), --time_resolution std_logic_vector(to_unsigned(8, 32 )), --commands ------------------------------------------------------------------------------------- --line std_logic_vector(to_unsigned(135, 32 )), --aYEnd_line std_logic_vector(to_unsigned(28, 32 )), --aXEnd_line std_logic_vector(to_unsigned(135, 32 )), --aYStart_line std_logic_vector(to_unsigned(70, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(124, 32 )), --aYEnd_line std_logic_vector(to_unsigned(71, 32 )), --aXEnd_line std_logic_vector(to_unsigned(135, 32 )), --aYStart_line std_logic_vector(to_unsigned(28, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(123, 32 )), --aYEnd_line std_logic_vector(to_unsigned(33, 32 )), --aXEnd_line std_logic_vector(to_unsigned(124, 32 )), --aYStart_line std_logic_vector(to_unsigned(71, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(113, 32 )), --aYEnd_line std_logic_vector(to_unsigned(76, 32 )), --aXEnd_line std_logic_vector(to_unsigned(123, 32 )), --aYStart_line std_logic_vector(to_unsigned(33, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(114, 32 )), --aYEnd_line std_logic_vector(to_unsigned(41, 32 )), --aXEnd_line std_logic_vector(to_unsigned(113, 32 )), --aYStart_line std_logic_vector(to_unsigned(76, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(105, 32 )), --aYEnd_line std_logic_vector(to_unsigned(78, 32 )), --aXEnd_line std_logic_vector(to_unsigned(114, 32 )), --aYStart_line std_logic_vector(to_unsigned(41, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(106, 32 )), --aYEnd_line std_logic_vector(to_unsigned(52, 32 )), --aXEnd_line std_logic_vector(to_unsigned(105, 32 )), --aYStart_line std_logic_vector(to_unsigned(78, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(74, 32 )), --aYEnd_line std_logic_vector(to_unsigned(87, 32 )), --aXEnd_line std_logic_vector(to_unsigned(106, 32 )), --aYStart_line std_logic_vector(to_unsigned(52, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(112, 32 )), --aYEnd_line std_logic_vector(to_unsigned(149, 32 )), --aXEnd_line std_logic_vector(to_unsigned(74, 32 )), --aYStart_line std_logic_vector(to_unsigned(87, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(111, 32 )), --aYEnd_line std_logic_vector(to_unsigned(122, 32 )), --aXEnd_line std_logic_vector(to_unsigned(112, 32 )), --aYStart_line std_logic_vector(to_unsigned(149, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(125, 32 )), --aYEnd_line std_logic_vector(to_unsigned(160, 32 )), --aXEnd_line std_logic_vector(to_unsigned(111, 32 )), --aYStart_line std_logic_vector(to_unsigned(122, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(125, 32 )), --aYEnd_line std_logic_vector(to_unsigned(122, 32 )), --aXEnd_line std_logic_vector(to_unsigned(125, 32 )), --aYStart_line std_logic_vector(to_unsigned(160, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(139, 32 )), --aYEnd_line std_logic_vector(to_unsigned(169, 32 )), --aXEnd_line std_logic_vector(to_unsigned(125, 32 )), --aYStart_line std_logic_vector(to_unsigned(122, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(140, 32 )), --aYEnd_line std_logic_vector(to_unsigned(122, 32 )), --aXEnd_line std_logic_vector(to_unsigned(139, 32 )), --aYStart_line std_logic_vector(to_unsigned(169, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(152, 32 )), --aYEnd_line std_logic_vector(to_unsigned(184, 32 )), --aXEnd_line std_logic_vector(to_unsigned(140, 32 )), --aYStart_line std_logic_vector(to_unsigned(122, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(153, 32 )), --aYEnd_line std_logic_vector(to_unsigned(28, 32 )), --aXEnd_line std_logic_vector(to_unsigned(152, 32 )), --aYStart_line std_logic_vector(to_unsigned(184, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands --line std_logic_vector(to_unsigned(135, 32 )), --aYEnd_line std_logic_vector(to_unsigned(70, 32 )), --aXEnd_line std_logic_vector(to_unsigned(153, 32 )), --aYStart_line std_logic_vector(to_unsigned(28, 32 )), --aXStart_line std_logic_vector(to_unsigned(2, 32 )), --commands ------------------------------------------------------------------------------------- --change_plane XY or XZ or YZ std_logic_vector(to_unsigned(0, 32 )), -- std_logic_vector(to_unsigned(32, 32 )), --commands --shim_fsm_Z_axis std_logic_vector(to_unsigned(20, 32 )), -- num_step std_logic_vector(to_unsigned(511, 32 )), -- axis_select std_logic_vector(to_unsigned(128, 32 )), --commands --period divider for pwm std_logic_vector(to_unsigned(150, 32 )), --z std_logic_vector(to_unsigned(150, 32 )), --Y std_logic_vector(to_unsigned(150, 32 )), --X std_logic_vector(to_unsigned(16, 32 )) --commands ); -- := initialize_ram; --mem_type begin -- Port A process(a_clk) begin if(a_clk'event and a_clk='1') then if(a_wr='1') then mem(conv_integer(a_addr)) := a_din; end if; a_dout <= mem(conv_integer(a_addr)); end if; end process; -- Port B process(b_clk) begin if(b_clk'event and b_clk='1') then if(b_wr='1') then mem(conv_integer(b_addr)) := b_din; end if; b_dout <= mem(conv_integer(b_addr)); end if; end process; end rtl; можно ли как то задавать инициализацию остальной памяти нулями без их предварительного количественного подсчета ? -

Отдельным процессом описать мультиплексор и отдельно описать декодер, который будет управлять комутацией

-

RobFPGA какую частоту сделать таким образом? не упростит ли синтезатор ткую петлю?

-

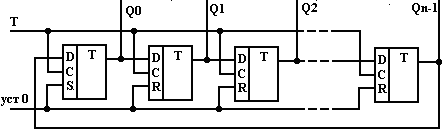

Распределителем тактов является сдвигающий регистр, выход последнего разряда которого подсоединен к входу первого разряда. В данном регистре все триггеры, кроме первого, устанавливаются в нулевое состояние, а в первый записывается логическая единица. По каждому такту логическая единица, переписывается в следующий регистр, а из последнего регистра в первый. ниже приведено описание на vhdl library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Generator is port ( clk, rst : std_logic; Dout : out std_logic_vector(7 downto 0) ); end Generator; architecture behav of Generator is signal S: std_logic_vector(7 downto 0); begin Process (clk,rst) begin if rst = '0' then S<="00000001"; elsif clk='1' and clk'event then for i in 0 to 6 loop S(i)<=S(i+1); S(7)<=S(0); end loop; end if; end process; Dout<=S; End behav;

-

Если кто скачал можете поделиться?

-

проблема с Circuit Studio

Maverick_ опубликовал тема в Altium Designer, DXP, Protel

Всем привет :) Есть одна активная лицензия на Circuit Studio. Там написано, что он зарегистрирован для @Daniel Schröer. Но я не могу найти сам файл лицензии. Мне это нужно для переноса лицензии с одного ПК на другой. Можно ли его установить на удаленном ПК? Или можно как-нибудь восстановить файл лицензии? -

TC напишете пожалуйста более подробно что Вы хотите сделать?

-

Так Вы можете реализовать в одной памяти: например старшая половина памяти для приема данных, младшая для отправки. Идеально конечно два буфера размером на 1 пакет данных Чтобы синтезатор увидел Болочную память нужно ее корректно описать - в template имются примеры

-

Возьмите напишите тестбенч и в симуляции все увидите как Ваш модуль работает... В симуляции будут видны все сигналы, а RTL viewer поможет понять как Вас понимает синтезатор... В симуляции сделайте мастер SPI (судя по тому что Вы сейчас делайте, обратитевнимание на циклограмму микросхемы с которой Вы планируете работать)... Не пытайтесь пропустить данный этап... Только после того как в симуляции будет все хорошо то можно приступать к работе с платой... У Вас клок заведен на плату я думаю намного больше чем клок приходящий от SPI - нужна синхронизация Рекомендую Вашу схему разбить на модули, например модуль синхронизации, модуль приема данных (сдвигающий регистр), модуль отправки данных (сдвигающий регистр), модуль управления (управляющий автомат - управляет всеми модулями) и т.д. Тогда будете видеть их в RTL viewer и поможет понять как Вас понимает синтезатор

-

псевдокод: if signal_write_1 = 1 then register <= 1 elsif signal_write_0 = 1 then register <= 0 end if оберните в олвейс с клоком и будет Вам " В моём понимании идеальным решением было бы "расшарить" регистр между модулями. В одном модуле в него пишут 1, при этом второй модуль можно считать эту единицу, а потом записать туда нолик и первый модуль увидит его. "

-

в чем секрет? :)

-

проблемы с PWM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Хороший принцип. Я к этому принципу только стремлюсь... -

проблемы с PWM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Посмотрел твои описания - мега крутые в плане понимания и документируемости... -

проблемы с PWM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

это да. У меня (в описании которое я выложил в первом посте) сигнал ready (один такт) формируется каждого периода (ready_period_shim) и когда автомат закончил работу то формируется также ready (ready) В сигнал done можно переименовать сигнал ready - я так наверное и сделаю ... -

проблемы с PWM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

большое спасибо Если приходит сигнал прерывание, то автомат закнчивает формирование текущего периода, но новый период не начинает формировать (на выходе PWM логический 0). Либо уходит в ожидание пока действует прерывание работы либо уходит в состояние старта (тут я еще не решил) -

проблемы с PWM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Zynq / CycloneV SoC -

проблемы с PWM

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем доброго дня :) Под конец рабочего дня ... голова не "варит" Реализация должна быть по сигналу прерывания на следующем шаге прерываться. Делать строго заданное количество шагов(периодов) (num_step в тестбенче). Можно ли ускорить работу (тактовую частоту) или/и упростить логику? Как по мне описание немного сложноватое... shim_fsm.rar -

Сортировка чисел первоисточник

-

+1 Согласен

-

Сортировка в VHDL

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

" как мне сделать скалабилити. я хочу задать d0 - dN. generate cell_0 - cell_N " если Вы это сделаете, выложите пожалуйста здесь PS Сейчас по работе сильно загружен... -

Сортировка в VHDL

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

LIBRARY ieee; USE ieee.std_logic_1164.all; USE IEEE.numeric_std.ALL; USE ieee.std_logic_signed.ALL; ENTITY sort_list_vhd_tst IS END sort_list_vhd_tst; ARCHITECTURE sort_list_arch OF sort_list_vhd_tst IS -- constants -- signals SIGNAL clk : STD_LOGIC; SIGNAL din : STD_LOGIC_VECTOR(3 DOWNTO 0):= (others => '1'); SIGNAL do0 : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL do1 : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL do2 : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL do3 : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL en : STD_LOGIC; SIGNAL insert_out : std_logic; SIGNAL rst : STD_LOGIC; COMPONENT sort_list PORT ( clk : IN STD_LOGIC; din : IN STD_LOGIC_VECTOR(3 DOWNTO 0); do0 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); do1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); do2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); do3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); insert_out : OUT std_logic; en : IN STD_LOGIC; rst : IN STD_LOGIC ); END COMPONENT; BEGIN i1 : sort_list PORT MAP ( -- list connections between master ports and signals clk => clk, din => din, do0 => do0, do1 => do1, do2 => do2, do3 => do3, en => en, insert_out => insert_out, rst => rst ); clock_gen: process begin clk <= '0'; wait for 25 ns; clk <= '1'; wait for 25 ns; end process; reset_gen: process begin rst <= '1'; wait for 10 ns; rst <= '0'; wait; end process; en_gen: process begin en <= '0'; wait for 10 ns; en <= '1'; wait; end process; const_gen: process (clk) begin if (clk'event and clk='1') then din <= din + "0001"; end if; end process; END sort_list_arch; -

Сортировка в VHDL

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

"do0, do1, do2, do3 это отсортированные значения ?" Да Я ниже привел тестбенч попробуйте запустить симуляцию и все станет ясно как работет. Или посмотрите тестбенч - как я подаю сигналы на вход -

Сортировка в VHDL

Maverick_ ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

------------------------------------------------------------------------------ -- Описание приведено для поиска четырех минимальных чисел. -- Легко масштабируется путем увеличения количества модулей sort_list_cell. -- Значение на входе сохраняется в модуле sort_list_cell, -- начиная с которого это значение превосходит значение -- регистра dout (условие позиции вставки: cprev = 0 и cout = 1). -- Остальные модули, у которых din < dout, берут новое значение -- регистра dout с выхода предыдущего модуля. -- dprev - содержимое регистра предыдущего модуля -- cprev - значение на входе din больше чем dprev -- cout - значение на входе din больше чем dout -- do0 - максимальное значение -- do3 - минимальное значение ------------------------------------------------------------------------------ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity sort_list is port(clk, en, rst : in std_logic; din : in std_logic_vector(3 downto 0); insert_out : out std_logic; do0, do1, do2, do3 : out std_logic_vector(3 downto 0)); end sort_list; architecture archi of sort_list is component sort_list_cell is port(clk, en, rst : in std_logic; din : in std_logic_vector(3 downto 0); dprev : in std_logic_vector(3 downto 0); cprev : in std_logic; cout : out std_logic; dout : out std_logic_vector(3 downto 0)); end component sort_list_cell; signal reg_cout0, reg_cout1, reg_cout2, reg_cout3: std_logic; signal reg_do0, reg_do1, reg_do2, reg_do3 : std_logic_vector(3 downto 0); signal reg_insert : std_logic; begin cell_3 : sort_list_cell port map ( clk => clk, en => en, rst => rst, din => din, dprev => reg_do2, cprev => reg_cout2, dout => reg_do3, cout => reg_cout3); cell_2 : sort_list_cell port map ( clk => clk, en => en, rst => rst, din => din, dprev => reg_do1, cprev => reg_cout1, dout => reg_do2, cout => reg_cout2); cell_1 : sort_list_cell port map ( clk => clk, en => en, rst => rst, din => din, dprev => reg_do0, cprev => reg_cout0, dout => reg_do1, cout => reg_cout1); cell_0 : sort_list_cell port map ( clk => clk, en => en, rst => rst, din => din, dprev => (others => '0'), cprev => '0', dout => reg_do0, cout => reg_cout0); do0 <= reg_do0; do1 <= reg_do1; do2 <= reg_do2; do3 <= reg_do3; reg_insert <= ('0' and reg_cout0) or (reg_cout0 and reg_cout1) or (reg_cout1 and reg_cout2) or (reg_cout2 and reg_cout3); insert_out <= reg_insert; end archi; library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity sort_list_cell is port(clk, en, rst : in std_logic; din : in std_logic_vector(3 downto 0); dprev : in std_logic_vector(3 downto 0); cprev : in std_logic; cout : out std_logic; dout : out std_logic_vector(3 downto 0)); end sort_list_cell; architecture archi of sort_list_cell is signal reg_dout: std_logic_vector(3 downto 0); signal reg_cout: std_logic; begin reg_cout <= '1' WHEN din < reg_dout ELSE '0'; cout <= reg_cout; process (clk, en, rst) begin if rst = '1' then reg_dout <= (others => '1'); elsif (clk'event and clk='1') then if(en and reg_cout) = '1' then if cprev = '1' then reg_dout <= dprev; else reg_dout <= din; end if; end if; end if; end process; dout <= reg_dout; end archi; я думаю данные для сортировки у вас появляються последовательно, тогда данный вариант должен подойти -

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity Pipeline_Counter is generic ( width_g: natural := 64; -- Must be divisible by parts_g. parts_g: natural := 4 ); port ( clk: in std_logic; rst_n: in std_logic; clear: in std_logic; enable: in std_logic; count: out std_logic_vector(width_g - 1 downto 0); tick: out std_logic ); end Pipeline_Counter; architecture rtl of Pipeline_Counter is constant part_width_c: natural := width_g / parts_g; signal almost_tick_r: std_logic_vector(parts_g - 1 downto 0); signal count_r: std_logic_vector(width_g - 1 downto 0); begin count <= count_r; process (clk, rst_n) variable part_v: unsigned(part_width_c - 1 downto 0); variable tick_v: std_logic; begin if rst_n = '0' then count_r <= (others => '0'); almost_tick_r <= (others => '0'); tick <= '0'; elsif rising_edge(clk) then tick_v := enable; for i in 0 to parts_g - 1 loop part_v := unsigned(count_r((i + 1) * part_width_c - 1 downto i * part_width_c)); if tick_v = '1' then -- Value is max - 1? if part_v = to_unsigned(2**part_width_c - 2, part_width_c) then almost_tick_r(i) <= '1'; else almost_tick_r(i) <= '0'; end if; part_v := part_v + 1; end if; count_r((i + 1) * part_width_c - 1 downto i * part_width_c) <= std_logic_vector(part_v); tick_v := tick_v and almost_tick_r(i); end loop; tick <= tick_v; if clear = '1' then count_r <= (others => '0'); almost_tick_r <= (others => '0'); tick <= '0'; end if; end if; end process; end architecture; testbench library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity tb_pipeline_counter is end entity; architecture testbench of tb_pipeline_counter is signal clk, rst_n: std_logic; signal clear: std_logic; signal enable: std_logic; signal count: std_logic_vector(15 downto 0); signal tick: std_logic; begin cnt1: entity work.Pipeline_Counter generic map (width_g => 16, parts_g => 4) port map (clk, rst_n, clear, enable, count, tick); process procedure clock is constant PERIOD: time := 1 us; begin clk <= '0'; wait for PERIOD/2; clk <= '1'; wait for PERIOD/2; end procedure; begin rst_n <= '0'; clear <= '0'; enable <= '0'; clock; rst_n <= '1'; enable <= '1'; for i in 0 to 65535 loop assert unsigned(count) = to_unsigned(i, 16) report "Wrong count, " & integer'image(to_integer(unsigned(count))) & " expected " & integer'image(i); assert tick = '0' report "Unexpected tick"; clock; end loop; assert count = X"0000" report "Expected to roll over"; assert tick = '1' report "Expected tick"; clock; assert count = X"0001"; clear <= '1'; clock; clear <= '0'; assert count = X"0000" report "Counter should clear"; clock; assert count = X"0001"; report "Simulation ended" severity note; wait; end process; end architecture;