-

Постов

3 865 -

Зарегистрирован

Весь контент Maverick_

-

Platform designer (quartus)

Maverick_ опубликовал тема в Среды разработки - обсуждаем САПРы

-

http://aperiodic.net/phil/archives/Geekery/find-duplicate-elements.html

-

Input: [1, 4, 3, 3, 2, 5] Sum = 18 As in this example, we have n = 5: Sum of 1 to 5 = 1 + 2 + 3 + 4 + 5 = 15=> 18 - 15 = 3 so 3 is the duplicate но Input: [1, 2, 3, 2, 3, 4] Sum = 15As in this example we have n = 5, Sum of 1 to 5 = 1 + 2 + 3 + 4 + 5 = 15/!\ Not working

-

Спасибо, отпишитесь пожалуйста по результатам реализации

-

Вот моя наброска самой простой реализации (не проверял, но логически вроде верно) - на вход поставить паралельно-последовательный конвертор, чтобы на вход моего модуля данные (Ваши 25 чисел) приходили последовательно) library ieee; use ieee.std_logic_1164.all; library work; package Const_type is type my_array is array (0 to 255) of std_logic_vector (7 downto 0); end package; library IEEE; use IEEE.STD_LOGIC_1164.ALL; USE ieee.numeric_std.ALL; use work.Const_type.all; entity hist is Port ( CLK : in std_logic; rst : in std_logic; indata : in std_logic_vector (7 downto 0); ready : out std_logic; outdata : out std_logic_vector (7 downto 0); ); end hist; architecture behavioral of hist is signal table_index : my_array; signal reg_data : std_logic_vector (7 downto 0); signal reg_index : std_logic_vector (7 downto 0); signal reg_state : std_logic_vector (1 downto 0);; begin process (all) begin if (rst = '1') then reg_index <= (OTHERS => (OTHERS => '0')); reg_state <= (others => '0'); reg_ready <= '0'; reg_index <= (others => '0'); reg_data <= (others => '0'); elsif (CLK'event and CLK ='1') then if reg_state = "00" then -- read data from table reg_data <= indata; reg_index <= table_index(to_integer(unsigned(indata))); reg_state <= std_logic_vector( unsigned(reg_state) + 1); reg_ready <= '0'; elsif reg_state = "01" then -- calculation index reg_state <= std_logic_vector( unsigned(reg_state) + 1); reg_index <= std_logic_vector( unsigned(reg_index) + 1); elsif reg_state = "10" then -- write new date to table reg_state <= (OTHERS => '0'); table_index (to_integer(unsigned(reg_data))) <= reg_index; reg_ready <= '1'; end if; end if; end process; outdata <= table_index (to_integer(unsigned(reg_data))); ready <= reg_ready; end behavioral; Реализация простая есть так сказать 3 состояния/такта (reg_state). На каждом состоянии/такте происходит соотвующая операция: 1. чтение данных из таблицы; 2 инкремент индекса 3 запись нового значения индекса в таблицу Далее все начинается сначала... PS Далее делаем второй модуль который сделать по сигналу ready сравнивает значение индексов (выход outdata) с предыдущим значение. Внутренний регистр в котором будет храниться максимальное число инициализируете максимальным числом (как то так reg_max <= (others => '1');) не проверял - наброски... library ieee; use ieee.std_logic_1164.all; library work; package Const_type is type my_array is array (0 to 24) of std_logic_vector (7 downto 0); end package; library IEEE; use IEEE.STD_LOGIC_1164.ALL; USE ieee.numeric_std.ALL; use work.Const_type.all; entity parallel2serial is generic( num : integer:= 25 ); port ( i_clk : in std_logic; i_rstb : in std_logic; i_data_ena : in std_logic; i_data : in my_array; o_data_valid : out std_logic; o_data : out std_logic_vector (7 downto 0)); end parallel2serial; architecture rtl of parallel2serial is signal r_data : my_array; signal r_count : integer range 0 to (num-1); begin p_paralle2serial : process(all) begin if(i_rstb='0') then r_count <= 0; elsif(rising_edge(i_clk)) then if i_data_ena = '1' then r_count <= r_count + 1; o_data <= i_data(r_count); end if; if r_count = 24 then o_data_valid <= '1'; else o_data_valid <= '0'; end if; end if; end process p_paralle2serial; Будут вопросы спрашивайте :) паралельная pipeline реализация займет больше ресурсов чем представленная последовательная реализация

-

2 ЕвгенийЗлыднев Для старта можно попробовать так: Создаем (исходя что 2^8=256) массивы регистров: - таблицы данных 256х8бит регистров (с начальной инициализацией равной 0) -таблицы индексов 256х8бит регистров (с начальной инициализацией равной 0). По приходу нового значения (само значение это адрес для таблицы 256х8бит регистров). Читаем по данному адресу если там уже имеется такое же число (работает 8 бит компаратор на равенство) и параллельно читаем индекс для данного регистра (адрес одинаковый для двух таблиц), то производим прибавление 1 для данного индекса иначе прибавляем 0 и записываем результат полученного индекс обратно в таблицу индексов. И так далле. В конце если требуется найти максимальное число повторений можно модифицировать такой поиск по таблице индексов (там же можете посмотреть как создавать массивы регистров): PS Массивы регистров можно заменить при необходимости память на BRAM или ALM(SRL). Скорее всего нужна только одна таблица индексов (оптимизация за Вами). Например просто добавить в таблицу индексов один бит по которому можно будет судить было ли раннее такое входное число.

-

Ответ супер. Повеселил. спасибо.

-

посмотрите это

-

в таком случае PLL использовать для автора не вариант?

-

вложение... возможно поможет... coder_decoder_1553_v.zip

-

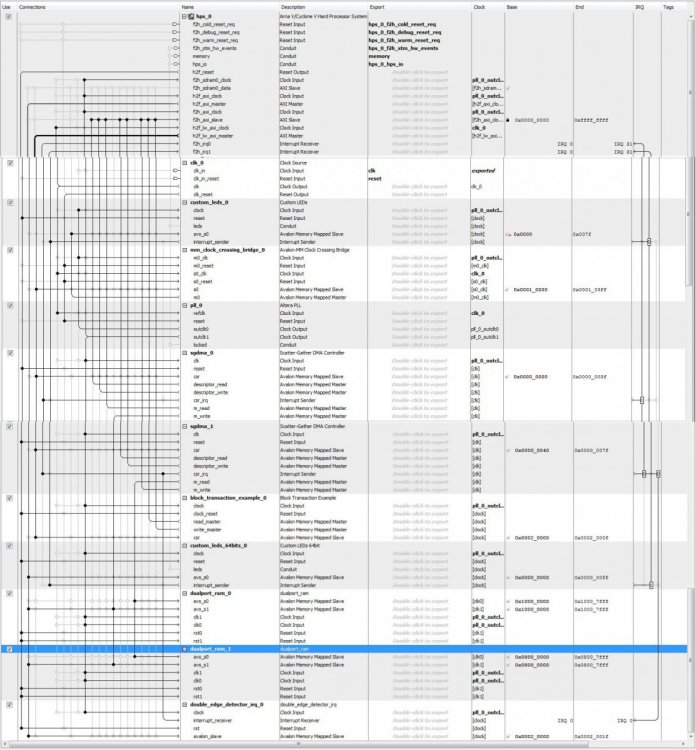

///////////////////////////////////////////////////////////////////////////////////////////////// //Scatter Gather DMA controller 2 printf( "\n\n------------- Scatter DMA 2---------------\n\n" ); //create descriptors in the mapped memory struct alt_avalon_sgdma_packed *sgdma_desc01=sdram_16MB_add; struct alt_avalon_sgdma_packed *sgdma_desc02=sdram_16MB_add+sizeof(struct alt_avalon_sgdma_packed); struct alt_avalon_sgdma_packed *sgdma_desc03=sdram_16MB_add+2*sizeof(struct alt_avalon_sgdma_packed); struct alt_avalon_sgdma_packed *sgdma_desc_empty0=sdram_16MB_add+3*sizeof(struct alt_avalon_sgdma_packed); //Address to the physical space void* sgdma_desc1_phys0=(void*)SDRAM_16_BASE; void* sgdma_desc2_phys0=(void*)SDRAM_16_BASE+sizeof(struct alt_avalon_sgdma_packed); void* sgdma_desc3_phys0=(void*)SDRAM_16_BASE+2*sizeof(struct alt_avalon_sgdma_packed); void* sgdma_desc_empty_phys0=(void*)SDRAM_16_BASE+3*sizeof(struct alt_avalon_sgdma_packed); //configure the descriptor initDescriptor(sgdma_desc01,(void*)DUALPORT_RAM_0_BASE,(void*)(SDRAM_64_BASE+40), sgdma_desc2_phys0,8*20, //sgdma_desc2_phys ( _SGDMA_DESC_CTRMAP_OWNED_BY_HW)); initDescriptor(sgdma_desc02,(void*)DUALPORT_RAM_1_BASE,(void*)(SDRAM_64_BASE+120), sgdma_desc_empty_phys0,8*20, ( _SGDMA_DESC_CTRMAP_OWNED_BY_HW)); /*initDescriptor(sgdma_desc01,(void*)ONCHIP_MEMORY_BASE,(void*)(SDRAM_64_BASE), sgdma_desc_empty_phys,4*20, ( _SGDMA_DESC_CTRMAP_OWNED_BY_HW));*/ /*initDescriptor(sgdma_desc3,(void*)SDRAM_64_BASE,(void*)MEMORYDMA_M_WRITE_MYBUS_BASE, sgdma_desc_empty_phys,4*30, (_SGDMA_DESC_CTRMAP_WRITE_FIXED_ADDRESS | _SGDMA_DESC_CTRMAP_OWNED_BY_HW));*/ initDescriptor(sgdma_desc_empty0,NULL,NULL, sgdma_desc_empty_phys0,0, (_SGDMA_DESC_CTRMAP_WRITE_FIXED_ADDRESS)); //map memory of the control register h2p_lw_sgdma_addr=virtual_base + ( ( unsigned long )( ALT_LWFPGASLVS_OFST + 0x40 ) & ( unsigned long)( HW_REGS_MASK ) ); printf( "sgma2 addr %08x\n", ((uint32_t *)h2p_lw_sgdma_addr)); printf( "sgma2 status %08x\n", *((uint32_t *)h2p_lw_sgdma_addr)); ////fill the data space //for (long int i=0;i<256; i++){ // *((uint32_t *)sdram_64MB_add+i)=i; //} //init the SGDMA controller init_sgdma(_SGDMA_CTR_IE_CHAIN_COMPLETED); debugPrintRegister(); //set the address of the descriptor setDescriptor(sgdma_desc1_phys0); //start the transfer setControlReg(_SGDMA_CTR_IE_CHAIN_COMPLETED|_SGDMA_CTR_RUN); debugPrintRegister(); //wait until transfer is complete waitFinish(); //for (long int i=0;i<256; i++){ //printf( "%d\n", *((uint32_t *)sdram_64MB_add+i)); // } printf( "/*///////////////////*/////////////////*/ \n"); for (long int i=0;i<256; i++){ //printf( "%d\n", *((uint64_t *)sdram_64MB_add+i)); printf("%" PRIx64 "\n", *((uint64_t *)sdram_64MB_add+i)); } //printf( "////////////////////////////////////// \n"); //for (int i=0;i<40;i++){ //printf( "%d\n", *((uint64_t *)h2p_rom_addr+i)); //printf("%" PRIx64 "\n", *((uint64_t *)h2p_rom_addr+i)); //} debugPrintDescriptorStatus(sgdma_desc01); //stop the core by clearing the run register setControlReg(_SGDMA_CTR_IE_CHAIN_COMPLETED); debugPrintDescriptorStatus(sgdma_desc01); ////////work interupt receive (double_edge_detector_irq) /////////////////////////////////////////////////////////// //h2p_intr_capturer_addr *(uint64_t *)h2p_intr_capturer_addr = 2; for (int k = 0; k < 8; k++) { printf( "intr_capturer k = %d\n", *((uint32_t *)h2p_intr_capturer_addr+k)); } пытаюсь захватить вырабатываемое прерывание модулем на логике, чтобы знать что прерывание действительно было. создал в платформ дизайнере проект (скришот вложение) написал программу (см выше) - извините не привык к новому движку сделал так сказать обработчик прерываний на логике library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity double_edge_detector_irq is GENERIC( Num_bit : INTEGER := 64); port ( clk : in std_logic; rst : in std_logic; irq_in : in std_logic; -- bus Avalon MM avs_address : in std_logic_vector (1 downto 0); avs_readdata : out std_logic_vector ((Num_bit-1) downto 0); avs_write : in std_logic; avs_read : in std_logic; avs_writedata : in std_logic_vector ((Num_bit-1) downto 0) ); end double_edge_detector_irq; architecture rtl of double_edge_detector_irq is signal din_delayed1 :std_logic; signal reg_change :std_logic; signal reg_data : std_logic_vector ((Num_bit-1) downto 0); signal count : std_logic_vector (((Num_bit/2)-1) downto 0); begin process(clk, rst) begin if rst = '1' then din_delayed1 <= '0'; elsif rising_edge(clk) then din_delayed1 <= irq_in; end if; end process; reg_change <= (din_delayed1 xor irq_in); --rising or falling edge (0 -> 1 xor 1 -> 0) process(clk, rst) begin if rst = '1' then count <= (others => '0'); elsif rising_edge(clk) then if avs_write = '1' then count <= avs_writedata(((Num_bit/2)-1) downto 0); else if reg_change = '1' then count <= std_logic_vector(unsigned(count) + 1); end if; end if; end if; end process; process(clk, rst) begin if rst = '1' then avs_readdata <= (others => '0'); elsif rising_edge(clk) then if avs_read = '1' then if avs_address = "00" then avs_readdata <= reg_data((Num_bit-2) downto 0)®_change; elsif avs_address = "01" then avs_readdata(31 downto 0) <= count; end if; end if; end if; end process; end rtl; пытаюсь считать на модуле обработчика прерывания - по нулям (программа после ////////work interupt receive (double_edge_detector_irq) /////////////////////////////////////////////////////////// )... Может кто-то сталкивался с такой проблемой - прошу помощи

-

не проще было написать clk_i <= not(clk);

-

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

вопрос снят ... Всем спасибо за помощь :) -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Вы правы не подключен был, подключил double_edge_detector_irq.vhd -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

задействован - самая последняя строка в tcl скрипте -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Добрый день. подскажите пожалуйста где в tcl скрипте ошибка, что платформ дизайнер (Qsys) не хочет видеть IP core (в IP каталоге платформ дизайнер (Qsys) отсутствует) double_edge_detector_irq.tcl double_edge_detector_irq.vhd -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

wolfman спасибо -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

у Вас есть исходники описания генерируемого IP ядро? -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

можете привести пример описания слейва с waitrequest и readdatavalid или в мое описание приведенное выше их добавьте.... -

вопрос по avalon MM

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Спасибо за помощь... -

вопрос по avalon MM

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

добрый день есть вопрос по спецификация (стр 16) имеется сигнал waitrequest и readdatavalid. Для слейва они нужны? Можно ли попросить посмотреть мое описание слейва: прилагаю также tcl скрипт # TCL File Generated by Component Editor 17.1 # Fri Jul 26 17:03:31 EEST 2019 # DO NOT MODIFY # # dualport_ram "dualport_ram" v1.0 # RocketBoards.org 2019.07.26.17:03:31 # Dualport memory Avalon slave MM IP # # # request TCL package from ACDS 16.1 # package require -exact qsys 16.1 # # module dualport_ram # set_module_property DESCRIPTION "Dualport memory Avalon slave MM IP" set_module_property NAME dualport_ram set_module_property VERSION 1.0 set_module_property INTERNAL false set_module_property OPAQUE_ADDRESS_MAP true set_module_property AUTHOR RocketBoards.org set_module_property DISPLAY_NAME dualport_ram set_module_property INSTANTIATE_IN_SYSTEM_MODULE true set_module_property EDITABLE true set_module_property REPORT_TO_TALKBACK false set_module_property ALLOW_GREYBOX_GENERATION false set_module_property REPORT_HIERARCHY false # # file sets # add_fileset QUARTUS_SYNTH QUARTUS_SYNTH "" "" set_fileset_property QUARTUS_SYNTH TOP_LEVEL dualport_ram set_fileset_property QUARTUS_SYNTH ENABLE_RELATIVE_INCLUDE_PATHS false set_fileset_property QUARTUS_SYNTH ENABLE_FILE_OVERWRITE_MODE false add_fileset_file dualport_ram.vhd VHDL PATH ip/dualport_ram/dualport_ram.vhd TOP_LEVEL_FILE # # parameters # # # module assignments # set_module_assignment embeddedsw.dts.compatible dev,dualport-ram set_module_assignment embeddedsw.dts.group rams set_module_assignment embeddedsw.dts.vendor dsa # # display items # # # connection point avs_s0 # add_interface avs_s0 avalon end set_interface_property avs_s0 addressUnits WORDS set_interface_property avs_s0 associatedClock clk0 set_interface_property avs_s0 associatedReset rst0 set_interface_property avs_s0 bitsPerSymbol 8 set_interface_property avs_s0 burstOnBurstBoundariesOnly false set_interface_property avs_s0 burstcountUnits WORDS set_interface_property avs_s0 explicitAddressSpan 0 set_interface_property avs_s0 holdTime 0 set_interface_property avs_s0 linewrapBursts false set_interface_property avs_s0 maximumPendingReadTransactions 0 set_interface_property avs_s0 maximumPendingWriteTransactions 0 set_interface_property avs_s0 readLatency 0 set_interface_property avs_s0 readWaitTime 1 set_interface_property avs_s0 setupTime 0 set_interface_property avs_s0 timingUnits Cycles set_interface_property avs_s0 writeWaitTime 0 set_interface_property avs_s0 ENABLED true set_interface_property avs_s0 EXPORT_OF "" set_interface_property avs_s0 PORT_NAME_MAP "" set_interface_property avs_s0 CMSIS_SVD_VARIABLES "" set_interface_property avs_s0 SVD_ADDRESS_GROUP "" add_interface_port avs_s0 avs_s0_address address Input 12 add_interface_port avs_s0 avs_s0_read read Input 1 add_interface_port avs_s0 avs_s0_write write Input 1 add_interface_port avs_s0 avs_s0_readdata readdata Output 64 add_interface_port avs_s0 avs_s0_writedata writedata Input 64 set_interface_assignment avs_s0 embeddedsw.configuration.isFlash 0 set_interface_assignment avs_s0 embeddedsw.configuration.isMemoryDevice 0 set_interface_assignment avs_s0 embeddedsw.configuration.isNonVolatileStorage 0 set_interface_assignment avs_s0 embeddedsw.configuration.isPrintableDevice 0 # # connection point avs_s1 # add_interface avs_s1 avalon end set_interface_property avs_s1 addressUnits WORDS set_interface_property avs_s1 associatedClock clk1 set_interface_property avs_s1 associatedReset rst1 set_interface_property avs_s1 bitsPerSymbol 8 set_interface_property avs_s1 burstOnBurstBoundariesOnly false set_interface_property avs_s1 burstcountUnits WORDS set_interface_property avs_s1 explicitAddressSpan 0 set_interface_property avs_s1 holdTime 0 set_interface_property avs_s1 linewrapBursts false set_interface_property avs_s1 maximumPendingReadTransactions 0 set_interface_property avs_s1 maximumPendingWriteTransactions 0 set_interface_property avs_s1 readLatency 0 set_interface_property avs_s1 readWaitTime 1 set_interface_property avs_s1 setupTime 0 set_interface_property avs_s1 timingUnits Cycles set_interface_property avs_s1 writeWaitTime 0 set_interface_property avs_s1 ENABLED true set_interface_property avs_s1 EXPORT_OF "" set_interface_property avs_s1 PORT_NAME_MAP "" set_interface_property avs_s1 CMSIS_SVD_VARIABLES "" set_interface_property avs_s1 SVD_ADDRESS_GROUP "" add_interface_port avs_s1 avs_s1_address address Input 12 add_interface_port avs_s1 avs_s1_read read Input 1 add_interface_port avs_s1 avs_s1_write write Input 1 add_interface_port avs_s1 avs_s1_readdata readdata Output 64 add_interface_port avs_s1 avs_s1_writedata writedata Input 64 set_interface_assignment avs_s1 embeddedsw.configuration.isFlash 0 set_interface_assignment avs_s1 embeddedsw.configuration.isMemoryDevice 0 set_interface_assignment avs_s1 embeddedsw.configuration.isNonVolatileStorage 0 set_interface_assignment avs_s1 embeddedsw.configuration.isPrintableDevice 0 # # connection point clk1 # add_interface clk1 clock end set_interface_property clk1 clockRate 0 set_interface_property clk1 ENABLED true set_interface_property clk1 EXPORT_OF "" set_interface_property clk1 PORT_NAME_MAP "" set_interface_property clk1 CMSIS_SVD_VARIABLES "" set_interface_property clk1 SVD_ADDRESS_GROUP "" add_interface_port clk1 b_clk clk Input 1 # # connection point clk0 # add_interface clk0 clock end set_interface_property clk0 clockRate 0 set_interface_property clk0 ENABLED true set_interface_property clk0 EXPORT_OF "" set_interface_property clk0 PORT_NAME_MAP "" set_interface_property clk0 CMSIS_SVD_VARIABLES "" set_interface_property clk0 SVD_ADDRESS_GROUP "" add_interface_port clk0 a_clk clk Input 1 # # connection point rst0 # add_interface rst0 reset end set_interface_property rst0 associatedClock clk1 set_interface_property rst0 synchronousEdges DEASSERT set_interface_property rst0 ENABLED true set_interface_property rst0 EXPORT_OF "" set_interface_property rst0 PORT_NAME_MAP "" set_interface_property rst0 CMSIS_SVD_VARIABLES "" set_interface_property rst0 SVD_ADDRESS_GROUP "" # # connection point rst1 # add_interface rst1 reset end set_interface_property rst1 associatedClock clk1 set_interface_property rst1 synchronousEdges DEASSERT set_interface_property rst1 ENABLED true set_interface_property rst1 EXPORT_OF "" set_interface_property rst1 PORT_NAME_MAP "" set_interface_property rst1 CMSIS_SVD_VARIABLES "" set_interface_property rst1 SVD_ADDRESS_GROUP "" полностью корректное подключение к шине Avalon MM описание блочной памяти или есть нюансы? Может какие то сигналы шины Avalon MM я упустил? PS просто сомнения есть... -

я про работу с hdl описанием в текстовом редакторе... NotePad++ поддерживает синтаксис VHDL/Verilog как предварительный вариант получения файла top level графический редактор подойдет, потом можно сгенерить hdl описание и продолжать уже работать в текстовом редакторе

-

Пльзуйтесь например NotePad++ там выделяешь сигнал и он подсвечивается. По подсветке можно проверять подключение. Как по мне удобно.

-

2 new123 https://forums.intel.com/s/question/0D50P00003yyThQSAU/unexpected-irq-trap-at-vector-xxx-arria-10-soc-linux?language=ru не помогает ссылка на аналогичную проблему у людей...

-

L1 path development

Maverick_ ответил MIkler тема в Алгоритмы ЦОС (DSP)

des00 Вам скорее всего не ответит MIkler он сам наверное не в теме