-

Постов

3 861 -

Зарегистрирован

Весь контент Maverick_

-

помощь с тестбенчем

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

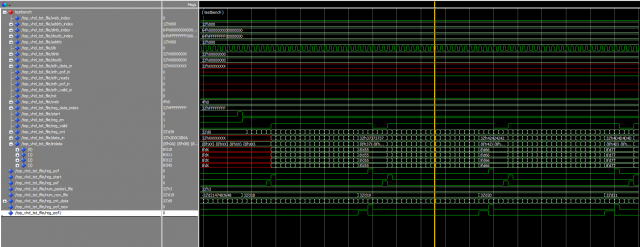

Добрый день мне стыдно обращаться с таким простым вопросом... но я что то не могу понять. Пишу тестбенч (во вложении). Там есть процесс process (all) begin if (rst = '1') then reg_eof <= '0'; reg_eof1 <= '0'; elsif (clk'event and clk = '1') then if reg_cnt_data = std_logic_vector(to_unsigned((num_row_file), reg_cnt_data'length)) then reg_eof <= '1'; else reg_eof <= '0'; end if; if reg_cnt_data = std_logic_vector(to_unsigned((num_row_file-1), reg_cnt_data'length)) then reg_eof1 <= '1'; else reg_eof1 <= '0'; end if; end if; end process; Почему reg_eof1 занимает 2 такта, а reg_eof - 1 такт. ??? Не могу понять. Прошу помощи indata.txt top_vhd_tst_file.vhd -

Просто любопытство Вы сами разработали MJPEG ?

-

image DSP

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день всем Натолкнулся на относительно простой алгоритм сжатия картинок. https://phoboslab.org/log/2021/12/qoi-specification В реализации на fpga тоже относительно прост... -

Можно на базе двухпортовой памяти организовать двойной буффер

-

Добрый день

Если видите что человек продает откровенный шлак, который долго не проработает, то пишите покупателю свои мысли в личку.

Иначе продавец очень сильно злиться как сейчас...

-

Юзеры что не должны знать про этот прикол ?

Это офигенный осцилл и я выбивал его себе на работе год. А потом он сдох новый и я ничего не смог с ним сделать, после платного ремонта в Присте он проработал 2 дня(((

В личке же меня этот лихой парень назвал мудаком. Я ему ни одного слова плохого не сказал.

И потом, это не просто Лекрой. Это еще и битый Лекрой. Как нужно всадить прибор, чтобы из него вырвать кусок ? Именно поэтому возможно на 20Gs прибор он ставит такой ценник.

Возможно эта штука уже глючит....

-

-

fpga_student и Maxim_S Прекратили ссориться!!!

- 16 ответов

-

- Lecroy

- WaveRunner

-

(и ещё 1 )

C тегом:

-

возможно это натолкнет на мысль - Ping Pong FIFO http://cospandesign.github.io/fpga,fifo/2016/05/02/ppfifo.html (работоспособность описания не проверял) PS Идея использовать плюсы двойного буфера (давблбуффер) . Для хранения данных со всех источников использовать даблбуфер. Хранить начальные адреса пакетов (вместе с длиной пакета) в отдельной памяти - можно это сделать для каждого источника отдельно. Чтобы оперативно можно производить пактное чтение с даблбуффера для каждого источника. Отдельно через регистр передавать количество пакетов записанных в даблбуффер. Сбрасывать указатели адресов памяти как только даблбуффер переключился, например. Это просто как мысли ...

-

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

как самый простой способ фильтрации это обычная пауза. внешняя борьба с дребезгом например триггер шмидта... -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Спасибо, Мур такой термин как вертикальный счетчик слышу впервые :) -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Имеют, плюс еще надо учитывать пологие фронты... -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Я не уточнил - вопрос к деталировке. Уровень рисования цифровой схемы это счётчик, дешифратор, мультиплексор и так далее... -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Вот пример описание ШИМа (Широтно-импульсная модуляция (ШИМ, или Pulse-Width Modulation, PWM) Первый процесс описывает счетчик который считает 1 период ШИМ сигнала, второй процесс компаратор, третий процесс позволяет менять период сигнала шима и длительность нуля library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity shim is generic ( N : natural := 3 ); Port ( clk : in STD_LOGIC; rst : in STD_LOGIC; en : in STD_LOGIC; --load : in STD_LOGIC; Period : in STD_LOGIC_VECTOR (N-1 downto 0); Duty_cycle : in STD_LOGIC_VECTOR (N-1 downto 0); ready_period : out STD_LOGIC; out_shim : out STD_LOGIC ); end shim; architecture Behavioral of shim is signal count_shim : STD_LOGIC_VECTOR (N-1 downto 0); signal reg_Period : STD_LOGIC_VECTOR (N-1 downto 0); signal reg_Duty_cycle : STD_LOGIC_VECTOR (N-1 downto 0); begin process (all) begin if rst = '1' then count_shim <= (others=>'0'); elsif(rising_edge(clk)) then if en = '1' then if count_shim = reg_Period then ready_period <= '1'; count_shim <= (others=>'0'); else count_shim <= count_shim + std_logic_vector( to_unsigned(1, count_shim'length )); ready_period <= '0'; end if; end if; end if; end process; process (all) begin if rst = '1' then out_shim <= '0'; elsif(rising_edge(clk)) then if count_shim < reg_Duty_cycle then out_shim <= '1' ; else out_shim <= '0'; end if; end if; end process; process (all) begin if rst = '1' then reg_Period <= (others=>'0'); reg_Duty_cycle <= (others=>'0'); elsif(rising_edge(clk)) then if ready_period = '1' then reg_Period <= Period; reg_Duty_cycle <= Duty_cycle; end if; end if; end process; end Behavioral; ниже пример схемы детектирования концевика (коментариев не даю) - как пример --detect_sensor library ieee; use ieee.std_logic_1164.all; --use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity detect_sensor is generic ( N : natural := 32 ); Port ( clk : in STD_LOGIC; rst : in STD_LOGIC; sensor : in STD_LOGIC; en_detect : in STD_LOGIC; sensor_rising : out STD_LOGIC; sensor_falling : out STD_LOGIC ); end detect_sensor; architecture Behavioral of detect_sensor is signal opto_sensor_shift_r : unsigned (N-1 downto 0); signal reg_sensor_falling, reg_sensor_rising : STD_LOGIC; begin sensor_rising <= reg_sensor_rising; sensor_falling <= reg_sensor_falling; process(all) begin if(rst = '1') then opto_sensor_shift_r <= (others=>'0'); elsif(rising_edge(clk)) then opto_sensor_shift_r <= opto_sensor_shift_r(N-2 downto 0) & sensor; end if; end process; process(all) begin if(rst = '1') then reg_sensor_rising <= '0'; reg_sensor_falling <= '0'; elsif(rising_edge(clk)) then if en_detect = '1' then if opto_sensor_shift_r((N-1) downto (N/2)) = to_unsigned(((2**(N/2))-1), N/2) and opto_sensor_shift_r((N/2-1) downto 0) = to_unsigned(0, N/2) then reg_sensor_rising <= '1'; else reg_sensor_rising <= '0'; end if; if opto_sensor_shift_r((N-1) downto (N/2)) = to_unsigned(0, N/2) and opto_sensor_shift_r((N/2-1) downto 0) = to_unsigned(((2**(N/2))-1), N/2) then reg_sensor_falling <= '1'; else reg_sensor_falling <= '0'; end if; end if; end if; end process; end Behavioral; Из-за этого я и пишу что нужно описывать цифровую схему ... -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

я не категорично отношусь ))) просто по другому нельзя делать разработку на FPGA ))) -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

правильно, дальше на базе примитивной логики тригеров(регистров) и комбинационной логики (and or xor и другие логические операторы) надо описать на VHDL этот делитель частоты. Еще как помощь может быть для Вас это Template там Вы можете найти примеры описаний счетчиков, блоков памяти, FSM и другие... Далее написать тестбенч и проверить работу... -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Ок, начнем с простого, как Вы плаируете например с 50МГц сделать 100Гц? Может лучше работать на на тактовой частоте, есть же сигналы enable? -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Vhdl также как и verilog это как карандаш в руках хужника. Если художник не умеет рисовать, то карандаш не поможет. Предлагаю начать рисовать цифровую схему на листочке. Потом опишете ее на vhdl и промолелируете, т.е. проверите ее правильность работы. Когда симуляция покажет что схема работает тогда начнёте проверки на плате. Иначе никак... PS GRAFCET у FESTO и в TIA PORTAL это высокоуровневые языки от производителей. Сравнивать их с Vhdl/verilog не коректно мягко говоря. Наверное модули которые программируются с помощью этих языков сложные цифровые устройстава. -

Логика на VHDL

Maverick_ ответил Станислав Н тема в Языки проектирования на ПЛИС (FPGA)

Вы не правильно сформулировали вопрос, главный вопрос какую цифровую схему вы видите для реализации описания в FPGA вашей потребности Что насчет цифоровой схемы? С моделированием цифровых схем "дружите"? В современных платах FPGA тактовая частота подается от 50МГц и выше. Дальше Ваше описание цифровой схемы которое делит тактовую частоту до 100Гц (если Вы видите в этом необходимость), формирует импульсы для шаговых двигателей и обрабатывает концевики... -

На fpgadeveloper нет реализации (во всяком случае я ее не нашел). Там идет ссылка на сайт https://www.intelliprop.com/ipc-nv164-hi/ И я уверен что стоит эта корка не дешево...

-

Всем спасибо за советы...

-

мне пока нравиться решение Спасибо

-

можно поподробнее пожалуйста особенно второй пункт с намеком на схемотехнику...

-

Дополню задачу - внесу более четкость Выход каждого модуля это порт памяти с которого необходимо прочитать результат обработки после ready = '1' Давайте пока считать что только 1 ready = '1' может быть Предыдущий пост дополнил для ясности задачи

-

des00 спасибо за подсказку... Добрый день. (update) есть несколько индентичных модулей (размножены с помощью generic). Модуль выдает ready как данные готовы. Все модули ready выдать одновремнно не могут - только один срабатывет Выход каждого модуля это порт памяти с которого необходимо прочитать результат обработки после ready = '1'. Вопрос как мне определить с какого модуля мне надо забрать данные и как построить мультиплексор к портам памяти (возможно есть другие красивые решения). Мое решение сложное - как по мне: ниже ход мыслей Объеденяем все ready от модулей в один регистр, далее module bitscan (req,sel); parameter WIDTH = 16; input [WIDTH-1:0] req; output [WIDTH-1:0] sel; assign sel = req & ~(req-1); endmodule (что делает этот модуль во вложении картинка) от результата отнимаем 1 и считаем количество едениц ответом и будет номер модуля с какого модуля мне надо забрать данные в котором сработал ready Потом мультиплексор ... library ieee ; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity mux4 is port( d0 : in std_logic_vector(1 downto 0); d1 : in std_logic_vector(1 downto 0); d2 : in std_logic_vector(1 downto 0); d3 : in std_logic_vector(1 downto 0); s : in std_logic_vector(1 downto 0); m : out std_logic_vector(1 downto 0)); end mux4; architecture rtl of mux4 is type t_array_mux is array (0 to 3) of std_logic_vector(1 downto 0); signal array_mux : t_array_mux; begin array_mux(0) <= d0; array_mux(1) <= d1; array_mux(2) <= d2; array_mux(3) <= d3; m <= array_mux(to_integer(unsigned(s))); end rtl; Для шины адреса и данных - необходимых для чтения из памяти (BRAM) Интересуют идеи по реализации.

-

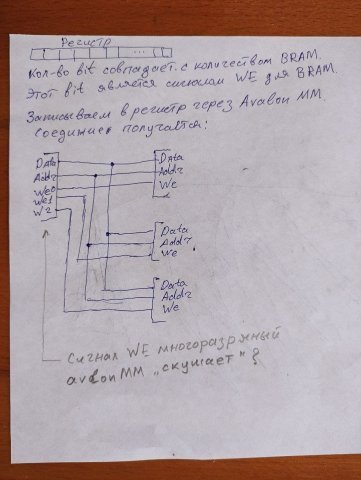

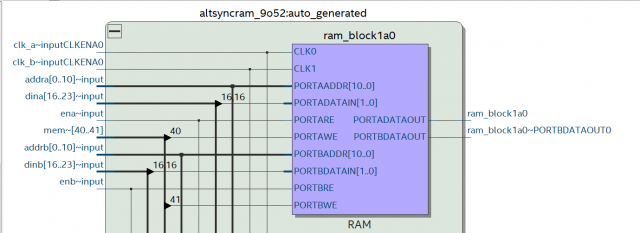

Насчет возможности с помощью Core Generator я знаю... Начал сомневаться что описать память с Chip select можно - только через Core Generator Вот еще архитектура для записи - вложение

-

описание двухпортовой памяти с CS

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день подскажите пожалуйста как правильно описать двухпортовую память с CS(Chip select) (altera) такое решение library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use IEEE.NUMERIC_STD.ALL; entity bram_tdp is generic ( DATA : integer := 32; ADDR : integer := 12 ); port ( -- Port A a_clk : in std_logic; ena : in std_logic;-- a_wr : in std_logic; a_addr : in std_logic_vector(ADDR-1 downto 0); a_din : in std_logic_vector(DATA-1 downto 0); a_dout : out std_logic_vector(DATA-1 downto 0); -- Port B b_clk : in std_logic; enb : in std_logic;-- b_wr : in std_logic; b_addr : in std_logic_vector(ADDR-1 downto 0); b_din : in std_logic_vector(DATA-1 downto 0); b_dout : out std_logic_vector(DATA-1 downto 0) ); end bram_tdp; architecture rtl of bram_tdp is -- Shared memory type mem_type is array ( (2**ADDR)-1 downto 0 ) of std_logic_vector(DATA-1 downto 0); FUNCTION initialize_ram return mem_type is variable result : mem_type; BEGIN FOR i IN ((2**ADDR)-1) DOWNTO 0 LOOP result(i) := std_logic_vector( to_unsigned(natural(i), natural'((DATA)))); END LOOP; RETURN result; END initialize_ram; shared variable mem : mem_type := initialize_ram; --shared variable mem : mem_type := (others => (others => '0')); -- := initialize_ram; begin -- Port A process(a_clk) begin if(a_clk'event and a_clk='1') then if ena = '1' then -- if(a_wr='1') then mem(conv_integer(a_addr)) := a_din; end if; a_dout <= mem(conv_integer(a_addr)); end if; -- end if; end process; -- Port B process(b_clk) begin if(b_clk'event and b_clk='1') then if enb = '1' then -- if(b_wr='1') then mem(conv_integer(b_addr)) := b_din; end if; b_dout <= mem(conv_integer(b_addr)); end if; -- end if; end process; end rtl; мне кажется не коректным т.к. не задействуется порт CS (technology viewer) - вложение. Основной вопрос как осуществить доступ к нескольким портам памяти (BRAM) имея один вход: Шина данных Шина адреса Сигнал WE Решение через сигнал WE мне кажется не очень быстродейственным - большой mux. Мне надо соедениться с 16 памятями - чтобы их инициализировать Можно конечно сделать pipeline. Может у кого есть более оригинальные решения? PS Для avalon MM для соединения мастера со многими слейвами MM - все намного проще "Chip select signal to the slave. The slave port should ignore all other Avalon signal inputs unless chipselect is asserted."