rloc

-

Постов

3 155 -

Зарегистрирован

-

Победитель дней

12

Сообщения, опубликованные rloc

-

-

Сейчас у ее профиля нет никаких ограничений

Пару месяцев назад у меня были другие сведения. Хорошо, что ошибся. Велкам.

-

под другим ником

Попрошу воздержаться от комментариев. Ко всем относится.

-

Уважаемые администраторы, есть у нас уважаемый пользователь Xenia, не пора ли вспомнить о возвращении в ряды писателей?

-

К основной управляющей фпгашке через параллельную шину цепляется цпльдэшка, которая сериализует управляющую посылку.

Если управляемые микросхемы находятся рядом, то я не сторонник таких манипуляций. Далеко передавать (понятие относительное) - тут есть над чем подумать. Мощность TTL подобных сигналов может натворить чудес. Совсем недавно, думая над такой задачей, решил попробовать LVDS - размах напряжений можно сделать около 200 мВ, вместо 3 В. И промежуточные мелкие фпгашки будут очень даже кстати, со скремблированием, мешированием и сериалайзингом.

Всех женщин поздравляю с праздником! Вдруг стало любопытно, есть ли такие, которые читают нашу ветку?

-

Понятно, что при этом в 2 раза увеличивается коэффициент деления в петле.

Не думаю, схема при этом фактически работает по передним и задним фронтам. Формально ничего не меняется, но схема становится удобнее в реализации и более предсказуемой.

Спрашиваете, зачем ЦАП? А что вместо него?Возможно я немного избалован, но если есть ЦАП (и даже не один) невольно возникает вопрос: а почему его не использовать по прямому назначению (прямой синтез)? По вашей статье вижу PDS базируется на идеи Босселаерса, где был использован ЦАП в гордом одиночестве. Я бы даже предложил поначалу отталкиваться от этой идеи, как более простой. В той схеме на выходе ЦАП также формируются импульсы, среднее значение которых является управляющим для ГУНа. Ладно, думаю, пусть есть ЦАП, но почему тогда нельзя на его выходе сразу формировать управляющее напряжение без импульсов? Оказывается, по-другому не получается, изначально нет информации о разнице фаз между двумя сигналами. И опять стопорюсь на этом моменте, в мире давно опробована и широко используется связка TDC-DAC, где сначала разницу фаз определяет преобразователь время-цифра и далее на медленном ЦАП формируется управляющее напряжение. Чем этот вариант хуже? Двигаюсь дальше, преобразование высокочастотных импульсов на ЦАП в напряжение на DC похоже на работу ШИМ или дельта-сигма модулятора, когда разница по частоте (сужение полосы) позволяет увеличить разрядность (точность управляющего напряжения). Другими словами, разрядность ЦАП теоретически можно уменьшать, в пределе до 1 бита (отсутствие ЦАП). Почему это свойство не было использовано в PDS или у Босселаерса? И вопрос о распараллеливании остается открытым, способность взаимодействия со скоростными технологиями на низких частотах?

Как это он решается на конструктивном уровне? И а какой скорости передачи? На 100 Mb/s и выше решается?Конструктивный уровень - "сендвич" компоновка управлялки и СВЧ, трассировка линий во внутренних слоях, промежуточная буферизация-фильтрация, прошивка ПП виасами, территориальное разнесение ... С интегральными микросхемами управление выше 20 Mb/s пока не встречалось, пробовал свое на 400 Mbyte/s - не видно вооруженным глазом.

схем рисовать принципиально не буду из-за того, что здесь присутствуют участники из других государств.Предлагаю шифроваться, как лет 30 назад у меня был советский компьютер (Электроника-85 если память не изменяет), где маркировки микросхем звучали как "капуста", "репка" ...

-

Можно заменить на XOR.

Не ожидал услышать. Можете нарисовать новую схему с элементами XOR ? И сразу следующий вопрос: зачем ЦАП в этой схеме? В двух-трех словах. Пытаюсь осознать концепцию PDS в общем виде, преодолеть отторжение сборной разношерстных элементов на подсознательном уровне.

-

С метастабильностью всё в порядке. Каждый парциальный детектор работает в середине линейного участка его статической характеристики. См.файл с описанием макета, приложенный к сообщению №2327 на стр.156.

По измерениям на макете не вижу характеристик линейности. Если детектор работает на линейном участке, его можно заменить на схему без обратной связи, меньше поводов сомневаться в линейности характеристик.

Да, абсолютно одинаковые. Да, будет работать.Красота.

Долго думал, как рандомизировать управляющую цифруПо SPI? Вроде на конструктивном уровне решаемый вопрос, как мне кажется.

тупиковые ветки синтезаПо косвенному синтезу рано ставить точку. Возможности по всем параметрам далеко не исчерпаны, я бы сказал далеки от потенциальных. В первую очередь по скорости перестройки, без экстремального расширения полосы.

-

Обратная связь в RS-триггере: чему она мешает?

Метастабильность на учаске характеристики, вблизи которого работают многие ФД. В цифровой схемотехнике стараются избегать асинхронных связей, где найти ошибки крайне сложно. Синхронность проекта считается хорошим тоном. Насколько асинхронность предсказуема в PDS, можете ответить только вы. Это поверхностные вопросы, без вникания в сложность структуры PDS.

Какую неравнозначность вы имеете в виду?На выходе каждого парциального детектора абсолютно одинаковые сигналы, без учета временного положения? Если оставить только один детектор, остальные исключить, схема будет работать с пропорционально худшими характеристиками?

-

RS-триггеры или XOR (разницы особой нет). Это проще, нет мёртвой зоны, частотные свойства выше.

У RS-триггера обратная связь есть, посмотрите пожалуйста структуру, тактируемый он или нет - это другой вопрос. Фазовые детекторы на RS-триггерах работают на нулевом фазовом сдвиге, на XOR - при сдвиге около 90 град, и он по своему принципу ближе к аналоговому смесителю.

Но это всё-таки факт (см.прилагаемую статью).Эту статью знаю, ее я и приводил ранее. Там речь о равнозначном сложении. У вас пока не вижу равнозначности по всем выходам.

-

Не понял что за «мёртвая» зона в RS-триггерах? Поясните, пожалуйста.По вашей ссылке там речь идёт о мёртвой зоне в ЧФД. Но при чём здесь RS-триггер? – в нём мёртвой зоны нет.

Мертвая зона в ЧФД в первую очередь связана с неопределенным состоянием триггера, при малой разнице между фазами сигналов, из-за задержки обратной связи сброса/установки. Схема накачки скорее имеет нелинейность, чем неопределенность, и также важна. Мне запомнился момент, когда Шаманъ говорил о неудачных попытках применения триггера с обратными связями на дискретных элементах в качестве ФД, и поэтому пришлось перейти на схему XOR, в которой этих недостатков нет.

Да, увеличение количества расщеплённых фаз и, соответственно, парциальных детекторов приводит к снижению шумов из-за их некогерентного сложения.Для меня это не столь очевидный факт.

На выходе их сигналы суммируются, так что результат получается как если бы детектор в целом работал на исходных высоких частотах.Процесс умножения, поднятие частоты, всегда непростой, не легко улучшить или сохранить шумы и спуры, особенно при большой разнице между конечной частотой и частотой ФД. Есть много мешающих факторов: ЭМС, УПТ ...

-

С ADFкой может быть один нюанс - у нее на выходе очень короткие импульсы

Импульс меньше периода?

Подскажите по микросхемам дискретных фазовых детекторов. Кто-нибудь имел дело с SY100EP140L которые теперь микрочип?Вроде должны быть аналогичны MC100EP140, а там схем применения много.

Как они по фазовым шумам и какую к ним аналоговую обвязку надо для коммутации токов перед фильтром?Зачем городить свой чарджпамп на выходе? Дифференциальными методами хорошо убирается постоянная составляющая, как в HMC439. По фазовым шумам думаю, как у многих ECL микросхем - в ближней зоне хорошо, в дальней - около 150-155 дБн/Гц, т.е. использовать на низких частотах не выгодно.

Имеет ли смысл собирать PDS на нескольких дискретных PFD c двоичным соотношением токов в каскадах? Какой выигрыш можно получить в зависимости от числа каскадов?Да, если применять в дискретном варианте PDS, есть некоторый смысл, как замена RS-триггерам. Как всегда, головная боль с этими триггерами - "мертвая" зона. А вот с количеством, вопрос действительно интересный. Виталий как-то писал, что увеличение количества должно приводить к суммарному уменьшению шума. Но это верно для случая равнозначного вклада всех парциальных детекторов, в ином случае можно получить противоположный эффект. И чтобы это понять, нужно глубоко вникать в структуру, как тау.

А у меня еще вот какой неудобный вопрос к Виталию: позволяет ли структура PDS распараллеливать операции? Как правило внутри любого DDS цифровая часть работает на низкой частоте и только за счет одновременной работы 2-4-8-16-32- ... ядер удается сформировать данные на единицах/десятках ГГц. И очень часто, именно для DDS, развитие идет не по пути повышения технологии (уменьшения nm), а за счет увеличения количества ядер, потому как аналоговая часть, имеет большой запас по частоте.

-

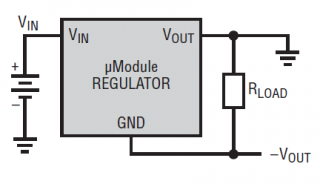

На -5V тоже можно найти готовое.

Любой понижающий DC-DC с большим входным напряжением подойдет. Аналогично схеме, как писал выше alekssan

Более подробно у Linear, Design Note 1021

Не знаю, может, не обращать внимания, что надо -5.2V, будет работать, что ему сделается, компаратору.Для аналоговых вещей после DC-DC хорошо поставить LDO, на минимальную дельту, чтобы не городить громоздких фильтров, поэтому лучше заложить -6V.

Есть вариант обойтись другим компаратором, тому не надо минуса.Часто не нужен компаратор в широком смысле, тогда проще заменить усилителем-ограничителем, формирователем тактового сигнала, а там и шумы получше, и быстродействие.

-

Конечно, можно было бы экспериментировать и дальше

В макетной части могу помочь, по схемотехнике, печати. Будем надеятся, что найдется спонсор.

-

Но если надо 2.8 мм именно на таких же feed thru, то берете 0-омную, надеваете на нее тефлоновую трубочку и высверливаете отверстие в корпусе под 50-омный коаксиал.

Честно, я тоже не сторонник такой комбинации, нет уверенности в землянном контакте печать-перегородка. Знаю 2-3 фирмы, делающие боард-ту-боард коаксиальные разьемы, но они устанавливаются с обратной стороны и их не утопишь..

Ещё один приём (чтобы не увеличивать размер по высоте) – утопить цангу в плате. В многослойке отверстие делается двухуровневым (это обычная технологическая операция в производстве PCB), так что цанга ложится заподлицо с обратной стороны платы.Backdrilling? Без металлизации, пайка со стороны компонентов? Задам еще уточнющий вопрос, в голове пока с трудом укладывается технологическая цепочка. Терминалы должны выступать с лицевой стороны платы и пайка отдельной операцией вручную? Или, второй вариант, - вставляются с натягом с пастой и пайка со всеми компонентами вместе?

-

Использованы именно матрицы резисторов: 8 штук по 4 резистора в каждой.

Между самими матрицами есть разброс и не малый. Допустим 1%, а это считается высокой точностью, меньше точности младшего разряда 7-битного ЦАП. Есть матрицы резисторов более 4 шт, вот о чем говорю. Пусть будет 5 %, но главное внутри матрицы будет точнее. Нельзя ли в опытном образце сделать резисторов меньше?

Но влияет также и временнОе рассогласование: 32 дорожки разной длины от FPGA до резисторов. Возможны также и искажения сигналов с выходов RS-триггеров в FPGA.Дорожки можно подровнять до 0.5 мм, решаемая задача. Триггеры желательно выносить за FPGA, делить цифровую и аналоговую части.

-

Если автор темы не против нескольких сопутствующих вопросов по ЭМС, то продолжим.

Получите и распишитесь. 110 mils ~ 2.8 мм. Видел и поменьше где-то.Какие терминалы для PCB можно использовать? Интересны сквозные, допускающие большой ход по высоте и установку с разных сторон. И какие возможны варианты коаксиальных переходов для передачи СВЧ с одной стороны бутерброда на другой при заданной толщине, в том числе 2.8 мм?

Буферирование Vtune повторителем на ОУ тоже портило спектр.На FET или BJT был вход усилителя?

-

Сейчас пришла в голову простая и вместе с тем нетривиальная идея использования для полной рандомизации элементарной RC-цепочки, управляемой цифровой рандомизацией.

Можно немного поподробнее? Не очень понятно о чем речь.

-

Шум – это шум дробности из-за неточности ЦАП. Без дробности шум на порядок ниже. А точным ЦАП не сделать, поскольку резисторы «размазаны» по печатной плате.

Распределенность положения думаю роли не играет, частоты достаточно низкие. Какая точность нужна? Есть матрицы резисторов. Почему спрашиваю, делал мультибитный сигма-дельта модулятор на частоту около 100 МГц, 8 резисторов, точности хватало, внутри одной сборки разброс - доли %.

-

Чтоб не запутаться, схема включения для ADF4002 будет такая?

В целом, да. По уровням и задержкам еще посмотреть. Для КМОП по входу можно добавить резистивный делитель на Uпит/2. А по задержкам чуть интереснее CPLD, легко добавить логический элемент, частота 400 МГц, управление фазой и скважностью (внешняя синхронизация).

Красивые шумы, однако, получаются...По-моемому сейчас все производители OCXO/VCXO в качестве активных элементов широко используют похожую логику: Magic Xtal, Morion, Crystek, Abracon ... Сомнений нет.

-

Ну да ладно, проехали.

Понимаю, что VCO ляпнул, умеет он.

К Вам вопрос, пока Вы тут появились. По поводу очистки сигнала внешним стробированием. Правильно ли я понимаю, что если взять плохенький по шумам делитель, но удобный в использовании (например, ADF4002), то я могу улучшить его шумы, подключив на его выход D-триггер (tiny logic), clock которого подключу к клоку ADF? Или я что-то пропустил здесь? В чем тут фишка?Мне показалось вам эта фишка хорошо знакома, по соседней ветке с ЭМС ) Идея очень простая, вы ее даже проговаривали и осмысливали. Добавочное дрожание фазы на выходе любого делителя определяется тремя вещами: технологией изготовления микросхемы, длинной пути от тактового сигнала до выхода и внутренней ЭМС. Внешний триггер дает нам простор в выборе технологии и сокращает задержку от клока до выхода. В "правильных" делителях внутри обязательно будет стоять стробирующий триггер. Первый пример, что пришел в голову - NB7N017M, делал когда-то давно на нем дробный делитель с внешним управлением. Виталия никак не могу уговорить на внешнее стробирование, посмотрите на его схему, FPGA фактически напрямую связана с аналоговой частью, шумы беспрепятственно пролезают.

Сейчас поищу ссылку, где на приборе замерил разницу со стробированием и без, ее и можно в закладки положить.

Кстати D-триггер любой подойдет, пробовал и National, и TI, и NXP серий AUP, AUC, LVC, много их. Это что касается КМОП технологий. По остальным не знаю.

Тут беседа была:

https://electronix.ru/forum/index.php?showt...st&p=993484

1-ый случай - тактовая частота 100 МГц разветвляется на CPLD и внешний триггер, делится на 5 на CPLD и подается на D-вход триггера

2-ой случай - сигнал снимается напрямую с выхода CPLD

-

Добавлю свои пять копеек.

А кому удалось решить проблему наводок по цепям управления?В целом подход как у Александра:

1. Поставить строенный ключ (Clock, Data, CS), который будет обрубать цепи управления по постоянке (мегагерцы), когда они не используются.2. В эти цепи (Clock, Data, CS) включить по LFCN-у, который (если правильно выбран) будет блокировать СВЧ и не обрезать фронты.

Но это всё навороты, за которые я бью по рукам.

Первым пунктом ставлю логику без клока с минимальными емкостями по входу и выходу, соответственно лучшей развязкой между входом и выходом на высокой частоте (если память не подводит - из серии AUP). Во втором пункте - аналог LFCN, но в более компактном исполнении, Murata например. Если управление с FPGA, без таких наворотов к сожалению не обойтись. Размышления такие - на низких частотах работает логика (ключевой режим), на высоких - ФНЧ.

От DC-DC развязка - разделением земель, после DC-DC - LDO по аналоговым питаниям.

-

Если PDS, то он есть, см. приложенный файл. И там спуры -70 дБн

Хорошо, будем считать первой итерацией, алгоритм работает, спуры низкие. Следующий вариант - шумы (2 ЦАП с суммированием например, продумать изоляцию от FPGA, как источника шума), и по-возможности более высокая частота работы FPGA. Важно посмотреть на спуры вблизи кратных частот.

-

Но не настолько лучше, чтобы заявлять, что кроме DDS ничего и никому больше не нужно.

Я бы поостерегся слов лучший, незаменимый - это крайности и ни к чему хорошему они не приводят. К PDS это также имеет отношение. Да, возможно и нужно для продвижения технологии где-то на 10-20 дБ лучше, чем любое другое решение, но это крайне мешает на начальном этапе развития. Пусть будет макет на коленке, со спурами 57 дБн - для меня приятно видеть железку, дальше посмотрим, что с этим делать.

Как Вы оцениваете способности Миландра?Никак, не нравится такой путь развития, дорогостоящий и рискованный. Только в кооперации со студентами.

-

Какие глубокие завязки с Ванкувером. Кто бы мог подумать? Вместе с Виталием гадал.

Кто старое помянет ...

Синтезаторы частот. От концепции к продукту.

в RF & Microwave Design

Опубликовано · Пожаловаться

Спорный момент, кому какие уровни нужны и считать ли гармоники за спуры (любой ГУН хуже по гармоникам ЦАП). А какие спуры будем считать низкими?

Действительно пробовали? Из любопытства спрашиваю. Глубоко вникать в детали нет смысла, важнее понять потенциал, на что можно рассчитывать.

Детально не занимался этой темой и привести сходу ссылку на последние достижения не могу. Общее представление дает следующая статья:

Michael H. Perrott, Tutorial on Digital Phase-Locked Loops

ЦАП там не используется, его функции берет на себя DCO - генератор управляемый переключаемым набором конденсаторов C-2C-4C-8C- ... Общая идея от этого не меняется: преобразование фазы в цифру (TDC, ADC), цифровая фильтрация и цифровое преобразование в частоту (DCO, DAC+VCO). Больше всего в этой схеме мне нравится потенциал - знание фазы дает полный простор для творчества, в цифровом виде намного проще сделать адаптивный алгоритм фильтрации, чем в аналоговом. Не вижу другого способа повысить скорость (на порядок), без потери устойчивости.

Как в данном случае сделать, мне трудно сказать, говорю о потенциальных возможностях. Многоразрядный быстрый ЦАП избыточен в PDS.

Если бы вопросы просто решались некогерентным сложением, работали бы в области кГц и никаких интегральных технологий не надо. Поэтому и намекаю, как перейти на более высокие частоты? Что с того, что в современных ЦАП частоты преобразования превышают 10 ГГц? Цифровая часть остается работать на низких частотах, на порядки более низких. Можно ли сравнить PDS с 32 парциальными детекторами на 400 МГц с DDS, работающим на 400*32=12.8 ГГц за счет распараллеливания?