rloc

-

Постов

3 155 -

Зарегистрирован

-

Победитель дней

12

Сообщения, опубликованные rloc

-

-

Собственно, я не против ЦАП как такового. Только вот ЦАП получается самым слабым звеном в DDS (частота клока, линейность, кол-во битов, цена и т.д.), не находите?

Ах, вот оно что :) Попробую развеять мифы, легенды, фобии. Клок - алгоритм формирования синуса хорошо распараллеливается, пусть даже частота ЦАП будет раз в 8/16/32 выше FPGA, биты - в алгоритме формирования синуса можно использовать аппроксимацию по Тейлору (закладывается в стандартные библиотеки), больших таблиц не нужно, ресурсов по современным меркам хватает 1%-10% от младших семейств FPGA, разрядность около 20 бит при 48 битах частоты, что на текущий момент вполне достаточно, линейность - немного посложнее, но как видели выше, вопрос решаем, ресурсов поболее, в младшие семейства быстрых FPGA уложиться можно, цена - согласен, высокая (в основном ЦАП, при оптимизации по стоимости), но когда начинаешь считать, сколько этот "кубик" может заменить/упростить, по себестоимости выходит немного дороже QS (сравнение конечных изделий), потребление - много, чем-то надо жертвовать.

-

Там же потом Александр предлагает поделить частоту пополам и построить меандр.

Все эти проблемы, если я правильно понял, исчезнут после создания меандра. Нет?

Нет, конечно.

-

Может RC-цепочка с варикапом?

Из-за нелинейности варикапа потребуется калибровка, зачем? RC-цепь или эквивалент лежат в основе большинства TDC/DTC. Как уже писал, вариант с интегрированием не подойдет по быстродействию, потому что для формирования нужна более высокая частота, чем частота выдачи данных. В варианте с переключаемыми R/C получаем матрицу элементов, такую же по сложности, как в ЦАП, только здесь есть одна неприятность - при больших задержках, малых токах, получаем высокий шум/джиттер. В ЦАП вклад младших разрядов, малых токов, в общую мощность сигнала не существенный, шум не увеличивается.

Согласен. Только где? Я имею в виду, что наиболее ценная информация об амплитуде находится в районе перехода через 0, а именно там она обычно и обрезается при реконструкции всей синусоиды.В нуле синусоида не обрезается, реконструирующий фильтр в нужный момент времени заставляет пересечь ось X. Говоря про размен, имею ввиду три параметра шум-спуры-полоса и ЦАП позволяет гибко играться между ними. В глобальном смысле ЦАП выгоднее универсальностью своего применения, большей востребованностью, технологии развиваются быстрее, больше фирм заинтересовано в выпуске.

А почему именно синуса?Пила имеет больше гармоник, на нелинейностях все эти гармоники будут интермодулировать с другими частотами (тактовой), и на выходе вылезет больше спур в рабочей полосе.

А если пилу (или что-то ещё, не знаю – мы ведь сами задаем функцию в LUT)? Получится прямая через две точки.А чем кстати легче интерполировать в аналоге: прямой или синусом?

-

Симбиоз DDS и SRD?

Зачем же так буквально воспринимать :) В отдельности. Совместно можно, для решения вопросов со смесительными спурами, но это уже совсем другая история.

-

Обязательно перед усилителем-ограничителем нужен фильтр. Если усиливать (нелинейно) выход ДАС до фильтра , то в полезную полосу попадут комбинашки с соседними зонами и пройдут через фильтр.

Согласен, выше писал, потом пропустил. Надеюсь на понимание.

А почему надо останавливаться? Возможна ли дальнейшая обработка сигнала такого варианта DDS?Двигаемся дальше. С таким простым элементом, как ЦАП, еще много не изучено, а с ДНЗ - вообще не паханное поле, не смотря на многолетний всемирный опыт работы с этим элементом.

-

В принципе, для начала я хотел посмотреть, насколько мог бы упроститься ЦАП, если ему не надо вырисовывать синусоиду.

В большинстве случаев ADC/DAC заменяют TDC/DTC (Digital to Time Converter). Поиск в интернете привел к такому же выводу:

PICOSECOND-ACCURACY DIGITAL-TO-TIME CONVERTER FOR PHASE-INTERPOLATION DDS

Поэтому присоединяюсь к гипотезе VCO:

И какая-то программируемая линия задержки.Есть два варианта DTC: на цепочке логических элементов, и на базе интегрирующей цепи. Первый шумный вариант отметается, второй по быстродействию проигрывает DAC. Возможно есть нечто гибридное, но очевидно не такое простое, чтобы прямо сейчас потягаться с DAC. В любом случае, там где возможно, нужно использовать ADC/DAC, лишней информация об амплитуде точно не будет, а скорее всего станет главным козырем в размене одних характеристик на другие.

Или упрощенно можно сказать, что ЦАП играет роль некоего фильтра-усреднителя или устройства, "вычисляющего" эту точку А - если хотите.Поправлю, интерполятором-реконструктором выступает ФНЧ и, что важно, это звено без потерь. Поэтому, как разработчик, остановился бы на варианте FPGA -> DAC -> Усилитель-Ограничитель

-

Хорошо. Давайте посмотрим с другого угла. Допустим, Вам нужно сконструировать DDS, который должен иметь на выходе не синусоиду, а меандр. Ну - или как вариант - короткие импульсы не обязательно равной ширины, но с привязкой фронтов к периоду синтезируемого сигнала (дальше можно подать на D-триггер и получить чистый меандр на половинной частоте). Как бы Вы решали такую задачу?

Начинаю терять нить рассуждений :) Давайте вернемся к первоначальным условиям:

1. Есть тактовая частота Fclk

2. FPGA

3. Можно использовать дискретную логику, пассивные компоненты

Стоит вопрос: можно ли сформировать частоту Fdds < Fclk/2 в виде меандра/импульсов в общем случае не кратной тактовой, чтобы она по спектральной чистоте основной гармоники была сравнима с чистотой по выходу классического DAC?

Считаете меня мезантропом? Пересчитайте людей, которых вы терпеть не можете!Вычитал из википедии: мизантропия

-

Мне представляется, что DDS содержит довольно большое число логических элементов (чтобы построить аккумулятор и т.д.), которые в свою очередь сами содержат несколько транзисторов.

Вот о чем речь была :) Дело в том, что данные с FPGA стробируются в DAC, тем самым путь тактовой частоты сокращается: Fdac -> входной усилитель-ограничитель -> регистры данных -> источники тока. Таким же образом внутри многоразрядных счетчиков-делителей по выходу ставят регистр, стробирумый входной частотой, и путь от тактовой частоты до выхода уменьшается. Объем цифровой части FPGA в составе DDS не оказывает никакого влияния на выходные шумы. Буферизация в DAC позволяет довольно эффективно разделить цифровую и аналоговую части.

Нет, я именно о самом, что ни на есть DDS-е. Только лишь убрать вторую составляющую в Вашем уравнении DDS=FPGA+ :)ЦАП позволяет сконструировать синусоиду (или другую желаемую форму). А нужна ли синусоида на выходе? Если предполагается дальше вверх умножать, то вполне подойдет и прямоугольник. При этом ЦАП вырождается в логический элемент с 0/1 на выходе.

Т.е. Вы предлагаете сократить разрядность DAC до одного бита? :) Чудес не бывает, либо мы получим счетчик-делитель, либо СПМШ+спуры астрономические.

-

На практике у Виталия сейчас такой возможности нет. Так что некоторые комментарии Виталия больше несут элемент отчаяния.

Да, похоже на отчаяние. Но, что самое интересное, возможности у Виталия есть, и финансовые и конструкторские. По тому макету, что приводил Виталий, большой бюджет не нужен, дорогостоящей и дефицитной комплектации нет, по моим оценкам до 500$ уложиться можно. Сказать, что это огромная сумма для человека пенсионного возраста нельзя, при условии, что Виталий днем и ночью думает о воплощении идеи в жизнь. По конструкторскому вопросу виден серьезный пробел, восполнить который формально можно без финансовых затрат, имея в распоряжении достаточно свободного времени. А иначе, я считаю, смысла продвигать PDS никакого нет, потому что понять где и какие шумы образуются невозможно. В любой разработке должен быть человек, понимающий теорию и физику протекающих процессов целиком, всего изделия. Так, чтобы один человек четко знал как "пришить пуговицы", другой - как "пришить карманы", и в итоге костюм сидел идеально - не получится. В этом и есть обреченность идеи. Взять к примеру Вас, Александр. Пришла бы идея QuickSyn'а без того, чтобы "пощупать" усилители, смесители, ФАПЧ, делители, умножители ... ? Пусть даже и сейчас Вы не держите паяльник в руках. Таким образом и родилась, заслуживающая уважения, проработанная по всем параметрам структура.

Виталий, ответьте пожалуйста, ради чего Вы изобрели PDS? Работодатель поставил перед Вами такую задачу (желательно озвучить цифры) или Вы сами придумали условия?

А нужен ли в DDS-e ЦАП? :)Загадочно поставлен вопрос. Формально, разрядность ЦАП в сочетании с линейностью определяют широкополосную спектральную плотность шумов. Без ЦАП представить прямой синтез сложно. Для узкой полосы вопрос решаем - несколько резисторов + сигма-дельта полосовая модуляция позволяют разменять полосу на бОльшую разрядность (меньшую спектральную плотность шумов).

-

Они тоже решили проблему очистки от спупов?

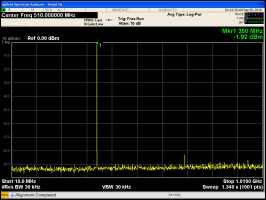

Более высокочастотный ЦАП, кратность с тактовой больше при одинаковых выходных частотах, но посмотреть на приборе в широкой полосе с большой динамикой нельзя RBW >= 30 кГц, под шумами спуры. Виталий, макет с новой микросхемой у вас перед глазами, меняйте частоты, разрешения, смотрите интересующие вас параметры.

Что-то похожее на картинки Сергея Бельченко.Бельчиков

-

Прикольную фишку аналог девайсес придумала: можно дистанционно управлять макетной платой DPG с подключенной AD9164 и делать скриншот с PXA.

http://labs.analog.com/ad916x/index.aspx

-

Ответил в личном сообщении.

-

L-диапазон, сетки частот нет (насколько мне не изменяет память), литерность может быть обеспечена выбором кварцевого генератора.

-

И всё же, каковы должны быть требования к шумам и спурам для радиолокации? К примеру, для того же комплекса "Утёс-т".

Порядка 70-80 фс в интегральном виде ФШ + спуры в диапазоне от 100 Гц и до полосы приемника. Конкретно на максимальный уровень не накладывается ограничений. Один большой спур может оказаться лучше кучки мелких.

-

Не понял, где ж там о необходимых характеристиках синтезаторов частоты?

Радиолокация и измерительная техника - два самых крупных потребителя источников с низкими фазовыми шумами. "Утес-Т" - трассовый радиолокационный комплекс. Принцип работы основан на излучении пачки когерентных импульсов, приема отраженного сигнала и выделения сигналов от целей. В трассовых станциях угол места не важен, луч в этой плоскости широкий, а в азимутальной - узкий. Поэтому при приеме отраженного сигнала всегда присутствует сигнал от цели и от подстилающей поверхности. За счет излучения и приема пачки когерентных импульсов, появляется возможность селекции по частоте Доплера, алгоритм называется СДЦ. Фактически стоит задача разделения двух сигналов с малой отстройкой по частоте, причем один из них может быть значительно больше по амплитуде (от подстилающей поверхности). Уровень фазовых шумов бОльшого сигнала не должен задавить слабый сигнал. На брифинге показаны результаты работы алгоритма СДЦ при низком уровне фазовых шумов зондирующего сигнала. Слабые отражения от БПЛА (ЭПР меньше 0.1 м2) хорошо видны на экране радара. Конкретных цифр по фазовым шумам там конечно не приводится, на то есть методика расчета. Это то, с чего начиналась моя проф. деятельность, и я рад, что станция работает надежно. Сейчас по всей стране работают метеорадары, чувствительность которых позволяет видеть кучевые облака на дальности в сотни км.

Пример привел, в связи с появлением новостей.

-

К вопросу о необходимости низкого уровня фазовых шумов и практическое применение. Брифинг Минобороны и представителей ВПК о первичных радиолокационных данных по MH17 (данные с трассового гражданского комплекса, отметки от метеобразований и БПЛА из композитных материалов на дальности 140 км):

-

PDS можно разбить и на две микросхемы. В чём проблема? В одной - чисто цифровая схема, во второй - аналоговая с ЦАП.

Разбить не так и просто, многократно Вам предлагали это сделать на макетной плате. ЦАП у Вас не простой, с двумя клоковыми доменами. Данные от каждого домена нужно тянуть к аналоговой части отдельными линиями, чтобы стробировать их в аналоговой части. Итого, про предварительной оценке, 32 + 32 = 64 линий, не мало, особенно по сравнению с обычным ЦАП. Это уже серьезное препятствие к оптимизации по стоимости, потреблению, быстродействию.

-

Судя по спурам- пока не особенно радостно.

Видны смесительные спуры. В той или иной степени они будут на выходе любого ЦАП. По косвенным признакам, эту микросхему начали разрабатывать достаточно давно, для одного военного заказчика. И задачи получить сверхвысокие параметры у них не было.

Вот интересно, если овернайквист находится за пределами рабочих частот балуна, то что там будет творится во второй- третьей зоне?Я бы не стал рассчитывать на зоны выше первой. С увеличением частоты по выходу ЦАП спуры растут быстрее закона 20logN, есть некоторая граница, после которой выгоднее умножать - это видно и по нашим измерениям и по схеме UXG. Жаль, нет доступа к полной полосе AD9162, с 6 ГГц до 12 ГГц повышение идет за счет интерполяционных фильтров, ЭМС которых с аналоговой частью может сказаться не лучшим образом.

Конечно, PDS лучше. Проще, дешевле, экономичней по потреблеиню да и спектр не хуже.С уверенностью говорю, реализовать спектральные характеристики на одной микросхеме со сравнимыми параметрами или лучше невозможно, вне зависимости от того, какой алгоритм используется. Все упирается в ЭМС внутри кристалла, и с повышением частоты проблема становится острее. Если на макете невозможно реализовать разделение аналоговой и цифровой частей, надеяться, что получится в интегральном виде не стоит.

-

Опубликовано · Изменено пользователем l1l1l1 · Пожаловаться

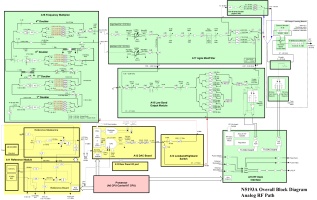

Думаю не помешает схема перед глазами, чтобы представлять общую структуру аналоговой части N5193A.

Получается, что так. Рабочий диапазон 0.65 ГГц - 1.5 ГГц при тактовой 6 ГГц. Смело они оставляют выход ЦАП без полосовой фильтрации.Т.е на рисунке "волохатость" исходного ДДС, вырезанная полосовым фильтром после умножения?

Полоса остается широкой, возможны все виды модуляции. Ранее думал, в UXG есть своя "изюминка".схемы очистки спектра узкополосны и надо менять блок-схему и частотный план "нового UXG"?

Сложно найти пользователей у нас в стране, до недавнего времени прибор попадал под санкции, пока не появились версии с ограниченной скоростью. Всегда в таких случаях задаю вопрос: кто будет закладывать прибор в серийное изделие?Может кто ковырял прибор и влез анализатором спектра в схему? -

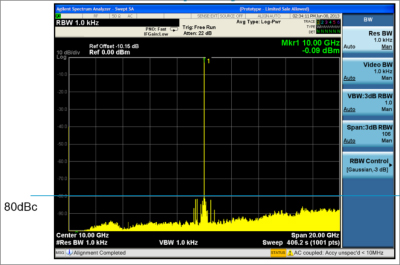

Добавлю к предыдущему посту Сергея. Обработка - аппаратно-программная. Если сделать поправку на пролаз УКВ станций, типичных спур FSW с уровнем -120 дБн, неидеальность опорного источника, конечную ЭМС на уровне -105 дБ ... -110 дБ от далеко стоящего маломощного ГК и его гармоник, то остаются спуры смесительного характера, почти без проигрыша в шумах. Смотрим, что получается в UXG на 10 GHz (спан 20 GHz):

После приведения к одной частоте - близко, и без использования эксклюзивных технологий, на широкодоступных компонентах. Вижу у Keysight стал доступен сервисный мануал, где подробно расписана структура.

P.S. Пролаза источников DC-DC не видно, можно смело применять.

-

А зачем?

Во-первых, реабилитировать хорошую умножилку, незаслуженно забытую, и под авторитетным влиянием рискующую попасть в долгий ящик. Во-вторых, она может быть сделана проще и по общим ощущениям более предсказуемой (как мне говорили, ближайшие гармоники с делителя имеют бОльший разброс по амплитуде). В условиях скудности выбора отечественной элементной базы (в некоторых случаях актуально), умножение на ДНЗ - это реальный выход из ситуации, емкость меньше, выше частотная граница, при всех прочих равных условиях (технологиях) с другими элементами. Как выяснили здесь на форуме, ДНЗ можно заменить на дешевые и более доступные аналоги, поэтому идеология сборки "на коленке" на элементах из Чип-и-Дипа, играет не маловажную роль. Есть предположение, что на pin-диодах разброс должен быть меньше, технология проще.

Или переводя в количественную плоскость (иначе ни о чем) – сколько Вам нужно гармоник? Не абстрактно (чем больше, тем лучше, и равномерно, и равной амплитуды и т.д.), а конкретно – сколько?Тенденции развития измерительной техники и не только таковы, что необходимость в малом шаге постепенно отпадает. Реальный пример - СА FSW, обработка в широкой полосе сделана на достаточно высоком уровне, чтобы не заметить разницы между режимами FFT и SWEEP. Хорошо, если получится N*100 до 10 ГГц, или в худшем случае в комбинации с N*200 или N*400.

Например, в КюеС их 4.Мне казалось 5, точнее 3 и 5, после делителя, номеров гармоник. Или речь о количестве умножений?

Т.е. из-за чего сыр-бор (это не наезд, а, наоборот, приглашение к дискуссии или мозговому штурму, может и четыре - это перебор - есть такое смутное подозрение)?Не имею ничего против комбинаций 2x, 3x, 4x, идеология понятна. Где-то удобно использовать, где-то нет. На нашем предприятии много лет консервативно решали вопрос получения одной частоты путем умножения кварца на 2x-3x каскадах, больно было на это смотреть - каждый раз изобретение велосипеда, но синтезатор применять избыточно.

Иронию понял)100:1 - это сложно, точно отобьет охоту к ДНЗ, чего не хочется.

P.S. Согласованием по выходу ДНЗ можно добиться расширения частотной границы. Импульс по выходу сужается в 2-3 раза с соответствующим ростом амплитуды. Зачем это делал, лучше не спрашивать, в свое удовольствие. И где применять, пока не знаю ) Вывод такой - 200x-300x особых проблем не составляет. Понятно, почему HP в качестве калибровки фазы до 50 ГГц использует 10 МГц с умножением на ДНЗ.

-

Без какой-либо регулировки или подбора элементов?

По итогам среднее значение тока, все. Схема простая, настраивать нечего. С интересом жду разработки трансформатора 100:1 )

-

Это серьезный подход.

Я бы сказал стечение обстоятельств. Схема была проверена в изделии, где для подстраховки были заложены все возможные регулировки.

Попадались статьи, в которых отмечалось, что SiGe биполярные транзисторы очень шустро выходят из насыщения.Ключевые режимы могут быть без насыщения, поэтому стараюсь осторожно называть нелинейными.

-

Только вот прямоугольник на входе – это уже сформированные нечетные гармоники, диод на выходе – это добавка других гармоник. К тому же регулировка тока накачки предполагает настройку и контроль (возвращаемся к щупу СА). Можно даже при желании ввести автоматическую регулировку накачки, но это уже перегибы.

Без конкретной схемы сложно судить, но и сразу давать готовое решение - тоже не дело. Согласен, схема по возможности не должна содержать регулировок, и они отсутствуют в действительности. Проверено на небольшой выборке, около сотни, не много, но все из разных партий, дат изготовления, фирм производителей. Напишу краткие пояснения:

1. Прямоугольный сигнал на входе - это может быть простое усиление-ограничение, чтобы сделать схему не зависимой от входной частоты и разброса времени жизни заряда в диоде.

2. Регулировка тока накачки - это отдельный источник тока, подключаемый к диоду в период накачки (формально может быть резистор). По факту не встречал ситуации, когда требовалась регулировка.

3. Диод по выходу включается последовательно и работает как ключ - пропускает импульс в одном направлении. Новых гармоник ни прибавляется и не отнимается (по материалам сверхширокополосной локации).

В конечном итоге схема может быть соразмерна с двумя удвоителями Minicircuits (отсутсвуют частотозависимые элементы: индуктивности, конденсаторы, трансформаторы), не требовать настройки, и иметь гарантированный уровень гармоник. До 20x-30x стабильно и предсказуемо.

Укрощение строптивого ДНЗ

в RF & Microwave Design

Опубликовано · Пожаловаться

Коаксиал играет роль широкополосного отражающего элемента, чем больше разница с выходным сопротивлением, тем лучше. Полосу можно расширить, если диод нагружать не сразу на 50 Ом, а трансформировать с высокого сопротивления. Никто и нигде об этом не пишет, даже HP.