rloc

Модератор-

Постов

3 270 -

Зарегистрирован

-

Победитель дней

14

Весь контент rloc

-

Методом научного тыка

-

DCM - это и есть PLL, только другими словами, как-то копался в американских патентах и нашел описание этой DCM, там и про частоты было сказано и особенности работы. Джиттер очень сильно зависит от загруженности ПЛИС, посмотрите хотя бы на то, какими путями идет сигнал на вход CLKFB, замыкающий петлю ФАПЧ, не трудно представить как изменится джиттер если на этот сигнал чего-нибудь наведется. Еще кстати на джиттер влияет задержка в петле ФАПЧ - "Feedback Tap Delays", если хотите джиттер поменьше ставьте "Source-Synchronous" вместо "System-Synchronous". Используйте аттрибут RLOC_ORIGIN, можно в самом .vhdl/.v, можно в .ucf. Читайте "Constraints Guide" cgd.pdf и "Virtex-4 User Guide" ug070.pdf

-

Я склонен считать, что это плохая ЭМС внутри кристалла. Этот эффект я долго изучал в свое время на платах с Virtex-4 SX35, по питанию весь кристалл был усеян конденсаторами 0402 по 10нФ, проверял осциллографом - пульсации не превышали 10mV. Сами по себе VCO, входящие в состав DCM обладают очень большими шумами (очень большой джиттер). Чтобы выйти из этой ситуации вручную выбирал какая именно DCM будет отвечать за тот или иной клок.

-

Шум квантования идеального АЦП

rloc ответил kamil_yaminov тема в Математика и Физика

По ссылочкам описываются понятия среднеквадратического отклонения, которое равно квадратному корню из дисперсии и дан пример расчета дисперсии равномерно распределенной величины в диапазоне от 0 до 1 -

Шум квантования идеального АЦП

rloc ответил kamil_yaminov тема в Математика и Физика

http://ru.wikipedia.org/wiki/%D0%90%D0%A6%D0%9F -

Analog Power Supply для АЦП

rloc ответил Segment тема в Вопросы аналоговой техники

Прошу прощения за небольшой оффтопик, 4 платы по 5 шт. LT1763 в корпусах DFN на каждой, 0.33мкФ на входе, 10мкФ керамика по выходу и 10нФ X7R на Cbyp - никакой генерации, на осциллографе шумов не видно даже при чувствительности 2мВ/кл. Платы 4-х слойные, LDO прострочены под корпусом и рядом большим количеством виа. Токи от 50 до 200 мА, в том числе есть RF усилители, правда другой фирмы - WJ. Вообщем отличные LDO, рекомендую. На AD7718/AD7708 есть "Evaluation board", и в "Technical Note" приведена схема печати, где прекрасно видно разделение земель, ну а что касается Avdd и Dvdd - достаточно соединить их вместе в одной точке рядом с выходом LDO. По Avdd можно дополнительно поставить или проходной конденсатор типа Murata NFM21P или ферритовую бусинку BLM21P той же фирмы. В дополнение к "Evaluation board", порекомендовал бы не экономить на печати и делать ее 4-х слойной. -

Таких трансформаторов скорей всего не найдете, максимально широкополосными всегда были типа "balun" - до 3.5 ГГц, но они гальваники не обеспечивают.

-

Цитирую статью из журнала "Test & Measurement World" Rohde & Schwarz enters the time domain На новую беху не хватит :rolleyes:

-

чем почистить Clock 100MHz ?

rloc ответил тау тема в RF & Microwave Design

Не подумав задал вопрос, дело было к вечеру. Возникли ассоциации с синтезатором частоты и внутренним воздействием на кольцо PLL (изменение коэффициента деления), ну и соответственно время перестройки (установления фазы) от десятков мкс до единиц мс. Тогда другой вопрос: важна ли синхронность передачи, можно ли исключить тактовый сигнал и ввести блочное кодирование с коррекцией ошибок и разными опорами с двух сторон? -

Ишь какой шустрый, хоть бы предложили из серии RTM, у автора топика не такой тугой кошелек. И даже с RTM не влезем в диапазон 3000-5000 уе. Знающие люди утверждают, что ничего в них от Rohde&Schwarz нет.

-

Вышел ISE 12.2

rloc ответил faa тема в Среды разработки - обсуждаем САПРы

-

чем почистить Clock 100MHz ?

rloc ответил тау тема в RF & Microwave Design

Какой период помехи? Успеет ли PLL после переходных процессов восстановить нужную фазу сигнала? -

В тестбенче ничего интересного нет: constant clk_period : time := 10 ns; BEGIN -- Instantiate the Unit Under Test (UUT) uut: gluk PORT MAP ( clk => clk, cnt => cnt ); -- Clock process definitions clk_process :process begin clk <= '1'; wait for clk_period/2; clk <= '0'; wait for clk_period/2; end process; Давайте лучше сравним скрипты с которыми запускается ModelSim, я пользуюсь ISE: vlib work # # Compile sources # vcom -explicit -93 "../src/gluk.vhd" vcom -explicit -93 "../tb/gluk_tb.vhd" # # Call vsim to invoke simulator # vsim -voptargs="+acc" -t 1ps -lib work work.gluk_tb # # Source the wave do file # do {gluk_tb_wave.fdo} # # Set the window types # view wave view structure view signals # # Source the user do file # do {gluk_tb.udo} # # Run simulation for this time # run 1000ns # # End #

-

В руках не держал эти осциллографы, но по характеристикам цифровые ничем не отличаются от младших моделей именитых брендов (2500 waveforms/s, разрешение экрана 320x240). Более старшие модели Hameg, которые делаются для Rohde&Schwarz, впечатляют по характеристикам, как впрочем и по цене. Аналоговые модели очень хороши, если по цене устраивают, то всяко лучше немецкая сборка, чем китайская.

-

Будем считать наши позиции совпадают.

-

Вышел ISE 12.2

rloc ответил faa тема в Среды разработки - обсуждаем САПРы

Основные отличия - новая шина AXI4, под которую переработано большое количество IP ядер в корегенераторе и все они совместимы только с Virtex-6 и Spartan-6. В дальнейшем это направление будет развиваться и под новые проекты желательно использовать уже новую шину. -

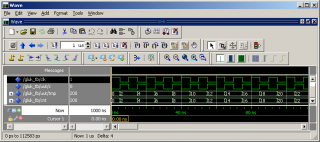

Автор этого топика спрашивал про сигнал prt_data_next, в котором наблюдались непонятные "скачки". Я так понимаю Вы попытались объяснить это следующим образом: Т.е. если я правильно понял, Вы говорили о неправильном отображении на экране. Я попробовал объяснить "скачки" особенностями работы алгоритма Моделсима и вполне корректным отображением на экране. Кто разберется с понятием "дельты", тот сможет не только объяснить, но и сделать скриншот в Моделсиме, поясняющий глюк функциональной симуляции моего примера.

-

Все очень просто, счетчик tmp (cnt) инкрементирует не "+1", а "+2" по каждому фронту сигнала с. Даже если я раззумлю график до масштаба 1пс, никаких гонок сигналов вы не увидите не по clk, не по c

-

Думаю начинающие простят мое незнание стандартов по моделированию. Для закрепления усвоенного материала, привожу простенький кусочек тестового кода для функциональной симуляции и результаты моделирования в Моделсиме (каждый может проверить). Это к вопросу CaPpuCcino об особенностях алгоритма рисовалки. library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity gluk is port( clk : in std_logic; cnt : out std_logic_vector(7 downto 0)); end gluk; architecture behavioral of gluk is signal a, b, c: std_logic; signal tmp: std_logic_vector(7 downto 0) := X"00"; begin a <= clk; b <= a xor clk; c <= not (b or clk); process (c) begin if c'event and c = '1' then tmp <= tmp + X"01"; end if; end process; cnt <= tmp; end architecture;

-

В данном случае - это абстракция, введенная разработчиками моделсима и ее вполне можно рассмотреть :rolleyes: Ладно, поправлюсь, в данном случае N*deltas<Resolution Time при сколько угодно большом N

-

чем почистить Clock 100MHz ?

rloc ответил тау тема в RF & Microwave Design

Можно просто ПАВ-фильтром обойтись -

Чтобы было понятно, откуда появляются пички, открывайте "modelsim_user.pdf" и читайте внимательно раздел "Expanded Time in the Wave and List Windows". Для простоты понимания, можно рассмотреть 2 примера: 1) if clk'event and clk='1' then a <= b; c <= a; end if; Если бы все задержки были равны нулю, то мы бы получили, что в один момент времени a = b и c = b. Поэтому моделсим вводит небольшую дельту (не путать с Resolution Time) и c = b только на следующем фронте clk. 2) a <= b; c <= a xor b; Здесь также моделсим добавляет небольшую дельту между сигналами a и b, в результате при поведенческом моделировании при смене состояния b из '0' в '1' или наоборот на выходе c мы увидим пички с длительностью в одну дельту. Чтобы внимательно рассмотреть эти дельты открывайте меню Wave->Expanded Time->Expand All

-

Присоединяюсь к мнению о неудачном выборе. Делал малошумящий LDO на LT1677 для синтезатора, так и не смог побороть шумы и самовозбуждение. С этой микросхемой действительно приятнее работать.

-

С хорошим аналоговым отображением сигнала делает цифровые осциллографы фирма Yokogawa из серии DLM2000, которые получили высокую оценку по мнению журнала "Test & Measurement World". Где-то в описании нашел, что они используют быстродействующий ASIC собственной разработки. По ценам точно не знаю, в интернете встречается цена 4250$ за двухканальную модель с полосой 200MHz, надо звонить дистрибьюторам.

-

Попробую несколько иначе, по-простому, объяснить разницу. Если хотите, чтобы цифровой осциллограф по качеству отображения картинки был близок к аналоговому, смотрите чтобы скорость обновления информации была выше чем 100.000 осциллограмм/сек (waveforms/s). Иначе разницы между вашими теками можете и не увидеть. Но тут боюсь ценник будет стартовать с 5.000$, даже китайский Rigol 6000-ой серии начинается с более чем 7.000$