-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

проект Planahead и XPS добавить в SVN

Krys опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Хочу добавить проект Planahead (внутри ещё и проект XPS) в SVN. Но не хочу добавлять все файлы подряд в папке проекта, чтобы не было мусора. Кто может посоветовать, как кто у себя делает. Когда работал в ISE (правда без XPS) - там просто: добавлял только файл проекта, результирующий бинарник и *.ucf. И никаких подпапок даже не требовалось добавлять. Всё остальное можно получить, нажав имплемент (бинарник конечно тоже можно получить, но долго, а бывает хочется сразу). Есть какие-то аналогичные советы для Planahead? Полная структура папок сейчас такая: └───fft_sp605 ├───fft_sp605.cache │ └───compile_simlib ├───fft_sp605.data │ ├───cache │ ├───constrs_1 │ ├───runs │ │ ├───impl_1 │ │ └───synth_1 │ ├───sim_1 │ ├───sources_1 │ └───wt ├───fft_sp605.runs │ ├───.jobs │ ├───impl_1 │ │ ├───.constrs │ │ ├───xlnx_auto_0_xdb │ │ ├───_ngo │ │ └───_xmsgs │ └───synth_1 │ ├───xst │ │ ├───dump.xst │ │ │ └───module_1_stub.prj │ │ └───work │ └───_xmsgs ├───fft_sp605.sdk │ └───SDK │ └───SDK_Export │ ├───.metadata │ │ └───.plugins │ │ ├───org.eclipse.cdt.core │ │ ├───org.eclipse.cdt.make.core │ │ ├───org.eclipse.core.resources │ │ │ ├───.projects │ │ │ │ └───module_1_hw_platform │ │ │ │ └───.indexes │ │ │ ├───.root │ │ │ │ └───.indexes │ │ │ └───.safetable │ │ ├───org.eclipse.core.runtime │ │ │ └───.settings │ │ ├───org.eclipse.debug.core │ │ ├───org.eclipse.debug.ui │ │ ├───org.eclipse.tcf │ │ │ └───certificates │ │ ├───org.eclipse.tcf.debug │ │ ├───org.eclipse.ui.editors │ │ ├───org.eclipse.ui.intro │ │ └───org.eclipse.ui.workbench │ ├───hw │ │ ├───docs │ │ │ ├───drivers │ │ │ └───ip │ │ └───imgs │ └───module_1_hw_platform └───fft_sp605.srcs └───sources_1 ├───edk │ └───module_1 │ ├───blockdiagram │ ├───data │ ├───etc │ ├───hdl │ │ └───elaborate │ │ ├───clock_generator_0_v4_03_a │ │ │ └───hdl │ │ │ └───vhdl │ │ └───microblaze_0_bram_block_elaborate_v1_00_a │ │ └───hdl │ │ └───verilog │ ├───implementation │ │ ├───axi4lite_0_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi4_0_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_coef_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_in_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_out_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_w_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_x1_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_x2_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_datamover_y_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_coef_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_in_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_out_wind_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_w_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_x1_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_x2_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_dma_ctrl_y_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───axi_stream_data_width_converter_0_wrapper │ │ ├───axi_stream_fft_core_0_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───cache │ │ ├───clock_generator_0_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───debug_module_wrapper │ │ ├───dip_switches_4bits_wrapper │ │ ├───leds_4bits_wrapper │ │ ├───mcb_ddr3_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───microblaze_0_bram_block_wrapper │ │ ├───microblaze_0_dlmb_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───microblaze_0_d_bram_ctrl_wrapper │ │ ├───microblaze_0_ilmb_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───microblaze_0_i_bram_ctrl_wrapper │ │ ├───microblaze_0_wrapper │ │ │ ├───xlnx_auto_0_xdb │ │ │ └───_xmsgs │ │ ├───proc_sys_reset_0_wrapper │ │ ├───push_buttons_4bits_wrapper │ │ ├───rs232_uart_1_wrapper │ │ └───sysace_compactflash_wrapper │ ├───pcores │ ├───synthesis │ │ ├───xst_temp_dir │ │ └───_xmsgs │ └───__xps │ ├───.dswkshop │ ├───ise │ │ └───_xmsgs │ ├───MCB_DDR3 │ └───pa │ ├───log │ └───stub └───imports └───microblaze Вопрос какие папки можно убить безболезненно, а второй вопрос - какие файлы в оставшихся папках тоже можно убить ))) -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

А у Вас не найдётся примерчик использования такой конструкции? А чем удобнее? Почему в Верилоге не все могут на него ссылаться? -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Такой вопрос появился: когда работал с Verilog под Xilinx, то в тестбенче использовали сигнал glbl.GSR, чтобы типа свой ресет не колхозить, а использовать "кошерный ресет", от производителя так сказать. Как делают ресет в тестбенчах на VHDL под Xilinx? -

vhdl obfuscator

Krys ответил dmitry-tomsk тема в Среды разработки - обсуждаем САПРы

netgen -sim -ofmt [verilog|vhdl] [options] input_file [.ncd] Типа такого можно попробовать. Пишут конечно, что это для симуляции, а не для синтеза, но вполне возможно, что для синтеза тоже будет работать, это можно попробовать для каждого конкретного исходника в железе. Вроде как vhdl-код и есть, но чёрт ногу сломит в примитивах... ))) ЗЫ: а чего это такую старую тему то подняли? )) -

Ну это я так понимаю относится к тому же, что и: Ещё можно то же самое сделать через Design - Settings - General - Top-level, и там мышкой с зажатым Ctrl выбрать сразу несколько топовых модулей. Минус данного решения в том, что по команде Delete Simulation Data эта настройка так же удаляется... Хотя настройка одинарного топового модуля не забывается. Бага наверное...

-

Aldec 9.3 тормоза

Krys ответил svalery тема в Среды разработки - обсуждаем САПРы

Отключил на всякий случай. Но SLP мне не светит, т.к. я забыл в начале сказать, что использую Standart Waveform Viewer, а для него нельзя использовать ключ Verilog Optimization. Ну а при таких настройках у меня всё равно ничего не ускорилось... Спасибо за разъяснения и подсказки. Поскольку я в VHDL новичок, мне это всё пригодится. А где-то здесь уже обсуждалось, когда лучше применять Variable вместо signal? Заодно: пробовал добавлять "...верилог сорцы именно FIFO_GENERATOR_Vxxxx и без всяких либ...", время не изменилось... ----------- И хочу поделиться результатами своих мучений. 1. Язык корки и библиотеки, а также тип корки (Structural, Behavioral) не влияет на время выполнения Initialize Simulation, это всё порядка 10 минут. 2. Это же не влияет и на скорость симуляции, специально всё замерял по секундам. 3. Проблема с большим временем выполнения Initialize Simulation имеет место лишь для Standart Waveform Viewer, в Accelerated Waveform Viewer всё быстро. 4. Случайно обнаружено, что на время выполнения Initialize Simulation влияет порядок действий. Изначально время выполнения Initialize Simulation порядка 10 минут было для случая, когда файл вэвформ уже открыт. Если файл не открыт, то это время буквально секунда. Но затем вы должны открыть этот файл, и тут открытие начинает занимать большое время, тогда как без Initialize Simulation файл открывается быстро. Но это большое время в разы меньше, чем когда Initialize Simulation делается при уже открытом файле вэйвформ. Так, для примера, для моего проекта это время 3,5 минуты для файла с большой длительностью симуляции. 5. Опытным путём установлено, что на время выполнения Initialize Simulation без открытия файла вэйвформ влияет его размер. Так что если большие длительности симуляции не нужны, можно на этом сыграть. Я урезал свой файл с 10мс до 1мс (правда там не все вэйвформы были заполнены до конца), объём уменьшился раза в 3, время выполнения Initialize Simulation сократилось до 1,5 минут. Так что я наверное уже заканчиваю искать выход, т.к. решение по пп. 4 и 5 для меня дают удовлетворительное время ожидания. -

интересно, почему они по умолчанию не включены? )) Как специально Xilinx хочет, чтобы на его продукт ругались, что он тормозной )))

-

Aldec 9.3 тормоза

Krys ответил svalery тема в Среды разработки - обсуждаем САПРы

Я перегенерил корки с настройками проекта, как указал ув. sallador. Т.е. получается, что у меня верилоговские только корки. Но, как я могу предположить, вполне логично компилятору догадаться при компиляции верилоговских корок подхватить верилоговские либы. Хотя... Дело в том, что фифо_генератор инстантируется в корках при указании behavioral модели. А когда модель structural, там остаются чистые плисочные примитивы типа LUT2, FD и т.п. Но я попробую опять взять корки с behavioral моделью и скомпилить верилоговский фифо-генератор. -

Aldec 9.3 тормоза

Krys ответил svalery тема в Среды разработки - обсуждаем САПРы

Спасибо за подсказки. Верилоговские коры с behavioral моделью не ускорили инициализацию симуляции (как и саму симуляцию). А симуляция корок с structural моделью у меня не запускается, вот отдельную тему создал: проблема с модулем glbl.v и коргеновским фифо от Xilinx в Active-HDL, ошибка, что не находит модуль glbl, на который ссылается примитив Итак, попробовал верилоговские корки с structural моделью, ничего не ускорилось. Так что проблема остаётся иметь место... -

Спасибо, чото сразу не догадался, что модуль объявлен то объявлен, но нигде не инстантируется ни разу... Помогло. Там задержка 100 нс, думаю это ни о чём...

-

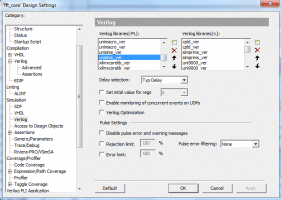

Здравствуйте. Мне нужно в Active-HDL использовать Verilog-корки коргеновские (и соответствующие Verilog-либы) от Xilinx, симулируя VHDL-исходники, в которых эти корки инстантированы. Я попробовал перегенерить корки с указанием Behavioral как Preferred Simulation Model. Симуляция прошла нормально. Но мне посоветовали, что правильно нужно сделать симуляцию для Structural, а не Behavioral. Я перегенерил корки, подсунул в Active-HDL, скомпилил. Вылезли ошибки по команде Initialize simulation, вот лог: asim -advdataflow -L simprims_ver -L uni9000_ver -L unimacro_ver -L unisims_ver -L xilinxcorelib_ver -L cpld_ver -L cpld_ver -L cpld_ver -L simprims_ver -L simprims_ver -L uni9000_ver -L uni9000_ver -L unimacro_ver -L unimacro_ver -L unisims_ver -L unisims_ver -L xilinxcorelib_ver -L xilinxcorelib_ver -PL simprims_ver -PL unimacro_ver -PL unisims_ver -PL xilinxcorelib_ver -PL uni9000_ver -PL cpld_ver -PL cpld_ver -PL cpld_ver -PL simprims_ver -PL simprims_ver -PL uni9000_ver -PL uni9000_ver -PL unimacro_ver -PL unimacro_ver -PL unisims_ver -PL unisims_ver -PL xilinxcorelib_ver -PL xilinxcorelib_ver +access +w_nets +p+/tb_delay axi_stream_fft_core behav_arch # ELBREAD: Elaboration process. # ELBREAD: Elaboration time 0.2 [s]. # asim: Stack memory: 256MB # asim: Retval memory: 256MB # KERNEL: Main thread initiated. # KERNEL: Kernel process initialization phase. # KERNEL: Time resolution set to 1ps. # ELAB2: Elaboration final pass... # KERNEL: PLI/VHPI kernel's engine initialization done. # PLI: Loading library 'C:\Program Files (x86)\Active-HDL 9.3\bin\systf.dll' # ELAB2: Create instances ... # ELAB2: Fatal Error: ELAB2_0036 Unresolved hierarchical reference to "glbl.GSR" from module "axi_stream_fft_core.x1_fifo.\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i \" (module not found). # ELAB2: Last instance before error: /axi_stream_fft_core/x1_fifo/\U0/xst_fifo_generator/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i \ # KERNEL: Error: E8005 : Kernel process initialization failed. # Error: Fatal error occurred during simulation initialization. Вот содержимое моего проекта: Вот либы указанные в настройках симуляции проекта: Тут видно не всё, но видно, что есть необходимые либы, где есть glbl.v, на которые оно ругается. Вот исходник коргеновского фифо, на которое ругается ошибка: fft_core_fifo_33_66.v Тут в строчке 318 как раз инстантируется примитив, указанный в ошибке. Открываю этот примитив по адресу C:\Program Files (x86)\Active-HDL 9.3\vlib\xilinx_ise\verilog\unisims_ver\src\FD.v, вот его исходник: // $Header: /devl/xcs/repo/env/Databases/CAEInterfaces/verunilibs/data/unisims/FD.v,v 1.13 2006/02/13 22:07:02 yanx Exp $ /////////////////////////////////////////////////////////////////////////////// // Copyright © 1995/2004 Xilinx, Inc. // All Right Reserved. /////////////////////////////////////////////////////////////////////////////// // ____ ____ // / /\/ / // /___/ \ / Vendor : Xilinx // \ \ \/ Version : 10.1 // \ \ Description : Xilinx Functional Simulation Library Component // / / D Flip-Flop // /___/ /\ Filename : FD.v // \ \ / \ Timestamp : Thu Mar 25 16:42:16 PST 2004 // \___\/\___\ // // Revision: // 03/23/04 - Initial version. // 02/04/05 - Rev 0.0.1 Remove input/output bufs; Seperate GSR from clock block. // 08/09/05 - Add GSR to main block (CR 215196). // 10/20/05 - Add set & reset check to main block. (CR219794) // 2/07/06 - Remove set & reset from main block and add specify block (CR225119) // 2/10/06 - Change Q from reg to net. (CR ) // End Revision `timescale 1 ps / 1 ps module FD (Q, C, D); parameter INIT = 1'b0; output Q; input C, D; wire Q; reg q_out; tri0 GSR = glbl.GSR; initial q_out = INIT; always @(GSR) if (GSR) assign q_out = INIT; else deassign q_out; always @(posedge C) q_out <= D; assign Q = q_out; specify (posedge C => (Q +: D)) = (100, 100); endspecify endmodule Тут в 38 строчке как раз идёт ссылка на модуль glbl, который коргеновском исходнике фифошки уже объявлен. Но ошибка имеет место. Поэтому я решил явно добавить glbl.v в проект, что и видно в дереве. Модуль у меня по такому пути: c:\Program Files (x86)\Active-HDL 9.3\vlib\xilinx_ise\verilog\unisims_ver\src\glbl.v Поскольку модуля glbl теперь стало 2, то при компиляции возникла ошибка, что один из модулей уже объявлен, поэтому пришлось доработать добавленный модуль в начале строчками условной компиляции по аналогии с тем, как это сделано в одноимённом модуле в исходнике корки фифо. Вот его доработанный исходник: // $Header: /devl/xcs/repo/env/Databases/CAEInterfaces/verunilibs/data/glbl.v,v 1.15 2011/08/25 22:54:30 fphillip Exp $ `ifndef GLBL `define GLBL `timescale 1 ps / 1 ps module glbl (); parameter ROC_WIDTH = 100000; parameter TOC_WIDTH = 0; //-------- STARTUP Globals -------------- wire GSR; wire GTS; wire GWE; wire PRLD; tri1 p_up_tmp; tri (weak1, strong0) PLL_LOCKG = p_up_tmp; wire PROGB_GLBL; wire CCLKO_GLBL; reg GSR_int; reg GTS_int; reg PRLD_int; //-------- JTAG Globals -------------- wire JTAG_TDO_GLBL; wire JTAG_TCK_GLBL; wire JTAG_TDI_GLBL; wire JTAG_TMS_GLBL; wire JTAG_TRST_GLBL; reg JTAG_CAPTURE_GLBL; reg JTAG_RESET_GLBL; reg JTAG_SHIFT_GLBL; reg JTAG_UPDATE_GLBL; reg JTAG_RUNTEST_GLBL; reg JTAG_SEL1_GLBL = 0; reg JTAG_SEL2_GLBL = 0 ; reg JTAG_SEL3_GLBL = 0; reg JTAG_SEL4_GLBL = 0; reg JTAG_USER_TDO1_GLBL = 1'bz; reg JTAG_USER_TDO2_GLBL = 1'bz; reg JTAG_USER_TDO3_GLBL = 1'bz; reg JTAG_USER_TDO4_GLBL = 1'bz; assign (weak1, weak0) GSR = GSR_int; assign (weak1, weak0) GTS = GTS_int; assign (weak1, weak0) PRLD = PRLD_int; initial begin GSR_int = 1'b1; PRLD_int = 1'b1; #(ROC_WIDTH) GSR_int = 1'b0; PRLD_int = 1'b0; end initial begin GTS_int = 1'b1; #(TOC_WIDTH) GTS_int = 1'b0; end endmodule `endif Но это ничего не помогло. Ошибка та же. Помогите, пожалуйста, избавиться от ошибки и запустить симуляцию.

-

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

О! Оказывается уже была такая проблема у людей... ) Только раньше это вызывало ошибку, а сейчас ворнинг. Ну и ладно. Забьём ) VHDL, Агрегат -

Aldec 9.3 тормоза

Krys ответил svalery тема в Среды разработки - обсуждаем САПРы

Спасибо. Первое действие в отдельности не помогло. А как сделать второе действие? Я пишу на VHDL. В обёртке фифошной корки есть такое упоминание: LIBRARY XilinxCoreLib; На компе есть такая папка c:\Program Files (x86)\Active-HDL 9.3\vlib\xilinx_ise\vhdl\xilinxcorelib\ Папки Verilog там нет. Если найти (скачать, сгенерить) под Verilog, положить в это место, а папку vhdl\xilinxcorelib\ убить, так скушает? Или там какие-то есть особые действия? Допустим, у меня есть верилоговские либы. Как Альдеку указать, что, хоть я и использую язык VHDL, но либы он должен брать верилоговские? -

это ничего не даст, хоть и знать будешь. Насколько я понял, фазы разводки - это последовательные итерационные проходы, на каждом следующем должно уменьшаться количество неразведённых цепей (почитайте отчёт). Чем больше фаз - тем труднее было развести ваш проект, с первой фазы не вышло. Попробуйте для эксперимента самый простенький проект на одном триггере, гляньте, сколько там фаз получилось. По опыту, на время разводки (как собственно и написано по ссылке) влияет сложность выполнения ваших ограничений. Если выполнить несложно - разведёт быстро. Если кристалл под завязку, а частоты надо обеспечить высокие - разводить будет долго. Ну там конечно есть свои нюансы в конкретном проекте...

-

Aldec 9.3 тормоза

Krys ответил svalery тема в Среды разработки - обсуждаем САПРы

У меня возникла проблема с тормозами Active-HDL на стадии Intitialize simulation. Вот если что логи консоли: asim -advdataflow -O5 +access +w_nets +p+/tb_delay axi_stream_fft_core behav_arch # Warning: Verilog Optimization cannot be used when -advdataflow is in effect. Verilog Optimization disabled. # ELBREAD: Elaboration process. # ELBREAD: Elaboration time 0.1 [s]. # asim: Stack memory: 32MB # asim: Retval memory: 32MB # KERNEL: Main thread initiated. # KERNEL: Kernel process initialization phase. # KERNEL: Time resolution set to 1ps. # ELAB2: Elaboration final pass... # ELAB2: Create instances ... # ELAB2: Create instances complete. # ELAB2: Elaboration final pass complete - time: 0.3 [s]. # KERNEL: Kernel process initialization done. # Allocation: Simulator allocated 13855 kB (elbread=5213 elab2=8197 kernel=444 sdf=0) # 10:29, 6 íîÿáðÿ 2014 ã. # Simulation has been initialized # Selected Top-Level: axi_stream_fft_core (behav_arch) Очень долго висит на стадии # ELAB2: Create instances .., порядка 10 минут. Проект в целом не сложный, вычислитель ЦОС в виде бабочки БПФ, но на входах и выходах вычислителя ЦОС имеются 4 коргеновские фифошки по размерам примерно 2..4 рамблока (т.е. глубина примерно 1000 - в зависимости от ширины шины). Симулировал сам вычислитель отдельно - тормозов не было, а когда добавил фифошки - появились. Кто знает, что-то можно подкрутить, чтобы уменьшить время инициализации? Я уж не говорю про время симуляции, на первых порах мне достаточно первых микросекунд. Но как что-то изменишь - ждать приходится по 10 минут инициализацию... работа пробуксовывает... -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Выяснились первые недостатки такого подхода - разделять умеет только вектора std_logic_vector, одиночные проводники типа std_logic не разделит. Либо нужно писать дополнительные процедуры, учитывая, что на каждом месте может быть одиночный проводник, а может и не быть. Даже для 4 аргументов придётся 16 разных функций описывать, это уж слишком... Пока обхожу этот "гвоздь в крышку гроба VHDL" описанием одиночных сигналов как std_logic_vector(0 downto 0), но это неудобно, т.к. при подстановке приходится всегда индекс (0) подписывать. -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

спасибо. Все подводные камни уже оказывается прощупаны ) -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Виноват, сразу не показал весь код, там ещё генерэйт есть: norndg: if NRS_BITS = 0 generate rnd_const <= (others => '0'); end generate norndg; rndg: if not (NRS_BITS = 0) generate rnd_const <= (NRS_BITS-1 => '1', others => '0'); end generate rndg; Так что нулевые отсеиваются. Ругается на ненулевые похоже. Попробовал ещё раз вместо NRS_BITS подставить константу NRS_BITS_С, определённую как constant NRS_BITS_C : natural := 4; Варнинг исчез. Но когда определяю так: constant NRS_BITS_C : natural := NRS_BITS; . То варнинг остаётся. Получается ругается на generic параметры?... -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

бывает 0 в некоторых инстансах, бывает 33 rnd_const объявлена так: signal rnd_const : std_logic_vector(BW_DSP_OUT-1 downto 0); , где constant BW_DSP_OUT : natural := 48; -

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Знатоки, подскажите, пожалуйста. Есть строчка: rnd_const <= (NRS_BITS-1 => '1', others => '0'); где entity mult35x35 is generic ( NRS_BITS : natural := 0; Active-HDL выдаёт такое ругательство: # Warning: COMP96_0349: ../../../../../rtl/std_lib/mult35x35.vhd : (194, 23): Aggregate with multiple choices has a non-static or null choice. Пробовал вместо NRS_BITS подставлять константу - та же ошибка. Пробовал вместо NRS_BITS подставлять просто число - ошибки нет. Как правильно написать, чтобы не было ворнинга. Что я делаю не так? -

vitus_strom, спасибо, полезная инфа.

-

Я сначала не знал, что параллельную флешь можно через жтаг стандартными средствами прошить. Оказалось это просто хитро называется BPI Flash, а я её искал как parallel flash. Теперь нашёл. Значит проблема отпадает. Да, в соседней ветке я уже отписался, что разобрался, как работать с карточкой. Так что теперь проблем нет, буду работать с карточкой лучше. Будьте добры пожалуйста поподробнее, что значит "загрузить в область данных флеши"? В чью область данных? Микроблэйза? Короче непонятно... Предупреждаю, что новичок в этом, так что вопросы могут быть тривиальными ))

-

А Вы попробуйте, потом тут отпишитесь

-

Нарыл тут http://www.xilinx.com/support/documentatio..._3/oslib_rm.pdf (стр. 156), что мне нужна библиотека LibXil FFS. Как такое подключается? Попробовал прописать в исходник хедеры, указанные в табличке, - не видит таких. Вот даже примерчик нарыл по использованию int main() { xil_printf("\n\r Hello \n\r"); const char *file="test.txt"; const char*mode="w"; SYSACE_FILE *ps; ps=sysace_fopen (file, mode); if(ps==NULL) xil_printf(" FILE OPEN FAILED !!! \n\r"); else { xil_printf(" FILE OPEN SUCCESSFULL !!! \n\r"); sysace_fclose (ps); } return 0; } Но у меня эти функции не видятся, ошибку даёт, что не знает таких. Как сделать, чтобы он их увидел? Вот даже советуют Но как этот пример выколупать я так и не понял. Может кто знает решение. Поскольку я во встраиваемых процессорных системах новичок, то мои вопросы могут иметь элементарное решение )) Но я увы его не знаю. Всё, по крайней мере с последним вопросом разобрался. Чтобы это всё увиделось нужно: 1. В EDK в Project Explorer нажать правой кнопкой на [имя вашего проекта]_BSP, выбрать Board Support Package Settings и поставить галочки напротив xilfatfs и xilflash, а в исходнике прописать #include "sysace_stdio.h" Вот тут ещё крупица информации, где эти библиотеки находятся локально: http://www.xilinx.com/support/answers/45479.html Там я нашёл и доку на использование функций. Теперь думаю дело попрёт.

-

Спасибо. Можно попробовать. Правда я уже начал подумывать заюзать CompactFlash (вот тема соседняя), на неё записать файл с компа через кардридер. А в программе микроблэйза надо будет вычитать из файла. А в предложенном Вами варианте о каком подходящем ядре в XPS идёт речь? Я поставил предлагаемое стандартное ядро для этой отладочной платы для работы с параллельным флешем. Но флеш то параллельный, а жтаг последовательный, как это грузить из компа - так разве можно? Может тогда вместо параллельной флеши таким же макаром через жтаг грузить CompactFlash? Так получится?