-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

Сделать полноценный синтаксический анализатор конструкций языка высокого уровня - это задача серёзная и нетривиальная, вряд ли автор хочет убивать 90% времени на написание анализатора ради 10% времени на "поиграться" с результатом ))) Накладные расходы должны быть оправданы и соразмерны основной работе )))

-

Ну тогда справедливости ради надо упомянуть, что вообще началось это с Си (рекомендация обходиться без препроцессора). Но мы и будем минимизировать. Мы же не сплошь и рядом все условия через препроцессор описываем, а только самые нужные, без которых не обойтись. Например, включение или отключение объявления портов в интерфейсной части.

-

VHDL+ISE

Krys ответил NikSave тема в Языки проектирования на ПЛИС (FPGA)

Сумматор, если правильно описать (см. xst.pdf по предыдущему совету), ляжет в ДСП. Беглый взгляд на http://www.xilinx.com/support/documentatio...uides/ug369.pdf натолкнул на мысль, что аппаратные каскадные связи работают только в пределах столбца (стр. 12): Вчитываться дальше лень, но думаю надо копать в этом направлении. Где-то есть ограничение. Но думаю нет проблем между столбцами соединить не выделенными каскадными связями, а обычными трассировочными ресурсами общего назначения. Можно вообще не использовать каскадные связи, а сразу всё делать на обычных, тем более, что не всегда синтезатор и видит эти каскадные связи. -

Ставлю под сомнение, что без нижнего слоя нельзя. Возвратный ток может идти и рядом на том же слое, просто надо окружить дифпару полигоном. В том же Поляр есть такие варианты дифпар, если не ошибаюсь, single layer они там называются. Давно не юзал, проги щас нет, могу ошибаться. Все мои утверждения только для общего случая, пойдёт ли это для конкретно SATA - не знаю. Для русских людей должно быть известно понятие кряк ))) Я с местного фтп для Вас скачаю, потом выложу. А так - да, сопротивление без подложки будет другое, но оно в любом случае будет. Залил на файлообменник. Не уверен, можно ли сюда постить ссылки. Куда выслать ссылку? Почта форума пишет отключена или не работает.

-

Неверно. Волновое сопротивление есть у любой линии, даже без подложки. Простой калькулятор, которым я пользовался, например Polar Si 8000 если не ошибаюсь так называется.

-

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Дак это обычное "не надо на спичках экономить". Аналогично в российских компаниях зачастую экономят на мощности компа у разработчика: то памяти крохи, то монитора 2 не покупают и т.п. Хотя эти разовые траты по сравнению с его годовой зарплатой - сущие копейки. Предприятие готово платить немалые деньги в качестве зарплаты разработчику, но неготово оплатить ему нормальный инструмент по цене существенно ниже этих немалых денег на зарплату. Так вот и сидим при хорошей зарплате и на говёном железе и про себя подумываем: может мне самому уже купить на свою хорошую зп недостающее и на этом работать? ))) -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

А вот я утверждаю обратное. В последнем случае всё очевидно из одной строчки. Для первого случая необходимо ещё дополнительно напрячь мозги и поднять глаза выше, разобравшись ещё с одной строчкой. А теперь представим себе, что портмаппинг длинный, и в экран не влазит - нужно пролистывать и искать, откуда же растут ноги. А так всё в одном месте. Не надо лишних сущностей. Согласен с SM, что введение дополнительных переменных очень часто только запутывает. Конечно, бывает и наоборот. Но в данном случае без неё запросто можно обойтись, ничего не ухудшив, а лишь уменьшив запутывание "вероятного противника" ))) А вот с этим согласен. Поэтому я обычно не пишу портмаппинг в одну строчку - слишком сложно парсить глазами ))) Я бы записал у себя в коде так: Module4 Mod_inst ( .out({sig1, new_sig, new_newSig_3}) ); Такая структурированность особенно важна, когда порт не один, как в данном примере, а несколько. Как уже было сказано, запутывает не количество строк, а лишний мусор в виде например промежуточных переменных, служащих лишь для "workarround" недостатков языка либо как бесполезный лексический шаблон языка из кучи мусора. -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Поддерживаю. Чем компактнее - тем нагляднее. Точнее чем больше информации влезет в поле зрения без перелистывания, тем нагляднее видно, как это работает. Краткость - сестра таланта, да и принцип бритвы Оккама никто не отменял )) -

Какой язык учить?

Krys ответил Pavia тема в Языки проектирования на ПЛИС (FPGA)

Ёжики, плакали, кололись?... )))) А вся эта тема им и является. И для того и создана. Про клавиатуру: набираю 10-пальцевым, как и многие сейчас, но проблема не в этом, а в психологическом моменте навроде "а может ну её нафиг эту доработку?". Вы утверждаете, что, когда хорошо знаешь VHDL, то писанины получается сравнимо с Verilog? Боюсь, что я уже знаю VHDL на достаточном уровне, чтобы понять, что меньше уже не напишешь и от тонны бесполезного мусора не избавишься. Остаётся копипастить шаблоны. Вовсе не так. С недостатками навроде бегин-енд я согласился, и это не достоинства. Но достоинств больше. Вы думаете, я лично Вас хочу уесть или спорю просто ради спортивного интереса, чтобы "победил" обязательно я? Я просто высказал свои комментарии к высказываниям, с которыми я несогласен. Просто свою точку зрения. Всё встречалось. Давайте не будем мериться пиписьками ))) Только я до сих пор не понимаю, чем VHDL лучше при глубине иерархии >10? По-моему, вообще от глубины мало что зависит... Да и чем лучше когда 2000 портов? По реализации портмапа я считаю, что оба языка одинаковы по трудоёмкости. Выигрывает только SV с его интерфейсами. Здесь я тоже не вижу никакой взаимосвязи между выбором языка и направлением подхода к проектированием. Если инструмент мне даёт возможность написать быстро, то я ею могу пользоваться при любом направлении. -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Вот-вот, тем более, что верилог позволяет конкатенацию для выходного порта прямо в портмэпе, а вхдл только для входного. -

Холивара для ))

-

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Ну значит и здесь VHDL ничем не лучше Verilog'а -

Какой язык учить?

Krys ответил Pavia тема в Языки проектирования на ПЛИС (FPGA)

За такой тонкий и не сразу ощущаемый сарказм - Вам "плюс в репу" ))) Но по существу почти все Ваши аргументы вполне парируемы: Ну да, это мелкие неприятности. Но приноровиться можно крайне просто. Есть ещё и begin с end которые загромождают вид, это недостатки языка. Верилог неидеален. Просто достоинств больше. Зачастую HDL-кодер - это одно лицо, а ЦОС-ник - это другое. Бывает и вместе. Тогда и языков человек много знает. Почти нет таких узких специалистов, кто бы ничего побочного не знал. Совершенно не проблема. Строгая типизация тоже позволит избежать ошибок. А это кому-то надо? Из-за неё писанины больше, а опытный разработчик такие ошибки либо не совершает, либо быстро находит. Для начинающих - да, нужно как можно больше инструментов по автоматическому указанию на ошибки. В Си препроцессор есть, многим он удобен. Но не нравится - можете не пользоваться. Инструмент вам предложили, а дальше дело ваше. Средствами синтезатора можно. И средствами симулятора тоже. Я всегда ставил защиту от дурака. Точнее я делал вывод сообщения в консоль и остановку дальнейшего анализа. Сообщение можно было почитать среди ворнингов синтезатора кажется. В SV чтобы пробросить лишний сигнал достаточно добавить его к интерфейсу. Это уже конечно не чистый верилог. Но если уж в последствии мечтать о переходе на SV, то начать изучать можно хотя бы чистый верилог. Не придирайтесь так уж жёстко к такой мелочи, как не понравившийся Вам символ в названии функции. Ну так просто называется функция, имя у неё такое, с доллара начинается. Вы можете зато написать свою, без доллара, под тем же именем. Т.е. доллар даёт позволяет не занимать это имя как зарезервированные слова языка. Это наоборот удобство. А надо выше? Куда? Вошли и пишите. Чем проще и быстрее освоить инструмент и чем на нём быстрее пишется и получается конечный результат - тем лучше. Дело не в самих пальцах. Думаю, пальцы особо не страдают: просто надписи на клавишах Ctrl C и V стираются быстрее ))) Дело в другом: когда на VHDL что-то хочется добавить, то ты мысленно прокручиваешь, какую кучу шелухи придётся наворотить, чтобы добавить эту простенькую фишку, уместившуюся бы (условно!) на верилоге в одну строчку. И дальше у тебя встаёт психологический барьер: а может ну её? Или может как-то сделать попроще? Даже копипастить длинные портянки - есть психологический барьер: ведь эту портянку ещё нужно найти где-то в своих старых исходниках, нужно ещё лазить по файлам, выискивать этот шаблон... Вспоминать, где это могло встречаться... А на верилоге писать можно с ходу, не лазия за шаблонами. Т.к. пишется всё очень просто. -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Полностью поддерживаю! Любители "error proof" пишут сразу на VHDL, им не жалко пальцы ) Назовите как хотите. Я сказал лишь, как бы я хотел это видеть. Есть в верилоге такое решение? Похоже уже дали ответ, что нельзя навроде open написать... А так? (стрелочки в другую сторону) port1_out(2) => port1_out(0), port1_out(1) => open, port1_out(0) => port1_out(1) -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

В другую, это же выход из более нижестоящего модуля в верхний. Ну я так в исходном сообщении и предложил, сказав, что это некрасиво. А красиво это как в VHDL типа open написать. Но как сказали, и в вхдл так нельзя. Это тоже модификация того, что я предлагал в начале. Прямые и очевидные способы я и так знаю ) -

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Сделаем из этой темы аналог Странные вопросы по VHDL, только для верилога. Вопрос: как в Verilog сделать: имеем модуль, у которого есть порт на выход (пусть условно будет 3 бита). Модуль инстантируется в более верхнем модуле. Нужно один из битов порта никуда не подключать. Примерно так: .port1_out({port1_out[0], ничего, port1_out[1]}). Как это сделать максимально красиво? Можно объявить однобитный wire, никуда его не подключать, прописать вместо "ничего". Можно даже не объявлять, он итак будет однобитным. А красиво как? В VHDL например можно сделать так: port1_out(2) <= port1_out(0), port1_out(1) <= open, port1_out(0) <= port1_out(1) А как в верилоге сделать аналог опен? -

А вот в VHDL нет такого препороцессора... фтопку его ))) К стати, через generate невозможно порты то использовать, то нет. А через препроцессор - можно. Ну а ещё лучше для изврата с составом портов наверное использовать SV, интерфейсы

-

Во всё вникать и проверять доказательства самому - не хватит времени на всё, это надо было делать ещё в вузе ))) Сейчас проще прислушаться к опыту "старших товарищей".

-

Хотелось бы Вам верить. Ведь так гораздо проще реализовывать. Но вот в статье "уважаемые дяденьки" пишут... и подкинул нам её как эталон "уважаемый товарищ" )))

-

Идея хорошая. Но есть сомнения. Вот тут (страница 13, второй снизу абзац): говорится, что: Это значит, что таймер может и не с нуля начать считать...

-

При том там считается вполне достаточным использование 2 триггеров, независимо от частоты.

-

Решение нашлось: AXI Timer's Freeze input: to which port of Microblaze should I connect Freeze input to pause the timer during my UB program is paused in debugger?

-

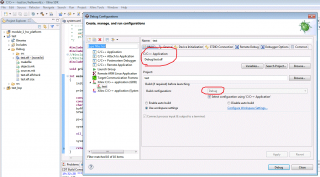

Я похоже разобрался в своей проблеме с запуском из первого поста. Это у меня лыжи не ехали, я же новичок во встраиваемых системах ))) Правда за последнее время я уже похоже на многие грабли наступил, шишек набил, можно уже из новичков меня вычёркивать) Короче дело было в том, что я не умел правильно управляться с конфигурациями запусков. Предлагаю для новичков, кто ещё будет наступать на эти грабли, следующую инструкцию. Для начала надо зайти в Run - Debug Configurations (если у вас конфигурация дебаг. Если релиз - то соответственно в Run Configurations). И удалить оттуда всё лишнее, чтобы не путаться: Затем нужно создать конфигурацию. В дереве проекта выбрать в своей конфигурации свой исполняемый файл, и нажать правой кнопкой, выбрав как на картинке (средство отладки может быть другим - какое вам нужно): В принципе всё запустится, как надо. Но если не запустилось, можно ещё раз дополнительно зайти в Run - Debug Configurations и убедиться, что в вашей конфигурации присутствуют правильные параметры (помечено красным) и главное правильные пути до нужной конфигурации и до нужного файла. Можно ещё через кнопку Browse убедиться, что это то, что надо. Можно даже для уверенности переименовать эту конфигурацию в уникальное для вас имя, чтобы быть уверенным, что это именно ваша конфигурация. Так мы создали конфигурацию запуска. В следующий раз её уже по указанной выше инструкции создавать не надо. И не надо удалять предыдущие конфигурации. Пусть у вас эта конфигурация так и будет. Чтобы запустить выполнение в следующий раз (допустим после закрытия - открытия SDK) нужно зайти в Run - Debug Configurations, выбрать ту конфигурацию, которую вы создали, и внизу нажать Debug. Всё опять запустится. Если SDK не закрывался, то при нажатии на жучка: ...запустится последняя успешно запущенная ранее конфигурация. Если SDK только что запущен, то последней конфигурации не существует. Какая последняя конфигурация запомнилась системой можно посмотреть, нажав на стрелочку рядом с жучком. Если пусто (после старта SDK) - значит ничего при нажатии на жучка и не запустится. Тогда надо запускать через Run - Debug Configurations. По этой же стрелочке можно быстро выбрать одну из последних запущенных конфигураций для текущего запуска (бывает, что конфигурации разные для разных целей). Т.е. стрелочка - это и история конфигураций, и средство выбора текущей для запуска. Если вы работаете не с конфигурацией Debug, а с Release - то всё вышеперечисленное справедливо, только в соответствующих местах слово Debug заменяется на Run. Ну вот так, сумбурно маленько, конечно - тороплюсь, поздновато уже на работе, домой пора )) Но надеюсь поможет кому-то ) А то я долго голову с этим ломал, не мог до меня дойти великий тайный смысл этих разных конфигураций.

-

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Можно. Ответ уже давали: Ну или хотя бы просто V. -

Директива ifdef verilog

Krys ответил likeasm тема в Языки проектирования на ПЛИС (FPGA)

Ну это только главный скрипт. Если было в функции - пиши пропало. Ну значит вам 4 дня потерять на коротком прогоне ничего не стоит, раз у вас там полный прогон месяцы занимает ))