-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

Я так и подумал. Ну в-общем попробовал keep_hierarchy, помогает, но только на этапе синтеза и только если синтезить корку XPS (которая собственно и содержит в себе сигналы, которые необходимо сохранить) как отдельный проект и то не для всех сигналов (хотя для большинства). После PAR эти сигналы отсутствуют. При том даже дополнительное добавление атрибута keep ничего не изменяет ни в лучшую, ни в худшую сторону. ============== По сложившейся традиции сам задал вопрос, сам отвечу )))) Решение заключается в создании дубликатов цепей и постоянном назначении им наблюдаемых сигналов. А на дубликаты уже наложить аттрибут keep, а keep_hierarchy уже не требуется. После таких действий все необходимые сигналы появились в чипскопе в полном объёме.

-

У меня XST, какой для него аналогичный констрейнт?

-

нет, этот модуль точно есть в иерархии как отдельный элемент, я это проверил (проект XPS всегда иерархию сохраняет). Забыл уточнить, извиняюсь: аттрибут я поставил в VHDL файле на сигналы.

-

Здравствуйте. В XST проблема в том, что аттрибут KEEP не действует, если в данном модуле сигнал лишь переназывается, а его источник не в данном модуле. Как всё же сохранить название сигнала в таком случае? Другими словами, например, сигнал выходит из фифошки (коргеновской) в виде широкой шины и в моём модуле разделяется чисто логически на допустим 2 шины, далее эти 2 шины подаются на другие блоки без обработки. Мне нужно для удобства наблюдения шин в Chipscope Analyzer сохранить такое разбиение одной широкой шины на 2 маленькие, т.е. нужно, чтобы в нетлисте явно присутствовали 2 маленькие шины, которые потом по отдельности можно наблюдать в чипскопе. Пока сохранить эти шины через KEEP не получается. Пробовал и SAVE, то же самое. Я понимаю, что это с одной стороны логически оправданно, раз сигнал порождён в другом модуле. Но мне то надо эти шины как-то вытянуть в целях отладки. Может кто знает какие-то обходные пути, чтобы достичь того, что мне надо? Я понимаю, что в самом Chipscope Analyzer можно вручную разбить шину, затем составить мелкие, как мне надо. Но у меня многовато шин, и при модификации прошивки большой вопрос, не придётся ли всё проделывать заново...

-

Нет, у меня корки лежат не вместе с проектом, а в отдельной папке. Но в XPS на эту папку указан путь как на репозиторий с корками.

-

У меня любые изменения в исходниках сразу применяются при следующей команде generate netlist в XPS. Корку я делал не через визард. Не экспортил, не импортил. Просто взял чужую корку и сделал по шаблону. Потом подсунул в ту же папку. Если все файлы корки правильно описаны, то корка видится средой сразу после закрытия-открытия XPS. Предполагаю, что у топикстартера какие-то параметры в файлах корки не так заданы, поэтому и изменения не подхватываются. Предлагаю сюда выложить всю её папочку в архиве. Может кто из нас посмотрит и найдёт причину. И в ISE я не работал с проектом для корки. Отлаживался в Active-HDL, потом сразу в XPS исходник этот.

-

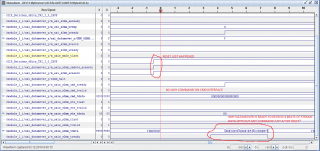

Здравствуйте. Такая вот проблема. AXI DataMover (S2MM) сразу после сброса готов принять 4 слова данных из стрима, хотя никакой команды на это ещё не было, как я понимаю, он сразу после сброса не должен держать Ready в 1, пока не поступит команда. Вот осциллограммы из ChipScope Analyzer: Так выглядит описание в файле *.mhs: BEGIN axi_datamover PARAMETER INSTANCE = axi_datamover_y PARAMETER HW_VER = 4.02.a PARAMETER C_INCLUDE_MM2S = 0 PARAMETER C_INCLUDE_S2MM = 1 PARAMETER C_INCLUDE_S2MM_DRE = 0 PARAMETER C_S2MM_BTT_USED = 23 PARAMETER C_S2MM_INCLUDE_SF = 0 PARAMETER C_S2MM_BURST_SIZE = 256 PARAMETER C_INCLUDE_S2MM_STSFIFO = 1 PARAMETER C_S2MM_STSCMD_FIFO_DEPTH = 1 PARAMETER C_S2MM_STSCMD_IS_ASYNC = 1 PARAMETER C_M_AXI_S2MM_ID_WIDTH = 3 PARAMETER C_S2MM_ADDR_PIPE_DEPTH = 4 BUS_INTERFACE M_AXI_S2MM = axi4_0 BUS_INTERFACE S_AXIS_S2MM_CMD = axi_dma_ctrl_y_M_AXIS_CMD BUS_INTERFACE M_AXIS_S2MM_STS = axi_datamover_y_M_AXIS_S2MM_STS BUS_INTERFACE S_AXIS_S2MM = axi_stream_fft_core_0_Y_AXIS PORT m_axi_s2mm_aclk = clk_75_0000MHzPLL0 PORT m_axis_s2mm_cmdsts_aresetn = DIP_Switches_4Bits_TRI_I[0] PORT m_axi_s2mm_aresetn = DIP_Switches_4Bits_TRI_I[0] PORT m_axis_s2mm_cmdsts_awclk = axi_dma_ctrl_y_axis_aclk_0 END Я использовал плату SP-605 со SPARTAN-6. Софт - ISE 14.7 (Planahead + XPS). Чтобы нагляднее продемонстрировать проблему я специально перевёл датамувер в режим асинхронных команд, чтобы был дополнительный сброс (на всякий случай). Все сбросы датамувера я подключил к DIP-Switch на отладочной плате, и захватил осциллограммы сразу после снятия сброса. Хотя проблема проявляется и без всего перечисленного, но не так наглядно. Кто-нибудь с таким сталкивался? Как лечить? Пока я делаю программный обход этой проблемы, добавляя в стрим избыточные данные (те самые 4 слова), которые будут потеряны при первой пересылке. При дальнейших пересылках всё работает как положено по датащиту.

-

До этого я ещё сразу догадался, но это не штатными средствами, а хакерство. И трудоёмко. Я ещё подумаю, нужна ли мне иерархия ценой таких временных затрат. Как в вивадо получается встроенной иерархичности в исе нет.

-

Я не сомневаюсь в Вашем устройстве, можете не хвастаться ))) Информация - из сравнения значений задержек в датащитах. Я вот тоже засомневался, особенно исходя из того, что быстродействие разное. Похоже просто "цельностянутая конструкция" ))) Но стянули чото криво )))

-

Как временное решение: в текстовом редакторе открыл в старом проекте по указанному пути файл chipscope.xml и руками перекопировал оттуда цепи, оказалось недолго

-

Получилась проблема, что проект в Planahead с XPS-ядром, дак вот перестала видиться *.ngc-шка от ядра, даже указанная явно, синтез заканчивался ошибкой, что не найдено, из чего делать модуль ядра. Пришлось пересоздавать проект, подсунув старый *.mhs, тогда всё заработало. Осталось в новом проекте вернуть старые настройки chipscope. Попробовал просто скопировать папки по пути fft_sp605\fft_sp605.data\sources_1\ - не помогает. Т.е. когда делаешь команду Setup Chipscope он начинает с пустого листа, заранее добавленных цепей в нём нет. Помогите, пожалуйста, подцепить старый чипскоп.

-

Про вивадо и так всё тут расписано. Я спрашивал про XPS из-под ISE Можно, но это коряво и трудоёмко )) Тем более это не совсем то, что хотелось бы. Хотелось вот что: взять несколько компонентов в XPS, подключить друг к другу как-то. Назвать это коркой, потом эту корку подключить в более вышестоящем проекте в XPS. И так несколько раз ))

-

Дак написали же выше, что это просто подтяжка так себя проявляет. Так на многих МК и ПЛИС

-

хм... а по нашей информации по быстродействию отечественные уступают своим аналогам...

-

Мы выработали обратный подход: в симуляционную модель (тестбенч в симуляторе) подаются одновременно входные вектора и выходные проверочные. Сам симулятор проверяет совпадение выхода модели и проверочного вектора и показывает в консоли число ошибок. Верификация пошла быстрее...

-

а ISEшный XPS (не Vivado!) умеет иерархические проекты (и корки)?

-

Здравствуйте. Наткнулся на такой вот баг Aldec Active HDL с потерей содержимого waveform при объединении сигналов в шину. Берём файлик, октрываем его в Active HDL, убеждаемся, что на сигнале clk присутствует заполнение и установлен стимулятор custom. Выделяем все сигналы, говорим Merge. Сохраняем файл. Закрываем. Открываем. Убеждаемся, что заполнение пропало... Кто-то с таким сталкивался? Много времени потратил, чтобы локализовать проблему. А то с начала не мог понять: тупо что-то меняю в своём большом файле вэйвформ, потом после сохранения он портится, работать дальше невозможно. Вот только выяснил, глюк связан с добавлением новых сигналов на вэйвформу и попытке их затолкать в уже существующую шину (группу сигналов). Понятно, что, раз уж нашёл причину, можно пока не добавлять новые сигналы в группу вообще. Но так было с группами удобно, когда сигналов много... Хотелось бы решить проблему по существу. Блин, как всегда, сам задал вопрос, сам отвечаю ))) Дальнейшие изыскания показали, что баг проявляется только, когда манипуляции с файлом вэйвформ проводятся без инициализации симуляции. Когда предварительно дать команду initialize simulation - содержимое вэйвформ не теряется. Заодно вопросы по этому же файлу. 1. Почему, когда файл открывается, то масштаб такой, что заполненная часть оказывается маленькой полоской слева? Обычно когда файл открываешь - там масштаб, что заполненная часть занимает половину экрана. Делал clear all waveforms after cursor - масштаб после открытия такой же мелкий. 2. Что за предупреждение вылазит при сохранении этого файла: "File <filename.awf> was modified outside of active design. Do you want to save this file?"? Иногда вылазит, иногда нет. Мне непонятно, кто же ещё кроме меня этот файл поменял. Я всегда соглашаюсь, но насторожен, никто же не должен кроме меня файл менять. test_bug.rar

-

Пришлось так и сделать. Публикую результат, может, будет кому-то полезно. Вот что получилось: c:\temp\test_planahead_from_svn\fft_sp605>tree /f Структура папок Серийный номер тома: 00000200 183F:C9C9 C:. │ fft_sp605.ppr │ ├───fft_sp605.data │ ├───constrs_1 │ │ designprops.xml │ │ fileset.xml │ │ usercols.xml │ │ │ ├───runs │ │ │ impl_1.psg │ │ │ runs.xml │ │ │ synth_1.psg │ │ │ │ │ ├───impl_1 │ │ │ constrs_in.xml │ │ │ constrs_out.xml │ │ │ impl_1.psg │ │ │ │ │ └───synth_1 │ │ constrs_in.xml │ │ sources.xml │ │ synth_1.psg │ │ │ ├───sim_1 │ │ fileset.xml │ │ │ └───sources_1 │ fileset.xml │ ports.xml │ ├───fft_sp605.runs │ ├───impl_1 │ │ │ download.bit │ │ │ module_1_stub.map │ │ │ module_1_stub.mrp │ │ │ module_1_stub.ucf │ │ │ module_1_stub_map.xrpt │ │ │ module_1_stub_ngdbuild.xrpt │ │ │ module_1_stub_par.xrpt │ │ │ module_1_stub_routed.par │ │ │ module_1_stub_summary.xml │ │ │ module_1_stub_usage.xml │ │ │ par_usage_statistics.html │ │ │ │ │ └───.constrs │ │ module_1_stub.ucf │ │ │ └───synth_1 ├───fft_sp605.sdk │ └───SDK │ └───SDK_Export │ ├───fft_sp605 │ │ │ .cproject │ │ │ .project │ │ │ │ │ └───src │ │ cf_read.c │ │ fft.h │ │ lscript.ld │ │ main.c │ │ platform.c │ │ platform.h │ │ platform_config.h │ │ │ └───fft_sp605_bsp │ .cproject │ .project │ .sdkproject │ libgen.options │ system.mss │ └───fft_sp605.srcs ├───constrs_1 │ └───new │ module_1_stub.ucf │ └───sources_1 └───edk └───module_1 module_1.mhs module_1.xmp module_1_stub.bmm module_1_stub.v Это конечно пока ещё не отточенный вариант, некоторые действия я ещё не пробовал с таким обрезанным проектом. Если будут поправки - может ещё сюда напишу.

-

А не подскажете, что такие тайные строки делают? )) В принципе, тут уже кучу способов привели, осталось выбрать самый простой

-

А надо?

-

Странные вопросы по VHDL

Krys ответил Unicorn тема в Языки проектирования на ПЛИС (FPGA)

Спасибо за развёрнутый ответ, теперь многое понятно. Хорошо, что Вы прояснили. Оказывается в VHDL и сигнал GSR тоже есть, и пользоваться им удобнее... ... но он не работает )))) Короче в VHDL на GSR проще забить и пользоваться самодельным типа: arst <= '1'; wait for 90 ns; arst <= '0'; -

А им и каменты знать не надо )) Я тоже так сначала подумал, воодушевился, но пока толку нет... Получилось вот так: fft_sp605.data\cache\ module_1_axi_datamover_coef_wind_wrapper_ngc_zx.edif 1149616 17.11.14 10:38:09 -> module_1_axi_datamover_in_wind_wrapper_ngc_zx.edif 1138063 17.11.14 10:38:06 -> module_1_axi_datamover_out_wind_wrapper_ngc_zx.edif 1555292 17.11.14 10:38:16 -> module_1_axi_datamover_w_wrapper_ngc_zx.edif 1103086 17.11.14 10:38:03 -> module_1_axi_datamover_x1_wrapper_ngc_zx.edif 1108840 17.11.14 10:37:56 -> module_1_axi_datamover_x2_wrapper_ngc_zx.edif 1108840 17.11.14 10:38:00 -> module_1_axi_datamover_y_wrapper_ngc_zx.edif 1499086 17.11.14 10:38:12 -> module_1_axi_dma_ctrl_coef_wind_wrapper_ngc_zx.edif 182948 17.11.14 10:38:11 -> module_1_axi_dma_ctrl_in_wind_wrapper_ngc_zx.edif 182541 17.11.14 10:38:08 -> module_1_axi_dma_ctrl_out_wind_wrapper_ngc_zx.edif 182745 17.11.14 10:38:17 -> module_1_axi_dma_ctrl_w_wrapper_ngc_zx.edif 181323 17.11.14 10:38:05 -> module_1_axi_dma_ctrl_x1_wrapper_ngc_zx.edif 181527 17.11.14 10:37:58 -> module_1_axi_dma_ctrl_x2_wrapper_ngc_zx.edif 181526 17.11.14 10:38:02 -> module_1_axi_dma_ctrl_y_wrapper_ngc_zx.edif 181324 17.11.14 10:38:14 -> module_1_axi_stream_data_width_converter_0_wrapper_ngc_zx.edif 76847 17.11.14 10:37:44 -> module_1_axi_stream_fft_core_0_wrapper_ngc_zx.edif 6829112 17.11.14 10:37:41 -> module_1_axi4_0_wrapper_ngc_zx.edif 3262380 17.11.14 10:37:38 -> module_1_axi4lite_0_wrapper_ngc_zx.edif 2087666 17.11.14 10:37:34 -> module_1_clock_generator_0_wrapper_ngc_zx.edif 25746 17.11.14 10:37:28 -> module_1_debug_module_wrapper_ngc_zx.edif 405409 17.11.14 10:37:53 -> module_1_dip_switches_4bits_wrapper_ngc_zx.edif 116456 17.11.14 10:37:22 -> module_1_leds_4bits_wrapper_ngc_zx.edif 109832 17.11.14 10:37:55 -> module_1_mcb_ddr3_wrapper_ngc_zx.edif 3205515 17.11.14 10:37:32 -> module_1_microblaze_0_bram_block_wrapper_ngc_zx.edif 168385 17.11.14 10:38:19 -> module_1_microblaze_0_d_bram_ctrl_wrapper_ngc_zx.edif 56635 17.11.14 10:37:52 -> module_1_microblaze_0_dlmb_wrapper_ngc_zx.edif 28347 17.11.14 10:37:31 -> module_1_microblaze_0_i_bram_ctrl_wrapper_ngc_zx.edif 56635 17.11.14 10:37:50 -> module_1_microblaze_0_ilmb_wrapper_ngc_zx.edif 28347 17.11.14 10:37:29 -> module_1_microblaze_0_wrapper_ngc_zx.edif 7557039 17.11.14 10:37:48 -> module_1_ngc_zx.edif 2715050 17.11.14 10:37:18 -> module_1_proc_sys_reset_0_wrapper_ngc_zx.edif 118265 17.11.14 10:37:26 -> module_1_push_buttons_4bits_wrapper_ngc_zx.edif 116456 17.11.14 10:37:20 -> module_1_rs232_uart_1_wrapper_ngc_zx.edif 305854 17.11.14 10:37:25 -> module_1_stub_ngc_zx.edif 43595 17.11.14 10:37:15 -> module_1_sysace_compactflash_wrapper_ngc_zx.edif 280429 17.11.14 10:37:23 -> fft_sp605.data\runs\impl_1\ constrs_out.xml 2181 18.11.14 10:22:00 -> fft_sp605.runs\.jobs\ job1.bat 463 14.11.14 15:17:51 -> job1.sh 462 14.11.14 15:17:51 -> job2.bat 461 14.11.14 15:20:25 -> job2.sh 460 14.11.14 15:20:25 -> job3.bat 461 14.11.14 15:33:00 -> job3.sh 460 14.11.14 15:33:00 -> job4.bat 463 17.11.14 10:36:02 -> job4.sh 462 17.11.14 10:36:02 -> job5.bat 461 17.11.14 10:38:29 -> job5.sh 460 17.11.14 10:38:29 -> job6.bat 461 17.11.14 10:50:22 -> job6.sh 460 17.11.14 10:50:22 -> job7.bat 461 18.11.14 09:47:20 -> job7.sh 460 18.11.14 09:47:20 -> fft_sp605.runs\impl_1\ 1.bitgen.begin.rst 180 18.11.14 09:59:33 -> 1.bitgen.end.rst 0 18.11.14 10:00:46 -> 1.data2mem.begin.rst 182 18.11.14 10:00:46 -> 1.data2mem.end.rst 0 18.11.14 10:00:47 -> 1.ISE.queue.rst 3 18.11.14 09:47:20 -> 1.map.begin.rst 177 18.11.14 09:48:40 -> 1.map.end.rst 0 18.11.14 09:56:07 -> 1.ngdbuild.begin.rst 183 18.11.14 09:47:20 -> 1.ngdbuild.end.rst 0 18.11.14 09:48:40 -> 1.par.begin.rst 178 18.11.14 09:56:07 -> 1.par.end.rst 0 18.11.14 09:58:36 -> 1.trce.begin.rst 179 18.11.14 09:58:36 -> 1.trce.end.rst 0 18.11.14 09:59:17 -> 1.xdl.begin.rst 178 18.11.14 09:59:17 -> 1.xdl.end.rst 0 18.11.14 09:59:33 -> 1debug_nets.cdc 8744 18.11.14 09:47:16 -> 1download.bit 1484808 18.11.14 10:00:46 -> 1htr.txt 824 18.11.14 09:47:19 -> 1ISEWrap.js 4770 18.11.14 09:47:19 -> 1ISEWrap.sh 1626 18.11.14 09:47:19 -> 1module_1_stub.bgn 16025 18.11.14 10:00:31 -> 1module_1_stub.bit 1484808 18.11.14 10:00:31 -> 1module_1_stub.bld 5631 18.11.14 09:48:39 -> 1module_1_stub.bmm 1656 18.11.14 09:47:18 -> 1module_1_stub.drc 9700 18.11.14 09:59:49 -> 1module_1_stub.edf 35304649 18.11.14 09:47:18 -> 1module_1_stub.log 177 18.11.14 09:48:10 -> 1module_1_stub.map 17550 18.11.14 09:56:07 -> 1module_1_stub.mrp 891668 18.11.14 09:56:07 -> 1module_1_stub.ncd 2263326 18.11.14 09:56:06 -> 1module_1_stub.ngd 18105217 18.11.14 09:48:38 -> 1module_1_stub.ngm 23280488 18.11.14 09:49:01 -> 1module_1_stub.pcf 4452410 18.11.14 09:56:01 -> 1module_1_stub.twr 905337 18.11.14 09:59:17 -> 1module_1_stub.twx 979999 18.11.14 09:59:16 -> 1module_1_stub.ucf 24794 18.11.14 09:47:18 -> 1module_1_stub_bd.bmm 1724 18.11.14 09:59:47 -> 1module_1_stub_bitgen.xwbt 345 18.11.14 10:00:31 -> 1module_1_stub_map.xrpt 59133 18.11.14 09:56:07 -> 1module_1_stub_ngdbuild.xrpt 40133 18.11.14 09:48:39 -> 1module_1_stub_par.xrpt 260299 18.11.14 09:58:34 -> 1module_1_stub_routed.ncd 4417262 18.11.14 09:58:34 -> 1module_1_stub_routed.pad 22547 18.11.14 09:58:31 -> 1module_1_stub_routed.par 30734 18.11.14 09:58:35 -> 1module_1_stub_routed.ptwx 24442 18.11.14 09:58:30 -> 1module_1_stub_routed.unroutes 4575 18.11.14 09:58:31 -> 1module_1_stub_routed.xdl 845922 18.11.14 09:59:33 -> 1module_1_stub_routed.xpi 46 18.11.14 09:58:34 -> 1module_1_stub_routed_pad.csv 22579 18.11.14 09:58:30 -> 1module_1_stub_routed_pad.txt 104552 18.11.14 09:58:31 -> 1module_1_stub_summary.xml 408 18.11.14 10:00:32 -> 1module_1_stub_usage.xml 261291 18.11.14 10:00:32 -> 1par_usage_statistics.html 4164 18.11.14 09:58:25 -> 1rundef.js 2430 18.11.14 09:47:19 -> 1runme.bat 246 18.11.14 09:47:19 -> 1runme.log 55154 18.11.14 10:00:47 -> 1runme.sh 2102 18.11.14 09:47:19 -> 1webtalk.log 660 18.11.14 10:00:45 -> 1fft_sp605.runs\impl_1\.constrs\ 1module_1.ncf 2513 18.11.14 09:47:18 -> 1module_1_axi4_0_wrapper.ncf 213 18.11.14 09:47:18 -> 1module_1_axi4lite_0_wrapper.ncf 237 18.11.14 09:47:18 -> 1module_1_clock_generator_0_wrapper.ncf 0 18.11.14 09:47:18 -> 1module_1_mcb_ddr3_wrapper.ncf 10561 18.11.14 09:47:18 -> 1module_1_microblaze_0_dlmb_wrapper.ncf 173 18.11.14 09:47:18 -> 1module_1_microblaze_0_ilmb_wrapper.ncf 173 18.11.14 09:47:18 -> 1module_1_microblaze_0_wrapper.ncf 176 18.11.14 09:47:18 -> 1module_1_stub.ucf 0 18.11.14 09:47:19 -> 1module_1_sysace_compactflash_wrapper.ncf 490 18.11.14 09:47:18 -> 1fft_sp605.runs\impl_1\_ngo\ 1module_1_stub.ngo 15039678 18.11.14 09:48:10 -> 1netlist.lst 97 18.11.14 09:48:39 -> 1fft_sp605.runs\impl_1\_xmsgs\ 1bitgen.xmsgs 12509 18.11.14 10:00:33 -> 1map.xmsgs 15131 18.11.14 09:56:07 -> 1ngdbuild.xmsgs 6820 18.11.14 09:48:39 -> 1par.xmsgs 10694 18.11.14 09:58:35 -> 1trce.xmsgs 1488 18.11.14 09:59:17 -> 1xdl.xmsgs 512 18.11.14 09:59:33 -> 1fft_sp605.runs\impl_1\xlnx_auto_0_xdb\ 1cst.xbcd 1757046 18.11.14 09:48:37 -> 1fft_sp605.runs\synth_1\ 1.xst.begin.rst 177 17.11.14 10:36:02 -> 1.xst.end.rst 0 17.11.14 10:37:10 -> 1.XST.queue.rst 3 17.11.14 10:36:02 -> 1htr.txt 372 17.11.14 10:36:01 -> 1ISEWrap.js 4770 17.11.14 10:36:01 -> 1ISEWrap.sh 1626 17.11.14 10:36:01 -> 1module_1_stub.lso 6 17.11.14 10:36:12 -> 1module_1_stub.ngc 18314 17.11.14 10:37:10 -> 1module_1_stub.ngc_xst.xrpt 10590 17.11.14 10:37:10 -> 1module_1_stub.prj 221 17.11.14 10:36:01 -> 1module_1_stub.srp 101280 17.11.14 10:37:10 -> 1module_1_stub.xst 252 17.11.14 10:36:01 -> 1rundef.js 1517 17.11.14 10:36:01 -> 1runme.bat 246 17.11.14 10:36:01 -> 1runme.log 55346 17.11.14 10:37:09 -> 1runme.sh 1342 17.11.14 10:36:01 -> 1fft_sp605.runs\synth_1\_xmsgs\ 1xst.xmsgs 63997 17.11.14 10:37:10 -> 1fft_sp605.runs\synth_1\xst\work\ 1work.sdbl 688958 17.11.14 10:36:12 -> 1work.sdbx 1482 17.11.14 10:36:12 -> fft_sp605.srcs\sources_1\edk\module_1\ platgen.log 38389 17.11.14 10:31:39 -> fft_sp605.srcs\sources_1\edk\module_1\__xps\ise\_xmsgs\ platgen.xmsgs 36444 17.11.14 10:31:39 -> fft_sp605.srcs\sources_1\edk\module_1\implementation\ module_1.bmm 846 17.11.14 10:21:06 -> module_1.ngc 2225154 17.11.14 10:32:52 -> module_1_axi_datamover_coef_wind_wrapper.ngc 263225 17.11.14 10:31:06 -> module_1_axi_datamover_in_wind_wrapper.ngc 260917 17.11.14 10:30:53 -> module_1_axi_datamover_out_wind_wrapper.ngc 360257 17.11.14 10:31:32 -> module_1_axi_datamover_w_wrapper.ngc 253993 17.11.14 10:30:40 -> module_1_axi_datamover_x1_wrapper.ngc 255147 17.11.14 10:30:14 -> module_1_axi_datamover_x2_wrapper.ngc 255147 17.11.14 10:30:27 -> module_1_axi_datamover_y_wrapper.ngc 348980 17.11.14 10:31:19 -> module_1_axi_dma_ctrl_coef_wind_wrapper.ngc 48473 17.11.14 10:31:13 -> module_1_axi_dma_ctrl_in_wind_wrapper.ngc 48469 17.11.14 10:30:59 -> module_1_axi_dma_ctrl_out_wind_wrapper.ngc 48471 17.11.14 10:31:38 -> module_1_axi_dma_ctrl_w_wrapper.ngc 48457 17.11.14 10:30:46 -> module_1_axi_dma_ctrl_x1_wrapper.ngc 48459 17.11.14 10:30:20 -> module_1_axi_dma_ctrl_x2_wrapper.ngc 48459 17.11.14 10:30:33 -> module_1_axi_dma_ctrl_y_wrapper.ngc 48457 17.11.14 10:31:26 -> module_1_axi_stream_data_width_converter_0_wrapper.ngc 19186 17.11.14 10:26:28 -> module_1_axi_stream_fft_core_0_wrapper.ngc 1610951 17.11.14 10:30:07 -> module_1_axi4_0_wrapper.ngc 985893 17.11.14 10:29:54 -> module_1_axi4lite_0_wrapper.ngc 686455 17.11.14 10:29:48 -> module_1_clock_generator_0_wrapper.ngc 9319 17.11.14 10:29:42 -> module_1_debug_module_wrapper.ngc 115630 17.11.14 10:23:21 -> module_1_dip_switches_4bits_wrapper.ngc 32673 17.11.14 10:26:01 -> module_1_leds_4bits_wrapper.ngc 31262 17.11.14 10:25:48 -> module_1_mcb_ddr3_wrapper.ngc 771668 17.11.14 10:30:01 -> module_1_microblaze_0_bram_block_wrapper.ngc 52071 17.11.14 10:22:04 -> module_1_microblaze_0_d_bram_ctrl_wrapper.ngc 46719 17.11.14 10:21:55 -> module_1_microblaze_0_dlmb_wrapper.ngc 12630 17.11.14 10:29:28 -> module_1_microblaze_0_i_bram_ctrl_wrapper.ngc 46720 17.11.14 10:21:36 -> module_1_microblaze_0_ilmb_wrapper.ngc 12630 17.11.14 10:29:22 -> module_1_microblaze_0_wrapper.ngc 2665358 17.11.14 10:29:35 -> module_1_proc_sys_reset_0_wrapper.ngc 25435 17.11.14 10:21:17 -> module_1_push_buttons_4bits_wrapper.ngc 31909 17.11.14 10:25:10 -> module_1_rs232_uart_1_wrapper.ngc 68823 17.11.14 10:24:57 -> module_1_sysace_compactflash_wrapper.ngc 65955 17.11.14 10:24:45 -> fft_sp605.srcs\sources_1\edk\module_1\implementation\cache\ cache.cat 74831 17.11.14 10:31:39 -> module_1_axi_datamover_coef_wind_wrapper.ngc 263225 17.11.14 10:31:39 -> module_1_axi_datamover_in_wind_wrapper.ngc 260917 17.11.14 10:31:39 -> module_1_axi_datamover_out_wind_wrapper.ngc 360257 17.11.14 10:31:39 -> module_1_axi_datamover_w_wrapper.ngc 253993 17.11.14 10:31:39 -> module_1_axi_datamover_x1_wrapper.ngc 255147 17.11.14 10:31:39 -> module_1_axi_datamover_x2_wrapper.ngc 255147 17.11.14 10:31:39 -> module_1_axi_datamover_y_wrapper.ngc 348980 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_coef_wind_wrapper.ngc 48473 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_in_wind_wrapper.ngc 48469 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_out_wind_wrapper.ngc 48471 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_w_wrapper.ngc 48457 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_x1_wrapper.ngc 48459 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_x2_wrapper.ngc 48459 17.11.14 10:31:39 -> module_1_axi_dma_ctrl_y_wrapper.ngc 48457 17.11.14 10:31:39 -> module_1_axi_stream_data_width_converter_0_wrapper.ngc 19186 17.11.14 10:31:39 -> module_1_axi_stream_fft_core_0_wrapper.ngc 1610951 17.11.14 10:31:39 -> module_1_axi4_0_wrapper.ngc 985893 17.11.14 10:31:38 -> module_1_axi4lite_0_wrapper.ngc 686455 17.11.14 10:31:38 -> module_1_clock_generator_0_wrapper.ngc 9319 17.11.14 10:31:38 -> module_1_debug_module_wrapper.ngc 115630 17.11.14 10:31:38 -> module_1_dip_switches_4bits_wrapper.ngc 32673 17.11.14 10:31:39 -> module_1_leds_4bits_wrapper.ngc 31262 17.11.14 10:31:38 -> module_1_mcb_ddr3_wrapper.ngc 771668 17.11.14 10:31:38 -> module_1_microblaze_0_bram_block_wrapper.ngc 52071 17.11.14 10:31:38 -> module_1_microblaze_0_d_bram_ctrl_wrapper.ngc 46719 17.11.14 10:31:38 -> module_1_microblaze_0_dlmb_wrapper.ngc 12630 17.11.14 10:31:38 -> module_1_microblaze_0_i_bram_ctrl_wrapper.ngc 46720 17.11.14 10:31:38 -> module_1_microblaze_0_ilmb_wrapper.ngc 12630 17.11.14 10:31:38 -> module_1_microblaze_0_wrapper.ngc 2665358 17.11.14 10:31:38 -> module_1_proc_sys_reset_0_wrapper.ngc 25435 17.11.14 10:31:38 -> module_1_push_buttons_4bits_wrapper.ngc 31909 17.11.14 10:31:38 -> module_1_rs232_uart_1_wrapper.ngc 68823 17.11.14 10:31:38 -> module_1_sysace_compactflash_wrapper.ngc 65955 17.11.14 10:31:38 -> Короче, если посмотреть, какие папки отсутствуют, - то видно, что парочка кэшей да результаты имплемента, которые я бы и сам догадался не добавлять в репозиторий. Так что это пока не то, что я бы ожидал, должно быть куда больше избыточного мусора...

-

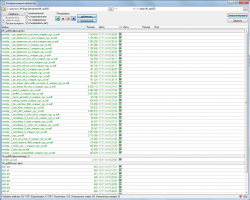

Спасибо, но, видимо, не вариант. Вот что в результате не вошло в архив: Т.е. это буквально несколько папок. Уверен, что нужны далеко не все. Я, правда, поставил галочку также добавить в архив результаты имплемента, но уж с имплементом я и своими мозгами могу разобраться...

-

Вы видели в исходном сообщении дерево проекта, сколько там папок? А ещё больше файлов в каждой папке. Именно поэтому я прошу поделиться уже готовым опытом, может, кто-то уже это проделал. Когда имплемент длится сутки, а даже генерация битстрима занимает полчаса, то становится плевать на размеры репозитория, удобство работы важнее. А работодатель купит дополнительный терабайтник. Вот что точно раздует репозиторий - это слепое добавление всего проекта, со всеми его потрохами. Но пока если есть необходимость контроля версий, но нет знания, какие папки и файлы оставить (о чём я тут собственно и спрашиваю), то остаётся только так и делать... А при коммите нельзя написать описание? Обычно то, что необязательно требуется - то и забывается/забивается. А при коммите окошко комментария хоть как вылазит, приходится честно писать, что где понаменял )) Ну собственно это использование папки по прямому назначению ))) Не совсем соглашусь. XPS к FPGA привязан довольно жёстко. Софт - тоже разный бывает. Есть наподобие std_lib, то конечно это должно в отдельной папке лежать, независимо от конкретного проекта. А есть исходники, которые касаются только этого проекта, их нужно хранить не раздельно. Это касается как исходников микроблэйза, так и плисочных исходников.

-

Спасибо. Но можно уточнение по конкретным папкам? Потому что умом то я и так понимаю всё, что Вы написали. А вот какие конкретно папки - вопрос... Я рассчитывал, что кто-то поделится в этой теме своим конкретным опытом. Что, мол, я добавляю в SVN конкретно те-то и те-то папки, а в них те-то файлы. Немножко уточню свой вопрос: без добавления некоторых папок файл проекта отказывается открываться. Так, например, если в папке проекта удалить папку fft_sp605.data (это для моего примера), то вы этот проект потом не откроете. Это я обнаружил экспериментальным путём, но папок много, поэтому все проверять замучаешься. Цель моего вопроса: добавить в репозиторий определённый необходимый и достаточный набор файлов и папок. Затем я, допустим, всё удалил на своём локальном компе. Затем хочу взять проект из репозитория. Делаю checkout этого проекта, и всё открывается, всё может быть имплементировано. Так вот, например, если я забуду добавить ту же папку fft_sp605.data, то потом ничего не откроется, и считай, что зря добавлял в репозиторий, проект пропал. Поэтому мне хотелось бы знать конкретный набор файлов и папок, может, кто-то уже проходил этот путь.