Поиск

Показаны результаты для тегов 'fpga'.

-

Переход с Altera на Gowin

GDS опубликовал тема в Предлагаю работу

Добрый день. Ищем программиста ПЛИС. Территориально находимся в г. Лобня. Необходимо осуществить переход с Altera 10M08SAE144 на Gowin. На альтере код полностью отлажен, есть все исходники, вся документация. Заинтересовавшихся прошу писать на [email protected] или на [email protected] -

Куплю terasic de10-standard

BeetRootRage опубликовал тема в Куплю

Куплю отладочную плату terasic de10-standard (новую или б/у)- 1 ответ

-

- fpga

- de10-standard

-

(и ещё 3 )

C тегом:

-

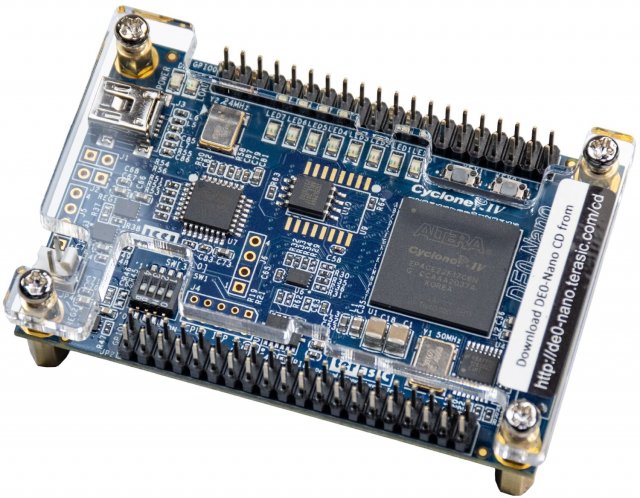

Отладочная плата Terasic DE0-Nano с ПЛИС Cyclone IV (Москва)

pavlovconst опубликовал тема в Продам

Продаю свою отладочную плату. Состояние - идеальное, все работает. Комплект: Без коробки, кабелей, стоечек и акриловой накладки. USB-Blaster интегрирован на плате, поэтому идет в комплекте ;) Цена 9999 р. Для сравнения, цены в магазинах: https://www.chipdip.ru/product/de0-nano https://www.terraelectronica.ru/product/675579 Технические характеристики: -

Нужен xilinx 7 серии, pcie m.2 Acorn cle-215+, litefury, nitrefury и другие

-

- fpga

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

Странное поведение Cyclone 4

AlexSailor опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток. На днях приобрел отладочную плату RZ-easyFPGA A2.2 с кристаллом Cyclone 4 (ep4ce6e22c8n). Начав тестировать вводы-выводы элементарными программами, столкнулся с тем, что плата воспринимает элемент И как ИЛИ и наоборот. С чем это может быть связано? Спасибо. -

Seal 5000 от isilicontek

makc опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую участников форума, В связи с понятными всем событиями Gowin тоже приказал нам долго жить и ушёл от нас, поэтому активизировался поиск альтернатив и я набрёл на пару вариантов: http://www.isilicontek.com/page29 http://www.isilicontek.com/page28 У кого-нибудь был опыт работы с этими ПЛИС? Что у них со средой разработки, с описаниями на английском языке? Есть ли представители в России? По виду это похоже на Artix-7 или около того. Но на сколько оно соответствует декларируемым возможностям и как оно себя ведёт в жизни для меня большой вопрос. -

amd AMD завершила сделку по приобретению Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Компания AMD объявила о завершении приобретения компании Xilinx в рамках сделки с полным пакетом акций. Приобретение, о котором первоначально было объявлено 27 октября 2020 года, создает лидера отрасли в области высокопроизводительных и адаптивных вычислений со значительно увеличенным масштабом деятельности и самым лучшим портфелем передовых вычислительных, графических и адаптивных продуктов (SoC). Подробнее -

PCIe и Cyclone 4 GX

Ilya_Msk99 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Появилась задача поднять PCIe на FPGA (на руках плата с Cyclone 4 GX). Сложности возникают абсолютно на всех стадиях. Сгенерировать Hard IP согласно документации Intel вроде и получается, однако даже со сборкой проекта огромное количество проблем, так как из-за не понимая интерфейса IP ядра не понятно что с чем соединять (очевидно что за информацией нужно идти в альтеровскую документацию на IP ядро, но из-за недостатка опыта не получается вытащить от туда необходимую информацию). Также сложность заключается в том, что почти все проекты в свободном доступе для Xilinx. Буду рад любой помощи от более опытных разработчиков: проекты, ссылки, описания и т д. -

Описываю поведение простого UART-передатчика на Verilog в среде Xiling Vivado 2018.2. При присваивании D-триггеру значения с входного порта, он переходит в Z-состояние. Также при попытке присвоить этот сигнал цепи через оператор непрерывного присваивания assign, цепь также принимает высокоимпедансное состояние. В чем может быть причина такого поведения/симуляции, и как это можно исправить? Описание модуля следующее:

- 12 ответов

-

- fpga xilinx

- verilog

-

(и ещё 3 )

C тегом:

-

Организаторы проведут интерактивную сессию вопросов и ответов с менеджером по линейке продуктов и техническим экспертом – представителями Xilinx. Подробнее

-

вебинар Знакомство с экосистемой Xilinx. Вебинар

МакроГрупп опубликовал тема в Объявления пользователей

На вебинаре Вы узнаете, какие готовые устройства и отладочные платы существуют, какие фреймворки и библиотеки можно использовать для ускорения приложений и где найти всю необходимую информацию. Подробнее -

modelsim Моделирование видеоматрицы в ModelSim

SemenSkor опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день! Нужно смоделировать поведение камеры в Model Sim . Есть готовое изображение. Нужно считать построчно значение яркости каждого пикселя и выдать эти значения в Wave в Model Sim. Это вообще возможно? -

-

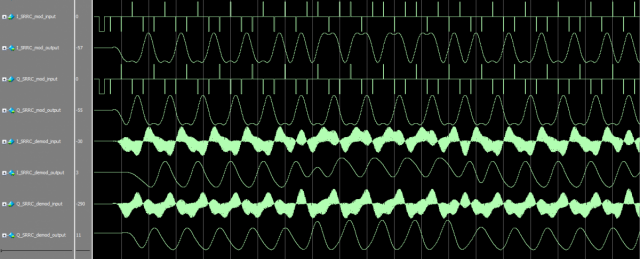

Отклик SRRC в QPSK демодуляторе

Zalman_ опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день, столкнулся с такой проблемой. Делаю демодулятор QPSK на FPGA Есть QPSK модулятор и соответственно QPSK демодулятор. В модуляторе используется SRRC, что автоматически добавляет такой же SRRC на сторону приемника. В процессе модуляции все происходит корректно и передается на приемник. Замечу, что так как проект сделан на ПЛИС (на данный момент только в коде, то как таковой задержки в чем-либо между модулятором и демодулятором нет). Также отмечу, что SRRC, NCO и частоты идентичны друг другу. По идее, на приемной стороне с выхода SRRC на синфазной и на квадратурной составляющей я должен видеть примерно ту же "картину", что и на выходе SRRC, который стоит в модуляторе. Однако при идентичности параметров и фильтров на приемной стороне SRRC выдает специфичный сигнал, который вроде бы и похож, но тем не менее не соответствует сигналу, получаемому из SRRC в модуляторе. Скрин приложил Скрин из программы ModelSim На скрине входы и выходы SRRC на I и Q в модуляторе и демодуляторе. -

Компания Xilinx объявила о приобретении Silexica – частной компании-разработчика инструментов для программирования и анализа на языках C/C ++. Набор инструментов Silexica SLX FPGA позволяет разработчикам получить полезный опыт разработки приложений на FPGA и адаптивных SoC. Данная технология будет интегрирована в унифицированную программную платформу Xilinx Vitis™, чтобы существенно сократить время обучения разработчиков программного обеспечения, создающих сложные приложения на основе технологии Xilinx. Подробнее

-

Использование UVM

AntonB опубликовал тема в Методы и средства верификации ПЛИС/ASIC

Посоветуйте материал для изучения UVM ?- 27 ответов

-

- fpga

- verification

-

(и ещё 1 )

C тегом:

-

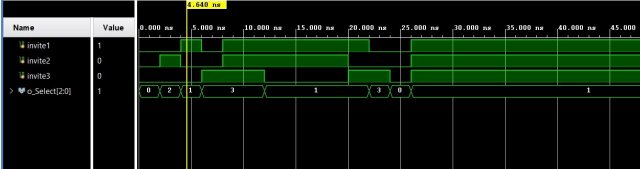

Всем добрый день, я новичок в FPGA. В проектах использую Verilog. Появилась задача сделать mux со справедливым обслуживанием. На входе 3 однобитных (С потенциальным расширением) сигнала, на выходе управляющая (3bit). На входы в различных комбинациях могут приходить "Запросы". На выходе должен быть сформирована управляющая последовательность для mux и переключаться в соответствии с тем в какой очереди поступили сигналы. У меня получилось написать вариацию, симуляция проходит предсказуемо, но после синтеза лезут warning о комбинационных петлях. Подскажите пожалуйста как решить эти варнинги и правильный ли вообще подход к решению задачи. PS Так же я знаю что есть проблема с переполнением счетчика, пока не понимаю как правильно сделать защиту(кроме заведомо большого размера счетчика). Код модуля: testbench: Симуляция с ожидаемым результатом:

- 7 ответов

-

- verilog новичок

- mux

-

(и ещё 1 )

C тегом:

-

Начну с основной проблемы. Потребовалось выполнить несколько операций ЦОС на ПЛИС. Разобравшись с языками описания цифровых схем были созданы три модуля: для БПФ, для взаимной корреляции сигнала и ещё один математический. По отдельности они проходили проверку работоспособности в железе на столе, но иногда всё разваливалось: бывали неудачные случаи разводки и результаты были неадекватные. После объединения всех трёх модулей в один проект работоспособная прошивка и вовсе перестала получаться. Почитав форумы и статьи понял, что может помочь задание временных ограничений на пути прохождения сигнала. (Например: "Если временные требования не заданы, то компилятор не производит оптимизацию задержек и они имеют произвольные значения и большой разброс." Источник: Lab1.pdf (spbstu.ru)) Я начал заниматься описанием временных ограничений, вижу на Chip Planer, что пути меняются, но какие-либо выводы по этому сделать не могу. Поэтому хотелось бы получить совет от тех, кто уже этим успешно занимался. Правильно ли вычислена ошибка? В верном ли направлении двигаюсь? Правильно ли мной описаны временные задержки блока БПФ: я описал прохождение сигнала из входной памяти (FFT:inst2, FFT:inst4 проекта) на бабочку (FFT:inst23), с результата вычисления бабочки до буферной памяти (FFT:inst21, FFT:inst22) и из буферной памяти до входа в бабочку при условии, что выполнение бабочки и установка адресов памяти выполняется не дольше, чем за 80 нс? Весь проект для Quartus II 13.0.1: MainDD3.zip — RGhost — файлообменник Ниже прикреплён файл временных ограничений sdc. P.S. Разработка ведётся под ПЛИС 5578ТС024. Для её конфигурирования используется прилагающееся к ПЛИС ПО и список цепей vqm из Quartus. Собственное ПО ПЛИС – одна из причин почему не использовалась мегафункция БПФ. Также для одного и того же списка цепей ПО может выдать как работоспособную прошивку, так и нет. В ПО есть возможность подгрузки файла временных ограничений, но тоже со своими особенностями. Если кто-то может и имеет желание помочь разобраться в этом, то оставьте контакт в телеграмм. MainDD3.sdc

-

Xilinx Versal AI Edge Series

МакроГрупп опубликовал тема в Объявления пользователей

Versal AI Edge Series – самая масштабируемую и адаптируемая платформа для оконечных и встроенных систем от Xilinx Подробнее -

СПб - ищем схемотехников и программистов

_LD опубликовал тема в Предлагаю работу

Здравствуйте, уважаемые форумчане! В команду требуются разработчики, ищем специалистов в следующих областях (разработка спецтехники): - разработка схемотехники цифровых устройств – FPGA, DSP, PCIE, SRIO, Ethernet, JESD204; - разработка ПО для FPGA (Xilinx, стык с АЦП/ЦАП, ЦОС, интерфейсы); - разработка ПО для DSP; - разработка ПО для ARM (в т.ч. Embedded Linux); - разработка схемотехники аналоговых СВЧ-устройств (частотно-избирательные цепи на распределенных эл-тах, усилители мощности AB-класса, ЭМС). Зарплаты определяются по результатам собеседования (ориентировочно для первых двух категорий 110 – 170 т.р. на руки). Условия работы – полная занятость, оформление по ТК РФ. http://www.nppntt.ru/ Территориально – СПб, ст. м. Академическая Контакты: Веженков Денис +7 911 294 16 64, звонить с 10 до 17 часов. [email protected] -

Этот курс включает в себя лекции, лабораторные занятия и демонстрации, которые помогут вам оптимизировать энергетические и тепловые решения с помощью Versal ACAP. Подробнее

-

Инженеров-разработчиков и сотрудников ИТ-отделов приглашаем принять участие в техническом семинаре, посвящённом новейшим продуктам компании Xilinx. Семинар пройдёт в городе Минск 24 мая Подробнее

-

Адаптивные SoM-модули Kria от Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Компания Xilinx анонсировала выпуск собственных адаптивных SoM-модулей (Система-на-Модуле) серии Kria. SoM модули Kria – это новый способ быстрого развёртывания производительных решений Xilinx в сфере Искусственного интеллекта (ИИ) на конечных устройствах. Подробности-

- som

- xilinx ise

- (и ещё 5 )

-

В данном вебинаре будут рассмотрены основные достоинства и недостатки использования SoM-модулей, как они могут ускорить проектирование и производство готовых устройств и как изменится процесс разработки ПО, если вы будете использовать модули в своих проектах. Также представитель компании «Рифтек» расскажет об одном из реальных проектов, в котором использовались SoM-модули компании Trenz Electronic. Подробнее