Поиск

Показаны результаты для тегов 'quartus'.

-

Странное поведение Cyclone 4

AlexSailor опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток. На днях приобрел отладочную плату RZ-easyFPGA A2.2 с кристаллом Cyclone 4 (ep4ce6e22c8n). Начав тестировать вводы-выводы элементарными программами, столкнулся с тем, что плата воспринимает элемент И как ИЛИ и наоборот. С чем это может быть связано? Спасибо. -

modelsim Моделирование видеоматрицы в ModelSim

SemenSkor опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день! Нужно смоделировать поведение камеры в Model Sim . Есть готовое изображение. Нужно считать построчно значение яркости каждого пикселя и выдать эти значения в Wave в Model Sim. Это вообще возможно? -

Quartus Prime Lite 20.1.1 Build 720, FPGA Cyclone IV E (EP4CE10E22C8). Для реализации I2C интерфейса необходимо опрашивать состояние двунаправленного порта, который имеет внешние подтягивающие резисторы. Полный код тестового модуля: module OpenDrain ( input clk_main, inout scl_i2c, inout sda_i2c, input scl_out, input sda_out, output reg scl_in, output reg sda_in ); // Debounce and deglitch input signals reg [2:0] sda_ff, scl_ff; always @ (posedge clk_main) begin scl_ff <= {scl_ff[1:0], scl_i2c}; if (~|scl_ff) scl_in <= 0; else if ( &scl_ff) scl_in <= 1; sda_ff <= {sda_ff[1:0], sda_i2c}; if (~|sda_ff) sda_in <= 1'b0; else if ( &sda_ff) sda_in <= 1'b1; end assign scl_i2c = (scl_out) ? 1'bz : 1'b0; assign sda_i2c = (sda_out) ? 1'bz : 1'b0; endmodule Инициирующая последовательность тестовых сигналов выглядит как на pic01. Здесь два OPEN DRAIN порта: scl_i2c и sda_i2c. В первом случае инициирущий тестовый сигнал всегда в "z" состоянии, а во втором, в моменты, когда порт должен подтягиваться к шине питания, вручную заданы состояния Weak High. Результирующие сигналы представлены на pic02 (для Quartus) и pic03 (для ModelSim). Как видно, для scl_i2c порта входное "z" состояние воспринимается как состояние "x", в то время как у sda_i2c таких проблем нет. Вот здесь написано, что в Assignment Editor можно включить опцию Passive Resistor. Но там такой опции НЕТ. Включение этой опции вручную (set_instance_assignment -name PASSIVE_RESISTOR "PULL-UP" -to scl_i2c) в qsf файл не дало никакого эффекта. Что еще пробовал. - добавлял внутренний pullup резистор (set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to scl_i2c). - пробовал в .vo файле менять параметр для cycloneive_io_ibuf с .simulate_z_as = "z" на .simulate_z_as = "1". - пробовал в коде указывать net_type как tri1: ... tri1 (strong0,strong1) tr1 = scl_i2c; always @ (posedge clk_main) ... scl_ff <= {scl_ff[1:0], tr1}; ... Существует ли способ симулировать (функциональная симуляция) эти внешние резисторы. Т.е. при состоянии "z" на порте, входная логика должна воспринимать это как лог.1. P.S. Прилагаю проект. Если у кого возникнет желание проверить симуляцию в ModelSim, то для облегчения, достаточно выполнить в нем переход в директорию "...\simulation\qsim\" (File => Change Directory...), а затем запустить tcl скрипт MyTest_DO.do (Tools => Tcl => Execute Macro...). OpenDrain.rar

-

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Здравствуйте! Возникла проблема с прошивкой Cyclone V (платы DE0-Nano-SoC и DE1-SoC), включающей Nios II. Заливка на пустую ПЛИС производится спокойно, но если на ней уже работает Nios II (с залитой прошивкой), то программатор в Квартусе выдаёт ошибку. В итоге всё решается только отключением и включением питания. Причём, даже зажатая кнопка reset (для Nios) не помогает. Причём, если Nios есть, но не залита его прошивка, то ПЛИС нормально перепрошивается. Подскажите, пожалуйста, в чём может быть проблема?

-

Quartus скриптинг

RobFPGA опубликовал тема в Среды разработки - обсуждаем САПРы

Приветствую! Пытаюсь вот вникнуть в нюансы скриптинга под Qu. Но что то туго идет - видать грибы в наше местности не такие забористые как у разработчиков . Хочу сваять скрип который делает билд несколькими этапами с модификацией настроек между билдами. Для этого используя qurtus_sh и в соответствии с наставлениями "Quartus II Scripting Reference Manual" создаю пустой проект. Теперь надо бы наполнит его содержимым, но чтобы опять не набивать лишние пару тысяч строк настроек можно же использовать source готовых настроек project_new -overwrite -revision $rev $prj source "project_all_setings.qsf" project_close Вроде все ок, проект создался - но портянка получающаяся в project.qsf удручает. Думаю, можно же сделать и так project_new -overwrite -revision $rev $prj set_global_assignment -name FAMILY "Stratix V" set_global_assignment -name DEVICE 5SGXEABK2H40C2 set_global_assignment -name NUM_PARALLEL_PROCESSORS 4 project_close set fou [open "$rev.qsf" "a"] puts $fou "\n" puts $fou "#==============================================================================" puts $fou "source \"./project_all_setings.qsf\"" puts $fou "#==============================================================================" close $fou ... Тогда в qsf проекта будет только ссылка/source со всеми настройками - красота! В GUI это работает и позволяет контролировать бардак в головах qsf. И действительно - на диске получается красивый qsf ... set_global_assignment -name TOP_LEVEL_ENTITY top set_global_assignment -name ORIGINAL_QUARTUS_VERSION 19.1.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "02:12:09 SEPTEMBER 18, 2020" set_global_assignment -name LAST_QUARTUS_VERSION "19.1.0 Standard Edition" set_global_assignment -name NUM_PARALLEL_PROCESSORS 4 #============================================================================== source "./project_all_setings.qsf" #============================================================================== Как бы ни так (подумали разработчики Qu) - потому как последующее ... ... project_open -revision $rev $prj set_global_assignment -name PARTITION_NETLIST_TYPE EMPTY -section_id id_some_parttion ... project_close ... приводит к тому что добавленные строки с source удаляются! Получается что в qurtus_sh в этом случае команда project_close ничего не закрывает хотя файл qsf и обновляется после "закрытия". А команда project_open соответсвенно не читает реальное содержимое qsf (а зачем, раз не закрыто то вот же оно, в кэше лежит)? Может кто проверить, такое поведение повторяется? Удачи! Rob. -

Столкнулся с проблемой в "уважаемом" Квартусе: по исходному проекту нужно установить целый ворох констрейнов для проверки прототипа в FPGA, но сам тул просто оптимизирует большинство имён модулей. Как можно указать сохранить имена именно входных/выходных портов для конкретного модуля? Ну или не оптимизировать иерархически. Квартус 20.1, бесплатный. Соответственно LogicLock не предлагать. З.Ы. Также на более поздних этапах будет интересовать вопрос по фиксированию определённой логики во floorplan. Я хорошо знаю как это делается у Xilinx, но как и есть ли вообще такой функционал у Альтеры - вопрос.

-

Импорт типа данных из интерфейса

Perdaculus опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем привет. Пытаюсь передать параметризированную структуру между модулями и поскольку "parameter type" в Quartus 18.1 не работает, я хочу сделать это через интерфейс. Описываю его в отдельном файле, создаю инстанс в топ модуле, а во вложенном модуле пытаюсь вытащить из него тип данных. Выглядит это так: interface intf_WITHSTRUCT #(WIDTH=8); typedef struct packed{ logic val; logic [WIDTH-1:0] cnt; } st_INSIDE_INTF; st_INSIDE_INTF struct_inst; endinterface: intf_WITHSTRUCT module top (output logic [7:0] ocnt); intf_WITHSTRUCT #(.WIDTH(8)) interface_inst(); test i_test ( .clk(clk_125MHz), .rst(prb_rst), .blabla(interface_inst), .ocnt(ocnt) ); endmodule: top module test ( input clk, input rst, intf_WITHSTRUCT blabla, output logic [7:0] ocnt ); typedef blabla.st_INSIDE_INTF st_INSIDE_INTF_import; // Вытаскивю структуру st_INSIDE_INTF_import new_struct_inst; // Создаю инстанс always_ff@(posedge clk or posedge rst) if(rst) new_struct_inst <= '0; else new_struct_inst.cnt <= new_struct_inst.cnt + 1'b1; always_ff@(posedge clk or posedge rst) if(rst) ocnt <= '0; else ocnt <= new_struct_inst.cnt; endmodule: test В результате получаю ошибку: Error (10733): Verilog HDL error at test.sv(17): cnt is not declared under this prefix В чем может быть ошибка? Что странное, если во вложенном модуле я присваиваю структуре (которая в интерфейсе) значения, то ошибки не возникает. На мой взгляд не логичное поведение- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

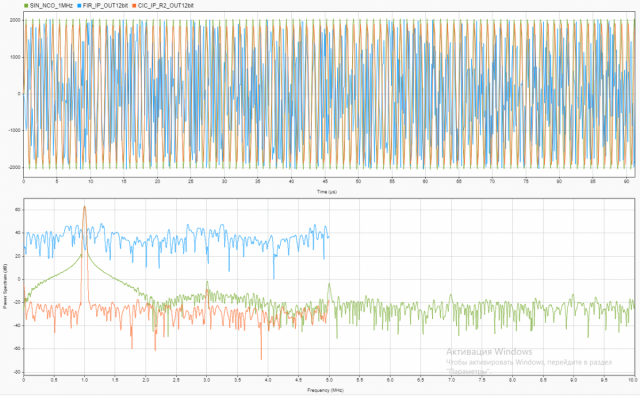

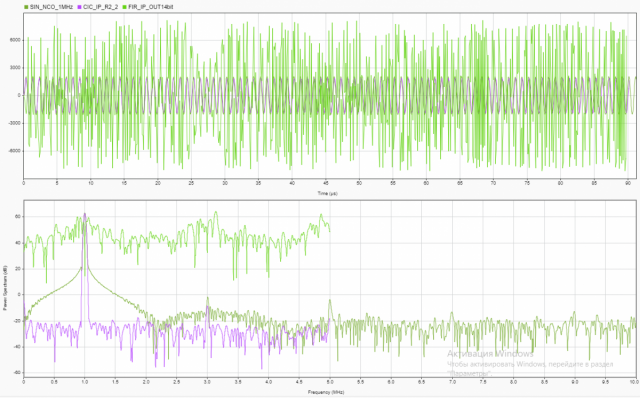

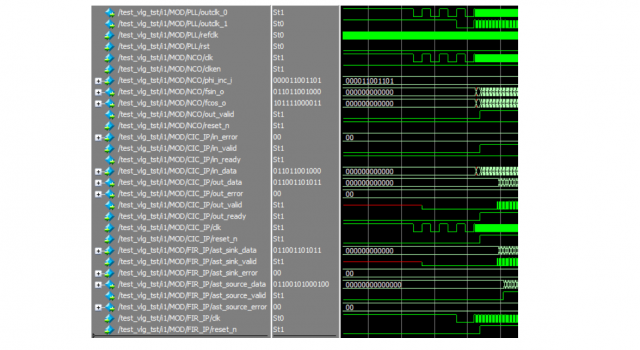

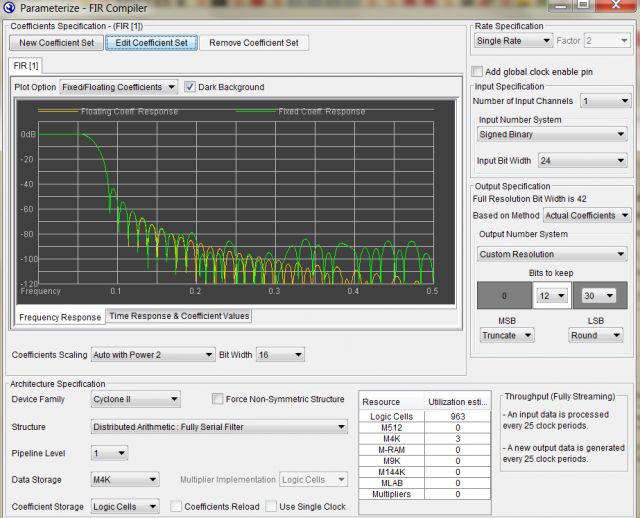

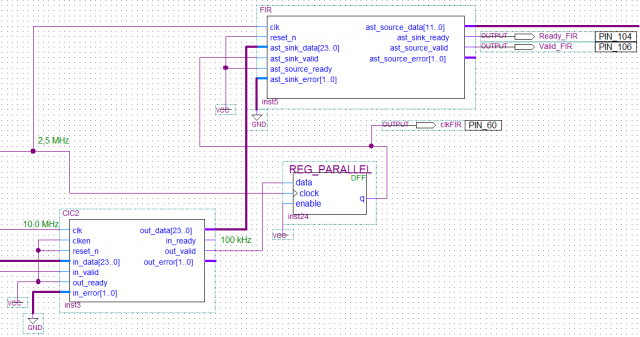

Всем доброго времени суток! Никогда ранее не обращался на форумы, но в данной ситуации ответа на свой вопрос в Сети не смог найти. Кратко введу в курс дела. Использую: 1) САПР для проектирования на ПЛИС - Quartus Prime Standart Edition 18.0.0 build 614 2) САПР для симуляции Verilog кода - ModelSim INTEL FPGA Starter Edition 10.5b Revision: 2016.10. (Данная версия поставляется вместе с Quartus на сайте https://fpgasoftware.intel.com/) 3) Для проверки результатов симуляции использую MATLAB 9.8 (2020a). В MATLAB на данный момент использую Signal Analyzer для просмотра спектра сигналов полученных в результате работы программного(-ых) модулей. Все программные модули пишу на Verilog (начал его изучать первым, на данный момент с VHDL знаком лишь отчасти). Опыт. Увлекся ПЛИС на 3 курсе университета. Специальных предметов по тематике ПЛИС на моем направлении не было, поэтому изучал все по видео/статьям/книгам/форумам. Увлечение переросло в желание написать диплом по ПЛИС. Таким образом, знаком с ПЛИС в районе 1,5 лет, из которых в учебное время не было слишком серьезных задач, а если и были, то решались они для моего уровня так, как мог их решить (костыли и тд). Вторым увлечением была ЦОС, в которой знания и опыт черпал из тех же источников, что и по тематике ПЛИС. Сейчас же появилась задача следующего плана. Занимаюсь QPSK демодуляцией. Разделим данный процесс на 3 этапа 1) Использование гетеродина для переноса на более низкую частоту. Тут все как обычно. Гетеродин и два умножителя для двух каналов (синфазного и квадратурного). 2) Децимация. Перед непосредственно реализацией дециматора окунулся в эту тематику. Знаком с статьей Hogenauer'a, а также с другой информацией на эту тему (ru.dsplib.org, dspguru.com), а также информацией с других сайтов. Имея начальное представление решил попробовать сделать, в итоге все получилось и CIC-фильтр работает так, как и ему положено. 3) Фильтрация. Компенсация искажений АЧХ после CIC-фильтра и последующая низкочастотная фильтрация. Так как в качестве САПР для проектирования на ПЛИС я использую Quartus, то было решено не использовать MATLAB без необходимости и решить задачу децимации и фильтрации с помощью встроенных в Quartus IP-ядер, а именно CIC и FIR II. В процессе работы с ядром проектирования CIC фильтра, есть возможность (ядро само сделает все необходимые файлы) сделать примерный вариант CIC фильтра, учитывая имеющиеся параметры. Одним из файлов является код MATLAB, который позволяет рассчитать коэффициенты компенсирующего FIR фильтра. В процессе выполнения скрипта задается количество и "битность" коэффициентов фильтра, а также - "FIR filter sample rate in Hz before decimation (80e6 as default): 20e6 (я указал 20 МГц)", что говорит нам о частоте дискретизации входного сигнала ПЕРЕД децимируюшим фильтром; - "FIR filter cutoff frequency in Hz (4e6 as default): 1.2 МГц". Частота среза компенсирующего FIR фильтра (в моем случае 1.2 МГц). После чего скрипт формирует текстовый файл с коэффициентами корректирующего FIR фильтра, которые загружаются позже в ядре FIR II. Исходя из коэффициентов ядро автоматически строит АЧХ,ФЧХ и ИХ получившегося фильтра. И вот мы дошли до самой сути моей проблемы. Все идет хорошо ровно до момента с компенсирующим FIR фильтром. По временным диаграммам в ModelSim (скриншот прикрепил) работа NCO, CIC и FIR фильтра прекрасна, то есть они работают и никто из них не простаивает и т.д. Ввиду того, что очень долго ковыряюсь с этой проблемой была сделана простая схема (скриншот из RTL Viewer из Quartus'а прикрепил), которая подает синусоиду с частотой 1 МГц и частотой дискретизации 20 МГц на вход CIC фильтра. Настройки CIC ядра: - Filter type - Decimator; - Number of Stages - 5; - Differential Delay - 1 cycles - Rate change factor - 2; - Input data width - 12 bit - Output Rounding Method - Hogenauer Pruning; - Output data width - 12 bit. Имея такие настройки CIC фильтр отлично отрабатывает и не искажает спектр в требуемом 1 МГц (скриншот прикрепил). Далее исходя из этих настроек был сделан скрипт, в котором задавал следующее: - Number of filter coefficients (31 as default): *оставил default значение*; - FIR filter sample rate in Hz before decimation (80e6 as default): 20e6; - FIR filter cutoff frequency in Hz (4e6 as default): 1.2e6 - Number of bits to represent the filter coefficients (16 as default): *оставил default значение*. После этого были сформированы коэффициенты и теперь надо настроить ядро FIR II. Настройки в нем задавал следующие: - Filter Type - Single Rate; - Interpolation / Decimation Factor - 1; - Clock Rate - 10 MHz; - Input Sample Rate (MSPS) - 10; - Coefficient Width - 16 bits; - Input Width - 12 bit; - Output Width - 14 bit; - Specifies whether to truncate or saturate the MSB - Truncation (аналогично для такого же параметра, но для LSB); - MSB Bits to Remove - 10; - LSB Bits to Remove - 9. Если не обрезать MSB и LSB, то на выходе ядро рекомендует ширину в 33 бита, что много и существенной разницы между 14 и 33 битами я не увидел (при увеличении доли MSB в сигнале растет мощность в дБ на спектре и все). Да, я пробовал 33 бита, однако желательно уходит от такой большой разрядности. Имея такие настройки, мы имеем следующую картину в спектроанализаторе Signal Analyzer (скриншот прикрепил). Как видно из рисунков спектр после FIR фильтра больше похож на шум, чем на что-то осмысленное. Промучавшись долго с этим ядром я решил, что необходимо попробовать сделать CIC и FIR в MATLAB и сравнить результат. При даже меньшей разрядности FIR фильтр выдал необходимый мне спектр и отработал так, как я и хотел (аналогично и CIC) (скриншот сравнения MATLAB'овского компенсирующего FIR и генерируемого ядром не смог прикрепить, однако и видно даже на первый взгляд, что разница имеется). Таким образом, вопрос. Знает ли кто-то в чем заключается проблема с FIR II ядром и почему (вроде бы нигде не ошибаясь) я получаю такой отрицательный результат? Заранее благодарю за уделенное время и оказанную помощь Что получилось загрузить

-

PCI Compiler в QSYS

Egorokrab опубликовал тема в Работаем с ПЛИС, области применения, выбор

Работаю с Cyclone III в Quartus II 13.0. Возможно ли создать Pci Compiler в QSYS? Смог добавить "вручную" через файл .qsys, но возникает ошибка "interface must have an associated reset". В настройках Pci Compiler создать reset нельзя. Так же возникает ошибка "altera_avalon_pci_compiler can not be generated in Qsys. Replace this component with a Qsys-compatible component." Если ли возможность как то обойти эту проблему или только работа в Sopc builder? -

походу нашел странный глюк использую связку Quartus 64bit 13.0.1 SP1+ Cyclone II EP2C8Q208C8 код - cделал вырезку, в ней глюк сохранятся // // переключение режимов reg [31:0] div10; reg CLK10; always @ (posedge CLK) begin if (div10 == 2400000) begin CLK10 <= 1; div10 <= 0; end else begin div10 <= div10+1; CLK10 <= 0; end end // reg [3:0] work_mode; // режимы работы комплекса // реакция на кнопки reg [3:0] step_key; always @ (posedge CLK10 ) begin if (~KEY[1]) // режимы begin if (step_key ==0) begin work_mode <= work_mode +1; CT [39:36]<= work_mode[3:0]; step_key <=1; end else begin step_key <=step_key+1; end end if (work_mode==0) begin DOTPOZ <=1; end else begin DOTPOZ <=6; end //CT [39:36] <= work_mode[3:0]; //CT [15:0] <= RD_CHECK[15:0]; //CT [35:16] <= addrramreadstream [19:0]; end // индикатор reg [3:0] DOTPOZ; // позиция точки 1234567890 reg [39:0] CT ; din40 dinamicind ( .CLK(CLK), .DIG(DIG), .SEG(SEG), .CT(CT), .POZ(DOTPOZ) ); проблема связана с переменной work_mode в данном коде, при старте она равна 0, однако, все проверки "if (work_mode==0)" считают что она равна 1 - те любой if обнаруживает значение больше на 1 чем там есть реально. на индикатор значение выводится верно. собака зарыта в месте присвоения CT [39:36]<= work_mode[3:0]; те если это в блоке вверху, то см эффект выше если перенести (раскоментировать/закоментировать) в блок внизу - 0 становится нолем итд итп блок динамического индикатора нужен для проявления глюка - те если его выключить, глюк пропадает. соответственно приложил код динамического индикатора. что там такого неправильного ? с чем связан данный глюк ? (на самом деле я ловил другой глюк и нашел этот случайно) как избежать подобного ? может что-то я делаю не так ? din40.v

-

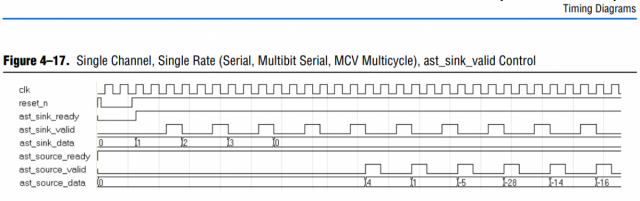

Добрый день уважаемые коллеги. В процессе разработки устройства (цифровой приёмник средневолнового диапазона) возникла проблема в конфигурации тайминга цифрового фильтра, при использовании соответствующей Мегафункции в Quartus 9.1. ПЛИС EP2C8Q208 (Cyclone II), КИХ фильтр 80 порядка, архитектура - Fully serial filter, single rate, входные данные - 24 бита (signed) с частотой 100 кГц. В FIR Compiler получаю 25 циклов CLK на один отсчёт. Согласно документа Fir Compiler User Guide устанавливаю CLK - 2,5 МГц, сигналы Reset и ast sink ready - лог."1", шина ast sink error - на земле, и ast sink valid сформировал через триггер - каждый 25-й отсчет CLK c длительностью в 1 период CLK (скважность 1/25 = 0,04) по сигналу valid от источника (CIC фильтр). Однако эти меры никак "не заводят" фильтр. При single cycle (вычисление отсчета за 1 CLK - c бешенным расходом LE) ast sink valid достаточно подтянуть к "1" и все работает... Может я что то неправильно понимаю в User Guide..? Заранее благодарен за любую помощь/пинок.

-

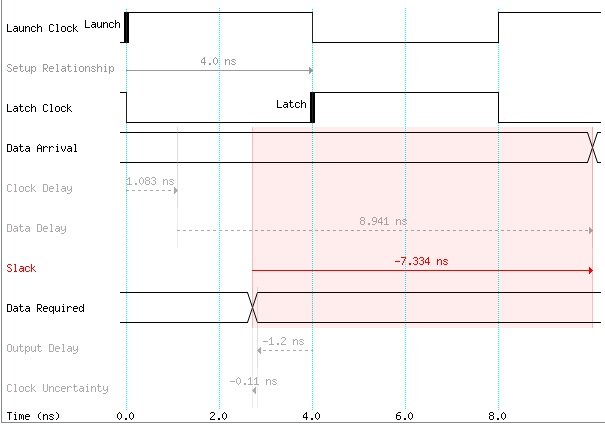

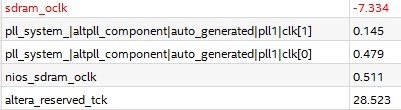

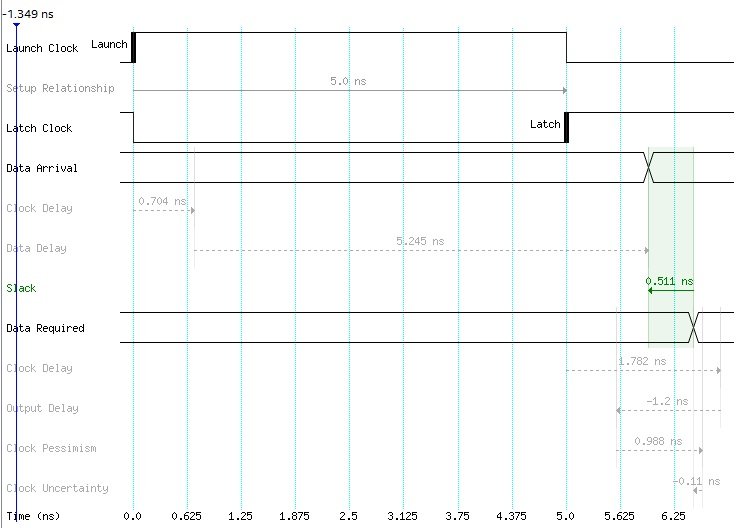

Здравствуйте, пишу свой первый проект на ПЛИС (verilog, max10), проект создаю в учебных целях. Создал систему в Qsys: nios, память(sdram), Jtag, и самописный компонент. Внутри самописного компонента, с просторов интернета контроллер памяти sdram(отдельно от памяти nios), счетчик и DCFIFO для передачи из счетчика на sdram. Nios запускает счетчик, тот в считает до оперделенного числа, и записывает в FIFO, оттуда контроллер sdram забирает данные и пишет в память. Nios и счетчик работают на 100Мгц, sdram и память на 125Мгц, FIFO двухклоковое на запись 100 Мгц на чтение 125 Мгц. На симуляции все работает отлично но в железе появляются проблемы констрейнов. В assigment поставил sdram выводам fast IO, клоки сделал Global Clock. Sdram для Nios работет timequest не ругается, а в моем компоненте постоянно ошибки памяти и я не могу понять почему такие большие слаки. Память микрон MT48LC16M16A2. На nios память микрон MT48LC4M32B2. Констрейны nios sdram Констрейны контроллера Общая картина: Клок Nios sdram Sdram внутри компонента. Не могу понять причину почему sdram внутри моего компонента так отличается от sdram используемого nios. Уже 2 недели бьюсь, может кто-то подскажет? Исходник компонента прилагаю. src.sv