Поиск

Показаны результаты для тегов 'asic'.

-

Обработка асинхронного сигнала

dips11 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

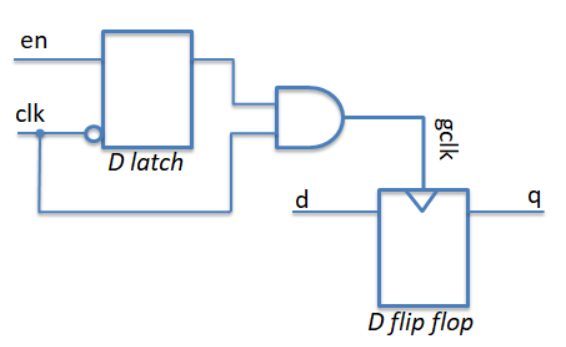

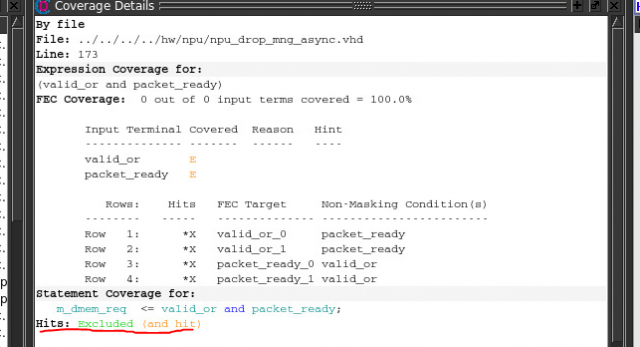

Доброго времени суток. В даташитах на микросхемы иногда встречается момент, где говорится примерно следующее: если сигнал ST придёт до 5 сигнала CLK, то микросхема перейдёт в такое-то состояние, а если после 5 и до 10 CLK то в такое-то. Причём не сказано за какое минимальное время до 5 CLK должен прийти сигнал ST. То есть сигнал полностью асинхронный. И мне интересно как может происходить обработка этого сигнала в микросхеме, ведь так как сигнал асинхронный нельзя просто использовать условие: always@(posedge CLK ) if(cnt==4 && !ST) reg0<=1; И возможности синхронизировать его нет. По сути задача может звучать как "надо определить какой сигнал приходит раньше ST или 5 CLK". Вот основные варианты, которые удалось найти. 1) Использовать сигнал ST как асинхронный сброс триггера. Если сигнал ST придет раньше то он сбросит триггер и не даст ему установиться, но как не достаток решения, если сначала придет 5 CLK то триггер установиться в 1, но потом все равно сброситься по сигналу ST и не сохранит свое состояние. always@(posedge CLK or posedge ST) if(ST) reg0<=0; else if(cnt==4) reg0<=1; 2) Использовать clock gating, то есть по сигналу ST отключить тактовую частоту. Если сигнал ST придет раньше 5 CLK то он заблокирует тактовую частоту для триггера, и он не установиться в 1, если позже пропустит. Где то встречал, что такое решение может вызвать метастабильное состояние. Это правда? Просто я вижу здесь либо наличие сигнала clk_gate для триггера либо его отсутствие. Элемент "И" ведь не должен выдавать шумов. assign clk_gate = CLK & !ST; always@(posedge clk_gate ) if(cnt==4) reg0<=1; Еще встречается реализация с защелкой. И говориться,что защелка добавляется для устранения glitch, так как такая схема будет пропускать сигнал ST только при низком значении CLK и его изменение не вызовет переключение выхода "И". Другие варианты являются производными от этих. Я был бы благодарен за советы, по тому как возможно правильно решить такую задачу. Возможно я вообще не там ищу. Спасибо.- 10 ответов

-

- verilog

- clock gating

-

(и ещё 2 )

C тегом:

-

Реверс-инжиниринг ячеек нанопорового секвенатора

genseq опубликовал тема в В помощь начинающему

Требуется помощь в реверс-инжиниринге ячеек нанопорового секвенатора MinION с целью использования отходов его работы (юзанных ячеек) в научных целях - для изучения различных ионных каналов в бислойных мембранах (программа минимум). Или для их регенерации и повторного использования. При этом сигналы с ячеек желательно считывать не при помощи секвенатора MinION, а с помощью доморощенного устройства (программа максимум). Плата ячейки содержит сенсорный чип (специализированный ASIC), информация с которого считывается FPGA (Xilinx Spartan-6) и передаётся на компьютер через Cypress FX3 по USB 3.0. Ещё там имеется парочка мелких чипов, с назначением которых нужно разбираться. Ячейки добыть не проблема, поскольку в России уже имеются десятки (или сотни) таких нанопоровых секвенаторов. Проблема в том, что решить эту проблему сейчас пытается только один человек (и это не я), который в одиночку может и не справиться. Или справиться, но не скоро. Поэтому буду очень рад, если такой реверс-инжиниринг заинтересует кого-нибудь из местных специалистов.- 120 ответов

-

- asic

- fpga xilinx

-

(и ещё 1 )

C тегом:

-

-

В связи с нестабильностью поставок ключевых ASIC-чипов и общим спадом спроса на ряд моделей компания Beneq (торговая марка Lumineq) вынуждена выводить из производства некоторые типоразмеры дисплеев. Подробности

-

FPGA разработчик. Полная занятость (Москва)

MaximBorzov опубликовал тема в Предлагаю работу

www.kraftway.ru Занимаемся разработкой материнских плат, видеокамер, коммутаторов и т.п. оборудования. Основной долгоиграющий продукт в работе: Микроконтроллер SSD диска. Есть первая рабочая версия. Вторая версия почти готова к отправке на фабрику. Планируем уже разработку третей версии. Там нужно будет принять участие в пересмотре архитектуры продукта. Сейчас под ARM, планируем RISC-V, но это не точно:-) Чем занимаемся: • Разработка конфигураций для FPGA Xilinx Zynq/UltraScale+; • Встраивание сторонних IP-блоков, разработка собственных IP-блоков; • Оптимизация проекта по быстродействию и занимаемым ресурсам; • Отладка интерфейсов взаимодействия FPGA и встроенного процессора ARM • Поддержка наследуемого кода, поиск и исправление в нем ошибок • Добавление в существующие модули новых функциональных возможностей; как пример задачи: разработка контроллера NVME. Пожелания по опыту/навыкам: Знание Verilog; Опыт написания тестбенчей с формированием отчетов; Опыт работы с Xilinx (ISE/Vivado) / Altera (Intel) (Quartus); Опыт работы с ПЛИС со встроенными процессорными ядрами (Xilinx Zynq, Intel Cyclone V SoC, Arria 10 SoC); Команда: 5 разработчиков ПЛИС. Verilog/SystemVerilog + смежные команды (математики, физдизайнеры). 2 верификатора. Redmine/Jira, git. Условия: Склоняемся больше к офисной работе. Но готовы обсудить и удалёнку/полуудалёнку) Место работы: м.Алексеевская, 5 мин.пешком от метро, 15 минут от платформы Рижская. График работы: Пятидневка. 8-часовой рабочий день. Обычно с 10 до 19. По деньгам: ориентир на 150+ т.р. в месяц. Всё в белую. Контакт: Борзов Максим Telegram https://t.me/Maksim_Borzov [email protected]-

- verilog

- systemverilog

-

(и ещё 2 )

C тегом:

-

Компания Syntacore, разработчик микропроцессорного IP, ищет сотрудника на позицию RTL Designer. Обязанности: Разработка и верификация сложных функциональных модулей для ASIC на Verilog/System Verilog. Требования: Опыт разработки и верификации RTL для ASIC от 3 лет; Отличное знание Verilog/System Verilog; Опыт использования RTL симулятора от 3 лет (any vendor); Знакомство с архитектурой современных процессоров, знание современных SoC интерфейсов (ACE, AXI); Уверенный пользователь Linux; Знание английского языка на уровне чтения технической документации и умения вести переписку на технические темы; Опыт работы с системами контроля версий. Мы предлагаем: Высокую оплату труда (по результатам собеседования); Оформление по ТК РФ; Интересную и перспективную работу, возможность быстрого профессионального и карьерного роста; Гибкий рабочий график; ДМС, оплачиваемый отпуск и больничный; Возможность публикаций и поездок на конференции. Контактная информация: [email protected] Дарья Также другие вакансии компании можно посмотреть на сайте https://spb.hh.ru/employer/2132324