-

Постов

122 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

pavlovconst стал победителем дня 15 марта 2023

pavlovconst имел наиболее популярный контент!

Репутация

2 ОбычныйИнформация о pavlovconst

- Сейчас Просмотр темы: Протокол взаимодействия с виртуальным кабелем Pango (PVC)

-

Звание

Частый гость

- День рождения 2 января

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Среда вам подсказывает, что в этих путях есть переход между тактовыми доменами. В тракт сигнала необходимо добавить синхронизаторы. Когда вы, как разработчик, будете уверены, что CDC сделаны корректно, можно будет написать констрейнт set_false_path. Если просто написать констрейнты, ничего не меняя в коде - вы только замаскируете проблему. Так лучше не делать )

-

SERDES на GOWIN

pavlovconst опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! У меня ПЛИС GW2AN-UV9XUG400C7/I6. Сделал проект с OSER10 + IDES10 + IODELAY. Используются дифференциальные буфера True LVDS с внешним согласованием. При скоростях 100Mbps (на линии) и ниже проект работает, а на 1000Mbps - гарантированно НЕ работает. Периодически с сердеса поступают последовательности в 10 и более нулей или единиц, что в принципе невозможно при использовании 8b10b кодирования, как у меня. Поделитесь пожста опытом, кто-то вообще запускал ПЛИС этой серии на скоростях под 1Gbps. Они в принципе могут в таком режиме работать? А если кто-то запускал - требовались ли для этого жесткие констрейны типа LOC-ов или прибитых гвоздями тактовых линий? От GOWIN конкретных рекомендаций я не видел, в логах тоже ничего страшного не вижу. Но по опыту реализации подобных проектов на Cyclone V я помню, что там требований было много (например использовать строго определенную PLL, ближайшую к IO банку, и специализированный тактовый буфер) -

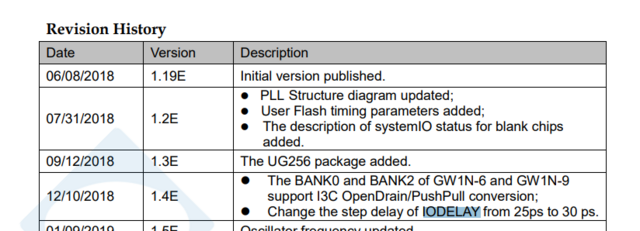

Привет! Я немного опоздал, но все же дополню 😃 В даташите на GW1N нашел такую запись Видимо, 25ps было задокументировано изначально, затем документация была поправлена, а модели - нет. Почему написали новые значения? Я предположу, потому что задержки IODELAY некалиброваннные (в отличие от Xilinx-а) и в разных PVT условиях могут отличаться. Возможно, перестраховались и вписали самый плохой случай...

-

pavlovconst подписался на IdiotBox

-

pavlovconst подписался на Универсальная посылка по UART. и ПЛИС Gowin Semiconductor

-

Первый вариант - перед UART_TX поставить FIFO для того чтобы временно хранить отправляемые данные. А для записи в FIFO написать арбитр, который будет собирать с N модулей данные. Поскольку N модулей могут захотеть писать в UART одновременно - можно предложить второй вариант - в каждом из N модулей по небольшому FIFO, а затем самописный модуль-арбитр, который последовательно или по приоритету забирает данные из FIFOшек и скармливает блоку UART_TX Основная идея - UART_TX нужно переделать, чтобы он получал данные побайтно, потоком

-

Не выдумывайте велосипед. Всё уже сделано за вас, в стандартном IP-ядре от Xilinx. Называется IBERT Указываете необходимые лейны для проверки, генерируете example design, зашиваете. Прямо в интерфейсе Vivado будет показано количество ошибок, BER, и даже глазковая диаграмма (если нужно)

-

Terasic DE10-Nano с ПЛИС Intel Cyclone V SoC

pavlovconst ответил pavlovconst тема в Продам

в продаже! -

@1891ВМ12Я Может показаться, что все идеи на поверхности - читай мануал, настраивай трансиверы - и получи синхронную работу устройств. Но, в действительности, GTH-ы и телекоммуникационное оптическое оборудование никогда не создавалось для синхронизации времени. В типичной задаче нужно лишь достоверно передать поток данных, а с каким фазовым набегом он будет получен - неважно. Производители не гарантируют характеристики, на которые такая система будет опираться. Весь путь проб и ошибок придется пройти самому. Поэтому, отладка такой системы может легко стоить десяток-другой человеко-лет.

-

Terasic DE10-Nano с ПЛИС Intel Cyclone V SoC

pavlovconst ответил pavlovconst тема в Продам

Цена 24 999р + доставка -

Terasic DE10-Nano с ПЛИС Intel Cyclone V SoC

pavlovconst опубликовал тема в Продам

Terasic DE10-Nano вот такая ПЛИС FPGA Intel Altera Cyclone V SoC Система на кристалле с аппаратными ARM ядрами Встроенный программатор отладчик USB Blaster Arduino shield разъемы В комплекте - отладочная плата с дополнительным радиатором - оригинальный блок питания Плата в работе не была. Включалась пару раз для проверки. Цена 29 999 р., Санкт-Петербург -

Говорят http://course.ece.cmu.edu/~ece545/F10/resources/Virtex5/xapp918.pdf, что в ISE есть инкрементальная компиляция. Она позволит вам зафиксировать разводку "ядра" проекта. Но проблема подсовывания различных ucf остается. Тут подсказать не могу, я мало работал с ISE.

-

Конечно, ваша задача решается с помощью скриптов. Компиляцию в ISE можно запускать из командной строки. Например, вот - https://github.com/duskwuff/Xilinx-ISE-Makefile Значит, берем любой скриптовый язык, и пишем "запустить ISE 20 раз в параллель". Я бы делал не один проект с разными настройками, а создал бы 20 проектов, ссылающихся на одни и те же файлы исходников.

-

Да, но только пытался 🙂. Без старой Вивады ничего не получится

-

Попробовал собрать у себя на машине. Падает с ошибкой ERROR: This script was generated using Vivado <2015.4> and is being run in <2021.2> of Vivado. Please run the script in Vivado <2015.4> then open the design in Vivado <2021.2>. Upgrade the design by running "Tools => Report => Report IP Status...", then run write_bd_tcl to create an updated script. Придется вам еще и древнюю Виваду ставить 😬

-

Надо написать ./build.sh prj v1 prj - выбор имени проета Vivado v1 - версия. Писать нужно именно так, потому что в инструкции автор их так называет Что возвращает команда? Команда должна запустить Виваду, в логе должна быть подробная информация, что происходит

-

Открываете папку проета. Прямо в адресной строке проводника, там где обычно путь к папке - набираете mintty[Enter]. Откроется командная строка линукс. Набираете команду ./build.sh <Project Name> <Version>, подставляя аргументы в соответствии с инструкцией...