Поиск

Показаны результаты для тегов 'questasim'.

-

Здравствуйте, коллеги Возникла проблема при миграции с QuestaSim в Xcelium Есть следующий код: T temp_numb; //... // Convert to actual number if (type(temp_numb) == type(int)) temp_numb = temp_numb_str.atoi(); else if(type(temp_numb) == type(int unsigned)) temp_numb = T'(temp_numb_str.atoi()); else if(type(temp_numb) == type(byte)) temp_numb = byte'(temp_numb_str.atoi()); else if(type(temp_numb) == type(real)) temp_numb = temp_numb_str.atoreal(); else if(type(temp_numb) == type(shortreal)) temp_numb = shortreal'(temp_numb_str.atoreal()); else `uvm_fatal("FILE READ", "Unsupported type of parameter") Здесь происходит парсинг входной строки в один из встроенных SV типов. Соль в том, что подобное сравнение типов спокойно компилируется в Questasim, а вот Xcelium при компиляции выдаёт ошибку. Пока пришлось закомментить данный блок и оставить конвертацию в один тип, но это костыль, а костыли - зло. Есть ли сравнение типов в Xcelium?

- 5 ответов

-

- systemverilog

- questasim

-

(и ещё 1 )

C тегом:

-

Questasim 10.7c Новшество - не воспринимает в файле modelsim.ini параметр VoptFlow = 0. Не воспринимает в *.bat и *.opt файлах параметр -novopt. При VoptFlow = 0 или наличии -novopt прога вылетает с ошибкой. Обьяснение от Mentor - эти параметры вредны, бла-бла-бла, короче сами прочитаете сообщение, которое выдаст прога при попытке их использовать. Пытаюсь скомпилировать библиотеки стандартным батником %Xilinx%\bin\nt64\compxlib -s questasim -64bit -arch all -lib all -l all -dir %MODEL_TECH%\..\Xilinx\ -p %MODEL_TECH%\ -log compxlib.log -w Переменные окружения у меня MODEL_TECH = путь до \win64, например C:\MentorGraphics\questasim64_10.7c\win64 XILINX = путь до \ISE, например C:\Xilinx\14.7\ISE_DS\ISE Ожидаю, что скомпилированные библиотеки будут в папке questasim64_10.7c\Xilinx\, как я прописал в батнике. Хрен там! Библиотеки "emty". Но папка Xilinx появилась с каким-то содержимым и подпапками. Лезу в подпапки этой папки ...\Xilinx\, смотрю файлы *.log. Вижу там **Error (suppressible): (vlog-12110) All optimizations are disabled because the -novopt option is in effect. Смотрю в папке Xilinx и в подпапках файлы *.cmd, в каждом файле есть строки типа C:\MentorGraphics\questasim64_10.7c\win64\/vlog -source -novopt -64 -work unisims_ver -f Хрен знает откуда там взялись эти -novopt. Короче - во всех файлах *.cmd из папки и подпапок questasim64_10.7c\Xilinx\ я уничтожил параметр -novopt. Потом запустил батник questasim64_10.7c\Xilinx\.cxl.questasim.nt64.cmd и всё хорошо! Библиотеки скомпилировались! Дальше я отключил оптимизацию, типа как раньше VoptFlow = 0. В файле modelsim.ini в секции [vopt] я прописал два параметра [vopt] Coverage = sbceft CoverOpt = 1 Наступило счастье.

-

-

questa+vivado

lennox опубликовал тема в Среды разработки - обсуждаем САПРы

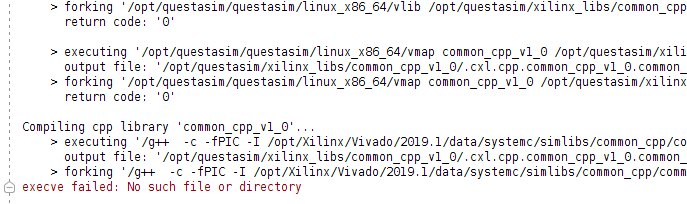

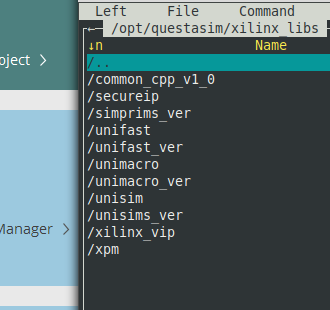

Здравсвуйте. Пытаюсь скомпилировать библиотеки для квэсты. Возникает ошибка с библиотекой common_cpp_v1_0 (не видел ее раньше в предыдущих версиях). Компиляция прекращается. вивада успевает скомпилить совсем мало... нету либ для ip ядер... Linux. Vivado 2019.1. Questasim_10.7c Подскажите, пожалуйста, как побороть это? Или как заставить виваду продолжать компилировать дальше (исключить конкретно эту либу)? -спасибо- 3 ответа

-

- compile_simlib

- questasim

-

(и ещё 1 )

C тегом:

-

Покрытие кода для FPGA

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Добра всем! Поискал в форуме в разных ветках, но сразу не нашёл ответа на такой вопрос: поставлена задача для наших проектов доказать соответствие оных директивам DO-254 и иже с ними. Проекты написаны как на VHDL и Verilog (SV), так и в схематике. Причём ПЛИС Actel и Altera. Вопрос: откуда нам, первый раз столкнувшимся со словами Code Coverage, начать сей нелёгкий и тернистый путь? Всё комментарии, а тем паче, ссылки, книги и прочее, приветствуются. Оптимально Mentor (ModelSim и QuestaSim), но и Aldec пойдёт, если он умеет это лучше.- 16 ответов

-

- mentor grapics

- modelsim

-

(и ещё 3 )

C тегом:

-

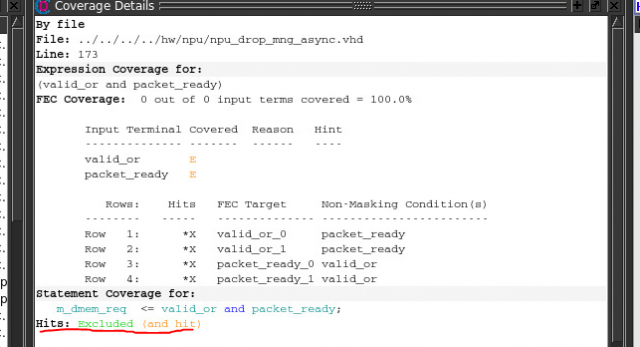

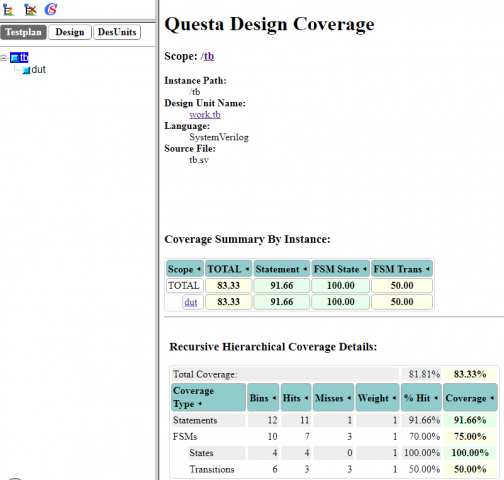

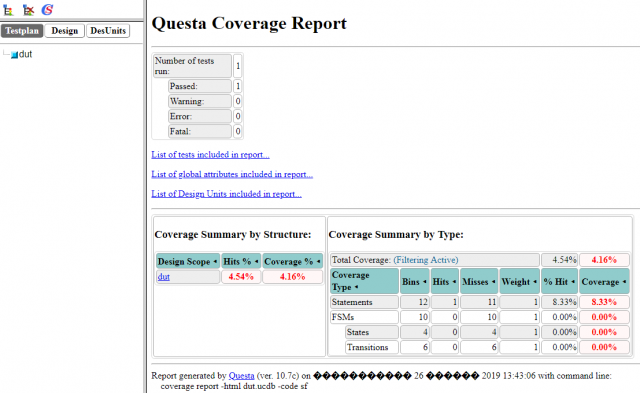

Всем добра! Столкнулся с такой проблемой: есть dut, например такого вида (dut.sv): module dut ( input logic clk, input logic res, input logic data, input logic ena, output logic q, output logic w ); always_ff @(posedge clk) if (res) q <= 1'b0; else if (ena) q <= data; else q <= q; enum {DUT_IDLE, DUT_START, DUT_PROC, DUT_END} dut_state; always_ff @(posedge clk) if (res) dut_state <= DUT_IDLE; else case (dut_state) DUT_IDLE : dut_state <= ena ? DUT_START : DUT_IDLE; DUT_START : dut_state <= DUT_PROC; DUT_PROC : dut_state <= DUT_END; DUT_END : dut_state <= DUT_END; default : dut_state <= DUT_IDLE; endcase assign w = dut_state == DUT_PROC; endmodule : dut и есть узурпирующий его test bench вида, например, такого (tb.sv): `timescale 1ns/100ps module tb; logic clk; logic res; logic data; logic ena_tb; logic ena; logic q; logic w; dut dut(.*); initial begin clk = 0; forever #10ns clk = !clk; end; initial begin res = 0; #20ns res = 1; #20ns res = 0; end initial begin data = 0; forever #30ns data = !data; end; initial begin ena_tb = 0; #70ns ena_tb = 1; #80ns ena_tb = 0; end enum {TB_IDLE, TB_START, TB_PROC, TB_END} tb_state; always_ff @(posedge clk) if (res) tb_state <= TB_IDLE; else case (tb_state) TB_IDLE : tb_state <= TB_START; TB_START : tb_state <= ena_tb ? TB_PROC : TB_START; TB_PROC : tb_state <= !ena_tb ? TB_END : TB_PROC; TB_END : tb_state <= TB_END; default : tb_state <= TB_IDLE; endcase assign ena = tb_state == TB_PROC; endmodule : tb есть tcl-скрипт (proc_tb.tcl), запускающийся в Mentore (ModesSim или QuestaSim) обрабатывающий упомянутые выше tb и dut вида # create library if [file exists work] { vdel -all } vlib work vlog -O0 +fcover +acc *.sv set top_module tb # set top_module dut set top_module_opt $top_module append top_module_opt "_opt" set coverage_letters_string "sf" # optimize design vopt +cover=$coverage_letters_string $top_module -o $top_module_opt vsim -cvgperinstance -c -coverage work.$top_module_opt # go run 200ns # make coverage report if {$top_module == "tb"} { coverage save $top_module.ucdb -instance /tb/dut coverage exclude -src tb.sv } else { coverage save $top_module.ucdb } coverage report -html $top_module.ucdb -code $coverage_letters_string # config instance window view instance source ColumnConfig_instance.tcl который, несмотря на наличии в нём строк вида coverage save $top_module.ucdb -instance /tb/dut coverage exclude -src tb.sv которые мы выполняем при моделировании с взятием в качестве модуля верхнего уровня test bench-а рисует на главной странице html отчёта картинку вида Картинка хорошая, но нам не нужен сам tb ни в дереве, ни в каких других таблицах! Нужен dut и всё, что ниже! Т.е. картина, которая нужна, получается при замене (в proc_tb.tcl) строки set top_module tb на set top_module dut что даёт Т.е. всё дерево слева и всё, относящееся к нему справа, стало, как доктор прописал, но покрытие теперь в нём стало минимальным! Test bench не сработал? ЧЯДНТ? Просьба ткнуть носом ) Как обычно, прикладываю проект. test_coverage_el.zip

-

- mentor graphics

- modelsim

- (и ещё 3 )