-

Постов

46 -

Зарегистрирован

-

Посещение

Репутация

2 ОбычныйИнформация о srf55

-

Звание

Участник

Посетители профиля

614 просмотра профиля

-

Извините, за мою безграмотность ( Здесь имелась ввиду не амплитуда, а достоверные мгновенные значения напряжений.

-

Не понял эту фразу. Вы говорите, что тип сигнала влияет на точность измерения амплитуды в отдельных отсчетах?

-

К сожалению, там выходные файлы не в формате LTSpice(

-

Спасибо) Получается, что максимально 62.5 kSPS на один канал. Из этого следует, что рабочая полоса может быть только 0..32,25 МГц (половина частоты дискретизации). Такая полоса тоже устроит. Смысл всей моей затеи - сделать входной фильтр для AD7682, использовать максимально доступный диапазон рабочей частоты, получив при этом минимальную неоднородность АЧХ в этом диапазоне рабочей частоты. Остановлюсь пока на AD7682, т.к он у меня есть. Хочу разобраться вообще в подходах к разработке аналоговых фильтров в, рассчитать в Filter Solutions, промоделировать в LTSpice (Transient, AC Analysis, Noise) и проверить в железе. Хочу получать значения амплитуды, без дофильтровываний в цифре. Зона Найквиста одна. При этом получить фильтр с минимальной неоднородностью АЧХ в рабочей полосе (для точности изменений)

-

По тексту не нашел конкретных указаний на это и начал считать от обратного: 50 МГц(частота SCK) / 4 канала / 16 бит (т.к SAR) = 781,250 kSpS . Понятное дело, что между сэмплами какая-то пауза должна быть. И поэтому решил, что 250kSpS на каждый канал вполне реально

-

Спасибо! Но разве активные фильтры не более устойчивы к изменениям R нагрузки и C нагрузки? По тексту из даташита на AD7682: Rin около 2.2кОм, Сin около 27pF А чем его тогда заменить, если фильтра Чебышева и Бесселя имеют более неоднородную АЧХ в рабочей полосе?

-

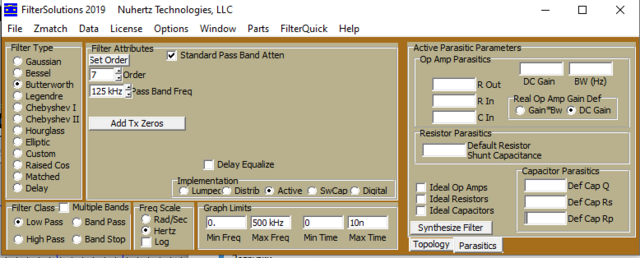

Спасибо за ориентировочные паразитные параметры. Пока что их буду использовать Спасибо! Изменил параметры Pass Band = 105 кГц, Stop Band Frequency = 150 кГц. 40 дБ подавления пока оставил. Но уже становится понятно, что с такими параметрами вменяемого порядка фильтра не получается. В моей задаче измерять фазу не требуется. У меня все четыре канала используются. В первом посте мне надо было написать, что речь идет в т.ч про килосэмплы. Полистал даташит на АЦП. Не нашел где сказано, что 250ксэмплов это не на каждый канал из четырех.

-

Здравствуйте! Появилась задача сделать антиалайзинговый фильтр (ФНЧ). Этот ФНЧ будет стоять перед входом в SAR АЦП (частота дискретизации 250 кГц) AD7682. Рабочая полоса входного сигнала: 0..100 кГц. Амплитуда входного сигнала: ±1 В (размах 2 В) Сам фильтр решил делать с такими параметрами (Поправьте, пожалуйста, если не прав. Возможно вообще можно сделать всё проще или сложнее 🙂 ) Активный фильтр Баттерворта. Предполагаю, что так можно будет достичь минимальной неоднородности АЧХ (около 0 dB) в области рабочей полосы). Все активные элементы: ОУ AD8655 Топология фильтра: GIC Biquad (интересно, как это по-русски называется). Если правильно прочитал, то фильтр с такой топологией будет наиболее устойчивым к изменениям номиналов резисторов/конденсаторов. Pass Band Frequency (частота полосы пропускания) = 125 кГц (взял такую, чтобы неоднородность АЧХ в рабочей полосе была минимальной, отодвинул частоту среза от рабочей полосы) Stop Band Frequency (частота полосы заграждения) = 250 кГц Stop Band Attenuation (ослабление в полосе заграждения) = 40 dB Усиление фильтра 1.5 раза. Выходной сигнал по амплитуде 0..3В Для расчета необходимо указать паразитные параметры (Parasitics): ОУ, конденсаторов, резисторов. Но где взять некоторые из параметров(как рассчитать), в даташитах они не приведены? 1) R Out (ОУ) 2) R In (ОУ) 3) C In (ОУ) 4) Default Resistor Shunt Capitance (резистор) 5) Def Cap Q (конденсатор) 6) Def Cap Rs (конденсатор) 7) Def Cap Rp (конденсатор) Конденсаторы и резисторы - Murata и Yageo Скорее всего еще ручная пайка будет вносить дополнительную паразитную емкость, как и ее учесть? Скриншот Nuhertz FilterSolution: P.S: Планирую еще потом проверить рассчитанный фильтр в LTSpice

-

Согласование уровней сигналов

srf55 ответил Vadim_nsk тема в Вопросы аналоговой техники

Здравствуйте! Подскажите, пожалуйста, какие-нибудь аналоги трансформатора ZMPT101B, желательно в еще более миниатюрном корпусе (по высоте) -

Спасибо всем за помощь! Вот что получилось: ring_buffer.v ring_buffer_pipe.v ring_buffer_tb.sv Исправил ошибку, last выставлялся несвоевременно, на такт раньше, чем нужно. Через строковый параметр Добавил возможность выбирать тип используемой памяти (параметр USE_BLOCK_RAM). Исправил, теперь в этом месте происходит сравнение с константой 😀 Разве? Где сигнал ready? А вот когда он появится, тогда Смотрел стандарт AMBA AXI-Stream и не нашел, что ready (TREADY) - это обязательный сигнал (но мог упустить, и где-то об этом говорится). В этом конкретном случае, на мой взгляд, сигнал TREADY не нужен.

-

Спасибо! Основываясь на мысли Arlleex сделал ring.v (прекратил запрещать запись во время выдачи данных) Добавил дополнительные регистры (ring_pipe.v). Но счетчики, на более мелкие (как посоветовал Maverick_) пока что дробить не стал. Т.к Fmax возрос до 370 МГц и этого хватает. Потом ради интереса может займусь. сделал ring_tb.sv - для проверки того, что модули работают идентично

-

Сейчас подумал, что можно обеспечить, чтобы адрес write_ptr был на 1 больше, чем адрес read_ptr. Тогда никаких коллизий не будет происходить. Спасибо! Только тогда придется сделать еще один счетчик(считать до значения глубины FIFO), т.к не получится останавливать выдачу данных на условии: (read_ptr == write_ptr - 1)

-

Реализация кольцевого буфера

srf55 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

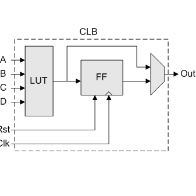

Добрый день! Написал модуль кольцевого буфера, планирую использовать для временного хранения отсчетов, захваченных с АЦП. Модуль служит для того, чтобы сохранять предыдущие N-отсчетов с АЦП. Суть работы модуля такая: 1) Данные пишутся в буфер непрерывно, по кругу 2) при возникновении разового импульса на входе catch все данные выдаются на выход (интерфейс AXI-Stream) 3) В момент выдачи данных, запрещается запись в буфер Вроде хорошо работает на частотах до 250 МГц (Virtex-6). Но хотелось бы оптимизировать его, чтобы он работать на чуть большей частоте (300МГц). Может кто-нибудь подскажет, как. Еще хотелось бы сделать модуль более параметризируемым. Чтобы можно было выбирать тип используемой памяти (блочная или распределенная) Код модуля: `timescale 1ns/1ps module ring_buffer #( parameter DATA_WIDTH = 8, parameter BUFFER_DEPTH = 32768, parameter USE_BLOCK_RAM = 1 ) ( input wire clk, // Тактовый сигнал input wire reset, // Сигнал сброса input wire [DATA_WIDTH-1:0] data_in, // Входные данные Native интерфейса input wire catch, // Флаг начала выдачи данных output wire [DATA_WIDTH-1:0] data_out, // Выходные данные output wire valid_out, // Сигнал валидности выходных данных output wire last_out // Сигнал последнего отсчета выходных данных ); reg [DATA_WIDTH-1:0] buffer [0:BUFFER_DEPTH-1]; // Кольцевой буфер предыдущих отсчетов reg [$clog2(BUFFER_DEPTH)-1:0] read_ptr = 0; // Указатель на чтение reg [$clog2(BUFFER_DEPTH)-1:0] write_ptr = 0; // Указатель на запись reg transfer_active = 1'b0; // Флаг активной передачи данных always @(posedge clk or posedge reset) begin if (reset) begin // Сброс в начальное состояние при срабатывании сигнала сброса //buffer <= 0; read_ptr <= 0; write_ptr <= 0; transfer_active <= 0; end else begin // Запись в буфер независимо от флага if (!transfer_active) buffer[write_ptr] <= data_in; if (!transfer_active) write_ptr <= write_ptr + 1; // Установка флага активной передачи данных if (catch) begin transfer_active <= 1; end else if (last_out) begin transfer_active <= 0; end if (transfer_active) begin read_ptr <= read_ptr + 1; end else begin if (catch) read_ptr <= write_ptr + 1; end end end // Выходные данные assign data_out = buffer[read_ptr]; assign valid_out = transfer_active; assign last_out = (read_ptr == write_ptr - 1) ? 1'b1 : 1'b0; // Сигнал последнего отсчета при чтении последнего отсчета из буфера endmodule Тестбенч: `timescale 1ns/1ps module ring_tb (); logic clk = '0; // Тактовый сигнал logic reset = '0; // Сигнал сброса logic [7:0] data_in = '0; // Входные данные Native интерфейса logic catch = '0; // Флаг начала выдачи данных logic [7:0] data_out; // Выходные данные logic valid_out; // Сигнал валидности выходных данных logic last_out; // Сигнал последнего отсчета выходных данных ring #( .DATA_WIDTH (8), .BUFFER_DEPTH (32768), .USE_BLOCK_RAM (1) ) dut ( .clk (clk), // Тактовый сигнал .reset (reset), // Сигнал сброса .data_in (data_in), // Входные данные Native интерфейса .catch (catch), // Флаг начала выдачи данных .data_out (data_out), // Выходные данные .valid_out (valid_out), // Сигнал валидности выходных данных .last_out (last_out) // Сигнал последнего отсчета выходных данных ); initial begin clk = 0; forever clk = #5 ~clk; end initial begin reset = 1; #100; reset = 0; #100; end always_ff @(posedge clk) begin : proc_data_in data_in <= data_in + 1'b1; end initial begin catch = '0; #500000; catch = '1; #10; catch = '0; #500000; catch = '1; #10; catch = '0; end endmodule -

Vitis 2023.2

srf55 ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Нашел для монтирования архивов более удобный инструмент: ratarmount Поддерживает многопоточность, работает быстрее -

Ага, так я себе это и представлял 🙂 Только не умею ни bat, ни sh. 😁 Поэтому надеюсь, что кто-нибудь подобное уже реализовал. Думаю, что это много бы кому пригодилось