Koctix

Участник-

Постов

12 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйПосетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Да, сейчас глянул, наверное поищу готовый 🙂 Я бы хотел свой написать, но, к сожалению, времени маловато, слишком много потратил на выяснение причины проблемы...

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

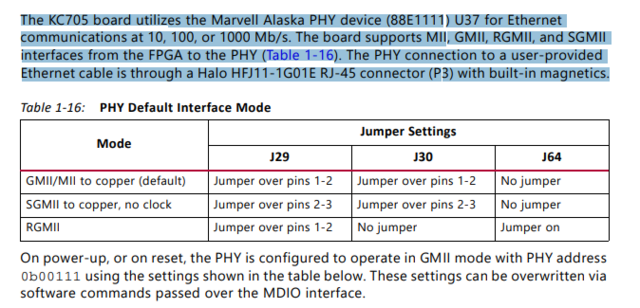

Спасибо за ответы. Strap пины я так понимаю выведены на плату KC705, там это задается джамперами. Или вы не об этом? Постараюсь тогда написать модуль для конфигурации по mdio, все равно вариантов у меня не остается

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

Koctix подписался на Ethernet на плате KC705

-

Ethernet на плате KC705

Koctix опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет, пытаюсь организовать Ethernet на плате KC705 с помощью интерфейса MII, на ней стоит PHY marvel 88E1111. Приемник сделать уже получилось, работает нормально, я принимаю пакеты из сети, пишу их в FIFO и оттуда по UART передаю на компьютер, и могу посмотреть, как выглядит пакет начиная от преамбулы и заканчивая CRC. Но вот передатчик сделать так и не получилось, светодиод при отправке пакета моргает (он управляется самим PHY), но никакого пакета Wireshark не видит, кроме того, у меня есть вторая плата KC705 и при соединении их между собой вторая плата также не видит никакого пакета, и сам PHY не моргает светодиодом, указывающим на прием какого-то пакета из сети. Соединяю я плату с пк или с другой платой через свич, который работает на 100 мбит/сек, так как никакую конфигурацию для PHY не задаю (кроме конфигурации джамперами на плате) и она при соединении выбирает скорость максимальную возможную, но я пытался сделать хотя бы MII, прежде чем переходить на GMII. Как решить проблему не знаю, может все-таки надо что-то конфигурировать прежде, чем пытаться отправить пакет, MDIO я вообще не подключаю к PHY, но не понятно зачем тогда микросхема моргает светодиодом при отправке. Пытался также принимаемый пакет сразу отправить назад без каких-либо изменений, Wireshark все равно увидел только один пакет (отправленный с компьютера). Может кто-то сталкивался с таким или может подсказать в какую сторону копать. Прилагаю модуль передатчика и модуль с описанным тестовым пакетом. Заранее спасибо! MII_tx.zip- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

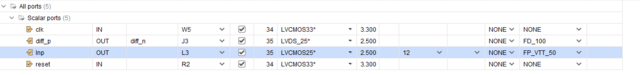

Да! Было упоминание, я не заметил, что это связано с пинами. Сообщение было следующие "[Vivado 12-1411] Cannot set LOC property of ports, the negative port (N-side) 'diff_n' of a differential pair cannot be placed on a positive package pin 'J3' (IOBM). ["D:/Work/SpaceWire/SpW_most_castom/RTL/exper_for_ISERDESE2/exper_for_ISERDESE2.srcs/constrs_2/new/LVDS_xds.xdc":7]", по всей видимости положительный сигнал зацепился на отрицательный и наоборот. Это странно потому что я делал с помощью средств vivado, а он мне получается создал неправильные констреины: set_property PACKAGE_PIN J3 [get_ports diff_n] set_property PACKAGE_PIN K3 [get_ports diff_p] set_property IOSTANDARD LVDS_25 [get_ports diff_n] set_property IOSTANDARD LVDS_25 [get_ports diff_p] было так, хотя J3 это положительный. Исправил: set_property PACKAGE_PIN J3 [get_ports diff_p] set_property PACKAGE_PIN K3 [get_ports diff_n] set_property IOSTANDARD LVDS_25 [get_ports diff_n] set_property IOSTANDARD LVDS_25 [get_ports diff_p] Все заработало, большое спасибо за помощь, в следующий раз буду внимательнее к варнингам 🙂 Нет вы, наверное, что-то проглядели, все синтезируется в нормальную схему)

-

Да стартует, в целом работает с другими модулями и в этом, если заметили, есть сигнал Inp, он работает как положено, на осциле померил

-

-

LVDS на плис XILINX

Koctix опубликовал тема в Работаем с ПЛИС, области применения, выбор

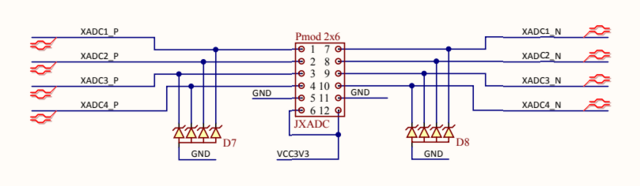

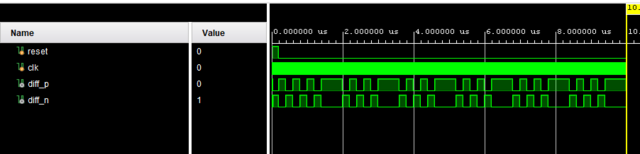

В проекте есть необходимость использовать LVDS, в документации на Xilinx 7ой серии UG953 нашел OBUFDS с примером использования, и попробовал подключить только его для проверки работоспособности, получился следующий код: module LVDS( input logic reset, input logic clk, output logic diff_p, output logic diff_n, output logic Inp ); logic Inp_inv; logic [7:0] data=8'b11010101; logic [3:0] i; logic [5:0] div; OBUFDS #( .IOSTANDARD("DEFAULT"), .SLEW("SLOW") ) OBUFDS_inst ( .O(diff_p), .OB(diff_n), .I(Inp) ); always_ff @(posedge clk or posedge reset)begin if(reset)begin Inp <= '0; Inp_inv <= '1; i <= '0; div <= '0; end else begin Inp <= data; Inp_inv <= !data; if(div==9)begin if(i<7) i <= i+1; else i<=0; div <= 0; end else div <= div+1; end end В симуляциях все работает: Но когда загрузил на плату, то никаких сигналов с выхода не увидел. Плату использую Basys 3 от digilent, по схеме нашел куда подключаются диф. пары (использовать решил выводы микросхемы J3 и K3 они соответсвуют цепям XADC1_P и XADC1_N). Скрин со схематика: Возможно что-то не так подключил или есть какие-то еще нюансы, может сможет кто помочь. Заранее спасибо -

Спасибо за ответ! Я попробовал запустить ваш проект, до 100Мбит/сек на прием работает (возможно можно увеличить за счет поднятия частоты тактирования, но я оставил все так как у вас описано), мой на 200, хотя мой криво написан в части машины состояний и поэтому у меня есть проблемы при введении ошибок в канал (ваш же работает в этой части без проблем абсолютно), да и в целом ваш код професиональнее, постараюсь почерпнуть что-то у вас, благодарю. По-поводу одновременного использования блокирующего и неблокирующего, просто экспериментировал с ними (хотя я действительно ниже среднего уровня в программировании ПЛИС), в данном случае синтезируется в одну и ту же схему, вот и не поменял назад, с этим могут возникнуть проблемы?

-

Вообще у меня на столе сейчас лежит мост SpaceWire/Ethernet он по SpaceWire обеспечивает скорость в 500 Мбит/сек, как на передачу, так и на прием, там стоит 2 ПЛИС одна альтеровская вторая хилых, хилых отвечает за SpW, альтера за Ether, плис напрямую подключена к портам SpaceWire без каких либо микросхем между ними, это Virtex 5. Вот и как они это сделали ? То есть у меня подход не правильный начиная с описания блока на verilog? Не стал вам сразу отвечать, разбирал мост SpaceWire/Ethernet который от компании MiT проверял какие микросхемы у них на плате, кроме плис Xilinx в части SpaceWire больше нет ничего, обеспечивает 500Мбит/сек и туда и обратно, у меня Artix 7. Может быть проблема в чипе?

-

Надо попробовать, спасибо, но как зафиксировать в планере? Нет до машины состояний не доходит двухфронтовая логика, она работает вообще под другим тактовым доменом, после этого модуля есть еще два модуля они работают по одному фронту (нужны что бы собрать символы из последовательных в параллельные и определить что за символ пришел) Согласен, но почему-то скорость в симуляции достигала 500Мбит/сек и эта скорсть зависит от выбора портов, следовательно это зависит от имплементации в том числе

-

Спасибо за ответ! Хотел так сделать, но никакого руководства не нашел по этому поводу не нашел, пытался сделать "в слепую", получилось в худшую сторону изменить результат, думаю можно и в лучшую, если есть какое-то руководство у вас буду признателен. Да такое можно сделать, тем более все и должно закончится созданием печатного узла и будет возможно организовать задержку, но хотелось бы получить максимальные скорости без этого, тем более что 500Мбит получилось сделать, но без остальной "обвязки", то есть думаю возможно настроить именно "правилами" проектирования. Триггер же тактировать надо будет чем-то, или может я не понял что вы имеете ввиду. Я не хочу получить больше, такие значения вышли при симуляции отдельно взятого приемника, но при объединении всех модулей скорость падает, как сделать так чтобы скорость приема осталась прежней? в целом и 400Мбит терпимо. Я вижу путь решения через "Constraints", однако не уверен правильно ли понимаю, как он работает и можно ли эту разницу в скорости прихода сигналов сделать определенной.

-

Приемник DS-кода на ПЛИС XILINX

Koctix опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте, я занимаюсь разработкой приемопередатчика SpaceWire, передатчик я сделал, необходим приемник. Протокол SpaceWire использует DS-кодирование для передачи информации, это кодирование имеет две линии Strob и Data, Strob изменяется всегда, когда не меняется Data, в сигнале закодирован тактовый импульс, восстановить его можно на другой стороне с помощью операции XOR. Есть два основных подхода к реализации приемников, назовем условно их "синхронный" и "асинхронный", синхронный по событиям от внутреннего тактового импульса считывает сигнал, асинхронный восстанавливает тактовый сигнал из самого DS-кода с помощью XOR. Я реализовал асинхронный прием, однако в ходе симуляции оказалось, что поднять скорость приема выше 300Мбит/сек не выходит, а связано это с тем, что XOR реагирует на пришедший сигнал с небольшой задержкой и восстановленный тактовый импуль после него не успевает запустить событие в модуле приема до того как сигнал данных изменится. Если это все компоновать вместе с передатчиком и машиной состояний (необходима для реализации других уровней протокола), то скорость может упасть и до 100Мбит/сек. Была идея задержать сигнал данных до модуля приема с помощью пустой логической операции, в симуляции отдельно для приемника получалось достичь более 500 Мбит/сек, однако это все сильно зависило от выбранных пинов и при изменении их выбора менялась скорость, в сочитании со всем остальным наполнением скорость не повысилась. Вопрос в следующем, может кто-то сталкивался с такой проблемой и знает решение или же я пошел не по тому пути и нужно делать иначе, слышал что оптимизировать трассировку можно с помощью Constraints, но так и не нашел как правильно ими пользоваться для таких задач. Модуль приема описан следующим образом: module Resiv_sem_var2( input Din,// линия данных input Sin, // линия строба input Codes_Check, //маркер символа управления input reset, output clk, // тактовый сигнал образованный операцией XOR output reg [1:0] Data, //выход данных (собирает по два бита) output reg [2:0] count=3'b100, //(счетчик указывает на номер пары битов в символе) output reg Start=0 //output Din_buf ); assign clk=(Din==Sin)?0:1; // XOR reg Start=0; reg DataLeft=0; always @(posedge clk)begin DataLeft<=Din; if (reset==1) DataLeft=0; end always @(negedge clk)begin Start<=1; if (reset==1)begin // сброс count=3'b100; Data=0; Start=0; end else begin if(Codes_Check==0)begin //счетчик для N-Char if (count<3'b100) count<=count+1; else count<=0; end if(Codes_Check==1)begin // счетчик для L-Char if (count<3'b001) count<=count+1; else count<=0; end Data[1]<=Din; Data[0]<=DataLeft; end end endmodule