Вадим Н.

Участник-

Постов

22 -

Зарегистрирован

-

Посещение

Репутация

1 ОбычныйИнформация о Вадим Н.

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

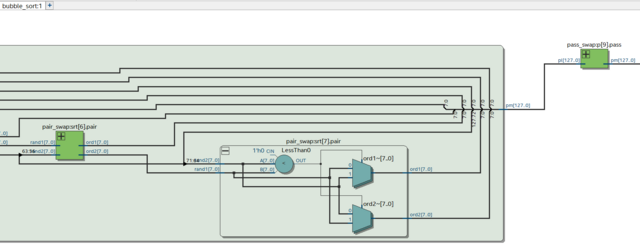

Всем привет! Тут, просто, ради интереса, довелось ответить на такой вопрос: Пузырьковая сортировка в ПЛИС "за один такт". Другими словами, только в виде комбинаторной логики, без синхросигнала и регистров. Verilog (не System). На входе и на выходе - массивы. На выходе - отсортированный. Чтобы было в общем виде, через параметры и циклы generate. Оказалось довольно интересно. Первое что поразило. Это слишком большая ошибка в оценке времени на разработку. Задача казалась очень простой. Сразу было ясно, что это будет многократное повторение простейшего модуля с перестановкой двух элементов. Сначала воспроизвёл алгоритм в perl, чтобы со стороны взглянуть на проблему. На это ушёл вечер - не считаем его вообще. Далее, накидал структуру модулей (перестановка, один проход, собственно сортировка и тестбенчи для всех) и решил что вся разработка с этого момента займёт пару вечеров... В первый вечер стало ясно, что знания по циклу generate не в один момент загружаются в голову... Пришлось поменять тактику: раскидать модули по файлам, прикрутить контроль версий. Долго-ли коротко-ли, ушло раз в 5-6 больше времени. И это довольно характерный коэффициент для меня. Просто до смешного стабильный показатель )) Это один результат, который надо ещё осмыслить )) Ну и оказалось, что этот проект интересно разглядывать через утилиты Квартуса. Особенно в процессе знакомства с generate + цикл. Очень наглядно: 1. RTL Viewer (см. скрин) 2. Timing Analyzer - путь с максимальной задержкой как меняется от размерностей массива 3. Technology Map Viewer (тут можно увидеть как всё конвертируется в таблицы истинности*) * если я правильно понимаю м.б. кому-нибудь пригодится И конечно интересны комментарии и соображения по всем задетым темам, если у кого они есть. bubble_sort.7z

-

- переключался на другие задачи. Вот, можно сказать, вернулся к теме ПЛИС. Не уверен что мы общались в личке или я скачивал ваши примеры. В любом случае Спасибо ) to all Закину прямо сюда testbench как он был сделан (на момент прыжка в сторону) сам модуль тоже прилагаю в архиве. С оговоркой, что это дилетантизм, и проходной пример в процессе поиска решений. Вопросов по нему у меня нет. Но может кому то просто интересно. exs.7z

-

sazh, попробовал примерчик свой переделать в таком стиле в принципе, норм. Спасибо! А то я как то из тех примеров что в интернете встречал не понял как оставаясь в режиме one-hot, организовать выбор адреса. Расширить шину данных до соответствия трёхбитным адресам - мне эта идея вообще не пришла. Да я сейчас ещё не уверен что это практично может быть. Ну будет в арсенале там посмотрим.

-

точно! Хотя "IEEE Std 1364-2001" у меня всегда под рукой, как то именно раздел "part-select" до сих пор пропускал. А всё потому что там картинок нет при столь не очевидной схеме +, -, lsb, msb %)

-

Вадим Н. подписался на повышение частоты clock на verilog и Литература по VHDL

-

litv, спасибо! ознакомился с "HDL Chip Design..." подход к изложению норм. Но есть нюанс. * у меня нет этой книжки целиком, есть одна глава: General Coding Guidelines Chapter 13: Recommended HDL Coding Styles "FPGA\intel-Altera\Quartus II\Handbook\1 Design and Synthesis\qts_qii51007.pdf" RobFPGA, спасибо! вас понял. Точнее, понял оп чём речь когда прочитал про классификацию мультиплексоров в этом квартус-дизайн буке (см. выше) sazh, спасибо! это SV наверное, и уровень супер эрор-пруф прогрэмин. - не. я пока пешком )

-

Как правильно описать мультиплексор

Вадим Н. опубликовал тема в Языки проектирования на ПЛИС (FPGA)

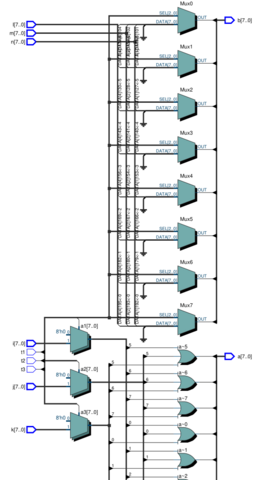

Требуется мультиплексор для задачи которая в общем описана в testbench ниже. Сначала я интуитивно всё это нарисовал и всё казалось нормально (см. первый вариант). Но потом стало ясно что ни кто так не делает. Поискал по форуму всё с "mux" (в частности). Написал вариант генерирующий мультиплексор (см. второй вариант). С использованием for для генерации комбинаторной логики всё ясно, но тут управляющий сигнал по другому устроен. И переделывать его, вроде бы, нет оснований. Так что я case использовал. Может будут какие-нибудь замечания... правильно ли использовать always @ (*) ? -

вообще то, мне это обсуждение помогло, (за что я очень признателен всем причастным) Testbench, вот сейчас рисую. Он выглядит более структурировано чем предидущие. И главное, в нём прописано, что собственно хотелось бы проверить на каждом этапе. Более осознанный подход )) но проверять предполагается по-прежнему визуально.

-

по поводу ethermac: Из всего что там есть, модуль wb_bus_mon.v вроде бы понял как работает. Он прикручен к "шине" в тестбенче. Пишет в лог все противоестественные сочетания значений на шине. Сам лог, вроде бы, дальше не анализируется. У меня в проекте ни каких шин таких нет, хотя в гораздо меньшем объёме тоже можно прикрутить сбоку к выходным сигналам такой монитор. Сейчас я ради этого в modelsim в wave.do добавляю сигнал: quietly virtual function -install /testbench/uut -env /testbench/uut { (k[1] && k[4]) || (k[2] && k[3])} comm Вроде бы, если я правильно понял, для основных тестов используется целая нервная система из событий, "симофоров" и двух уровней отладочных модулей. На одном уровне описан план тестирования а другой уровень изображает из себя интерфейс и выполняет задачи отправки данных через "устройство". Такое можно в рамках целого проекта поддерживать, но не для каждого модуля. А всё-таки каждый модуль тоже нуждается в формальной проверке. Мне кажется, в Quartus, что что-то подобное предпологается. Вот в настройках проекта / EDA Tool Settings / Simulation / Test Benches... / Edit / Run simulation until all vector stimuli are used Vector stimuli это что латынь? Что имели ввиду авторы? Кто нибудь видел tutorial с данным подходом? Я только нашёл что Quartus под это дело генерирует шаблон: в этом шаблоне имеется регистр eachvec. Видимо, дальше всё супер-просто, но где пример )) кто нибудь видел пример от intel/altera/mentor_graphics, объясняющий концепцию?

-

народ, спасибо за проявленное участие к этой драме. Да - как верно предположили - проекты у меня не сложные. Пару лет назад слова ПЛИСка в моём лексиконе вообще не было. Но есть задача, и закон диалектики (или чего там) о переходе количества в качество уже вот-вот прилетит по башке. des00, спасибо за наводку, уже вытянул с github-а. А вообще захотелось супер быстро изготовить модуль. Уже далеко не десятый, так что надо прям по щелчку. Типа, сначала тест. Он и будет спецификацией. А потом уже модуль. Тест проходит, следовательно удовлетворяет спецификации - и фсё! - Понятно, в общем... Я ещё может сюда его закину, если получится быстро что-нибудь сгородить.

-

угу. значит не избежать думать головой ) и метода test-first не годится хотя бы потому что заточена на какие-то статические вещи "если на входе то, то на выходе должно быть это". А здесь у нас процессы, параллельное выполнение, обратная связь, зависимость от предидущего состояния.. слишком много надо городить чтобы хотя бы входной сигнал сгенерировать. Хотя на простом примере попробовать можно. Подход с файлами, с входными и выходными векторами, по крайней мере на каких то задачах попытаюсь применить. Спасибо!

-

Кто-нибудь может поделиться примерами автоматизации тестирования модулей verilog? (имеется ввиду этап симуляции в modelsim) Реально ли использовать в разработке модулей на verilog подход "test first"? Реально ли отказаться от визуального контроля в режиме "Wave" в пользу консольного вывода наподобие Test::Simple ?

-

Значит это нормальный подход. Ну и прекрасно. Можно гнать дальше. Всем спасибо!

-

где то в настройках Quartus предупреждает, что симуляция должна быть в пика-секундах я не знаю как запустить вручную проект содержащий мегафункции. Так что хочу я или нет там будут пика-секунды. Хотя в тестбенче указано `timescale 1ns / 1ps

-

повышение частоты clock на verilog

Вадим Н. опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем привет! Мой проект для Cyclon-IV на verilog содержит мегафункцию ALTPLL для повышения частоты вторичного clock в 50 раз. Симуляция сгенерированного колхоза - вещь супер медленная, как оказалось. Есть какая-нибудь простая схема на verilog для повышения частоты вторичного clock, чтобы симуляция в ModelSim шла быстрее (чем при использовании стандартной мегафункции)? Пока я наоборот делаю: для симуляции повышаю частоту внешнего тактового сигнала, а сгенерированный модуль ALTPLL заменяю на простую передачу внешнего сигнала -

исчезла поддержка modelsim хотя может, квеста это тот-же моделсим - вид сбоку - я не знаю. кто-нибудь может пояснить ситуацию: на сайт интел захожу через бесплатный VPN. всё норм. Пытаюсь скачать любой дистриб для винды (там они все в exe-формате) - вылетает страница The requested URL was rejected. Please consult with your administrator может быть это надо VPN платный? или в чём тут дело?