blackfin

Свой-

Постов

4 139 -

Зарегистрирован

-

Победитель дней

4

blackfin стал победителем дня 1 сентября

blackfin имел наиболее популярный контент!

Репутация

25 Очень хорошийИнформация о blackfin

-

Звание

Гуру

Контакты

-

Сайт

Array

-

ICQ

Array

-

HF RFID ридер ISO15693

blackfin ответил my504 тема в RF & Microwave Design

А керамические конденсаторы с пьезо-эффектом в "фильтре на ОУ" используются? На частоте 423,75 кГц пьезо-эффект керамических конденсаторов может быть все еще достаточно большим для паразитной ПОС в усилителе. -

HF RFID ридер ISO15693

blackfin ответил my504 тема в RF & Microwave Design

IMHO, тракт приемника возбуждается "на частоте этого фильтра". Все-таки, 80 дБ это довольно большое усиление. И не понятно, почему "фильтр на ОУ" стоит после усилителя..? Во всех учебниках по РПУ фильтр на ПЧ стоит сразу после смесителя перед усилителем. -

Для ADC12DJ5200RF можно легко посчитать максимальную частоту клока данных на выходе IP Core JESD204C: Для JESD204C из PG242 (см.: Table 6) находим: rx_core_clk = Serial line rate / 66 (for 64B66B linecoding) = 17.16 / 66 = 0.26 GHz.

-

Отуда у вас эти цифры? С потолка? И какой speed grade у вашей ПЛИС? Читайте DS923, Table 33: Block RAM and FIFO Switching Characteristics. Но даже самый медленный Virtex UltraScale+ умеет обрабатывать (читать и писать в BRAM) на частоте 642 МГц: vup_1_ctscanner.

-

Ессно, есть: for (int i = 0; i < 6*6*6*6*6*6; i++) { D0 = i%6; D1 = i/6%6; D2 = i/(6*6)%6; D3 = i/(6*6*6)%6; D4 = i/(6*6*6*6)%6; D5 = i/(6*6*6*6*6)%6; }

-

АЦП 140 dB / 100 SPS ?

blackfin ответил Ruslan1 тема в Операционные усилители и АЦП

Вопрос не только в величине плотности шума. Важно, что шумы Vref, ADC, Fclk (jitter), усилителя и проч., некореллированы в точках: T[n], T[n]+T*1/4, T[n]+T*2/4, T[n]+T*3/4. -

АЦП 140 dB / 100 SPS ?

blackfin ответил Ruslan1 тема в Операционные усилители и АЦП

Толк есть, если тактировать каждый АЦП отдельным клоком Fclk сдвинутым на T/4 относительно опорного клока. То есть, из нескольких АЦП можно сделать АЦП с частотой семплирования Fclk*4, а потом сделать децимацию на 4. -

Попадались, но не кварцевые и не резонаторы: SiT8944

-

Ultra-640_SCSI передавал 320 Мбит/с по каждой LVDS паре на 10 метров ещё 20 лет назад..

-

ADL5610 / ADL5611 ?

-

Long Lifecycle FPGA:

-

GitHub: `ifdef VCS $display("Synopsis VCS"); `endif `ifdef INCA $display("Cadence NC-Verilog"); `endif `ifdef MODEL_TECH $display("Mentor Graphics ModelSIM/Questa"); `endif `ifdef XILINX_ISIM $display("Xilinx ISE Simulator"); `endif `ifdef XILINX_SIMULATOR $display("Xilinx Vivado Simulator"); `endif `ifdef __ICARUS__ $display("Icarus Verilog <http://iverilog.icarus.com>"); `endif `ifdef VERILATOR $display("Verilator <https://www.veripool.org/wiki/verilator>"); `endif `ifdef Veritak $display("Veritak <http://www.sugawara-systems.com>"); `endif

-

Измерение разности фаз

blackfin ответил SergeyVas тема в В помощь начинающему

1000 ppm это "стабильная частота"??? "Куда катится этот мир?".. -

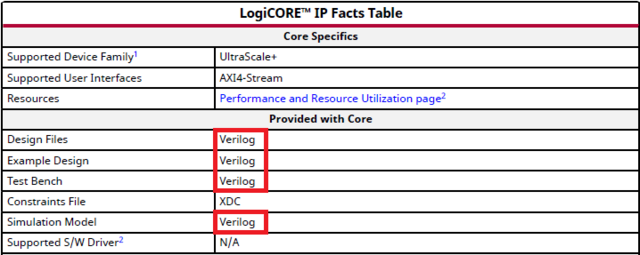

И ещё более многие делают то же самое на Verilog! Удивляет другое! Почему-то все новые IP-Cores Xilinx упорно пишет на Verilog'е (ну или на SV). Открываем любой PG на более-менее современную IP-Core (PG203,PG210,PG211,PG213,PG251,PG302) и видим такую таблицу: Может, Xilinx не знает, что VHDL лучше, эффективнее, безопаснее, удобнее? Может, пора ему всё объяснить?