blackfin

Свой-

Постов

4 126 -

Зарегистрирован

-

Победитель дней

3

Весь контент blackfin

-

Судя по всему, в версии 2022.1 поломали комплексный умножитель - на выходе умножителя нули.

-

QUARTUS, MODELSIM

blackfin ответил aosp тема в Среды разработки - обсуждаем САПРы

Была похожая тема: -

Прохождение сигнала через Sinc фильтр

blackfin ответил zuuuuk тема в Алгоритмы ЦОС (DSP)

Wiki: Sinc filter In signal processing, a sinc filter is an idealized filter that removes all frequency components above a given cutoff frequency, without affecting lower frequencies, and has linear phase response. The filter's impulse response is a sinc function in the time domain, and its frequency response is a rectangular function. The name "sinc filter" is applied also to the filter shape that is rectangular in time and a sinc function in frequency, as opposed to the ideal low-pass sinc filter, which is sinc in time and rectangular in frequency. In case of confusion, one may refer to these as sinc-in-frequency and sinc-in-time, according to which domain the filter is sinc in. -

Из одного цап в два

blackfin ответил whale тема в В помощь начинающему

На 8-ми выводах можно сделать два 8-ми битных ЦАП'а - R2R + ШИМ: Hybrid PWM/R2R DAC improves on both -

Избыточное кодирование

blackfin ответил amaora тема в В помощь начинающему

Для кодов БЧХ, если нужна "устойчивость к потере до ~50% передаваемых данных", то объем передаваемых данных нужно увеличить в 4-6 раз. Вот примеры нескольких кодов БЧХ исправляющих ~50% ошибок: t = 3: code = (15,5,7) t = 6: code = (31,6,13) t = 10: code = (63,18,21) t = 21: code = (127,29,43) t = 31: code = (255,55,63) t = 59: code = (511,112,119) t = 111: code = (1023,218,223) t = 215: code = (2047,419,431) t = 413: code = (4095,826,827) t = 766: code = (8191,1522,1533) t = 1495: code = (16383,2978,2991) t = 2905: code = (32767,5809,5811) t = 5610: code = (65535,11211,11221) Где t - количество исправляемых ошибок. То есть, для кода (65535,11211,11221) длина сообщения равна 11211 бит, а длина кода равна 65535 бит. Это равносильно увеличению объема передаваемых данных в 65535/11211 = 5,85 раза. -

Brand New Starlink Dish To Reduce Power Yet Improve Efficiency & Density:

-

Знала и довольно давно:

-

ФЧХ можно легко вычислить, зная АЧХ. Учите мат-часть: Соотноше́ния Кра́мерса — Кро́нига. PS. Нет, я был не прав.. Зная Re[K(w)] можно вычислить Im[K(w)] и наоборот. С модулем K(w) такой фокус, кажется, не пройдет. PPS. Но в любом случае, судя по графику из первого поста, ФЧХ известна.

-

Можно. Функция КЧХ является аналитической. Ваш, КО.

-

-

OK. Вот MTBF в пустом проекте на K3UP-2-i: +----------------+-----------------+----------------+ | Structure Type | Total in Design | MTBF | +----------------+-----------------+----------------+ | Synchronizers | 16 | 2.96e+03 years | | FIFOs | 0 | --- | | Overall | 16 | --- | +----------------+-----------------+----------------+ +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ | CDC Path | MTBF | Data Toggle Rate(Mtrs) | Data Sample Rate(Mhz) | Total Settling Time(ns) | Sending Domain | Receiving Domain | Number Stages | CDC Net Name | +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ | 1 | 1.65e+08 years | 3.36 | 690 | 1.81 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__0[0] | | 2 | 7.55e+03 years | 3.4 | 690 | 1.38 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__2[0] | | 3 | 4.01e+04 years | 3.64 | 690 | 1.46 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__4[0] | | 4 | 1.55e+06 years | 2.84 | 690 | 1.57 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__6[0] | | 5 | 3.9e+04 years | 2.45 | 690 | 1.46 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__8[0] | | 6 | 1.51e+06 years | 2.54 | 690 | 1.55 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__10[0] | | 7 | 2.01e+08 years | 3.64 | 690 | 1.79 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__12[0] | | 8 | 6.5e+03 years | 3.81 | 690 | 1.34 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__14[0] | | 9 | UNDEFINED | ZERO* | 714 | 1.54 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__15[0] | | 10 | UNDEFINED | ZERO* | 714 | 1.76 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__1[0] | | 11 | UNDEFINED | ZERO* | 714 | 1.63 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__3[0] | | 12 | UNDEFINED | ZERO* | 714 | 1.63 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__5[0] | | 13 | UNDEFINED | ZERO* | 714 | 1.62 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__7[0] | | 14 | UNDEFINED | ZERO* | 714 | 1.79 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__9[0] | | 15 | UNDEFINED | ZERO* | 714 | 1.75 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__11[0] | | 16 | UNDEFINED | ZERO* | 714 | 1.61 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__13[0] | +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ * Summary: Overall Synchronizer MTBF:2.96e+03 years Только не понял, почему для m_axis_* -> s_axis_* Toggle Rate равны ZERO*.

-

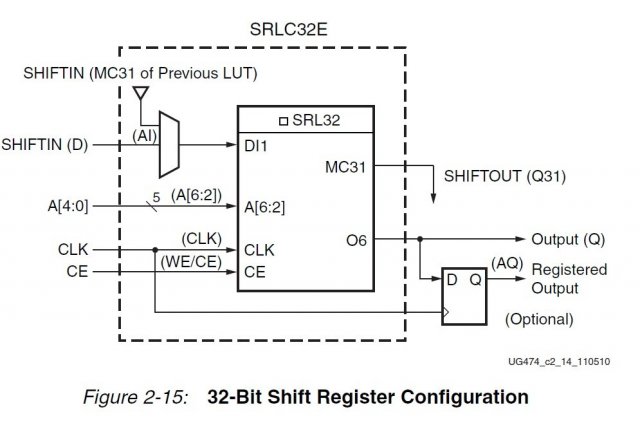

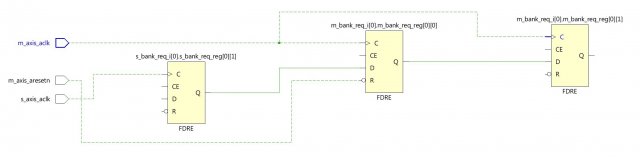

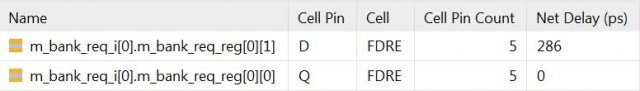

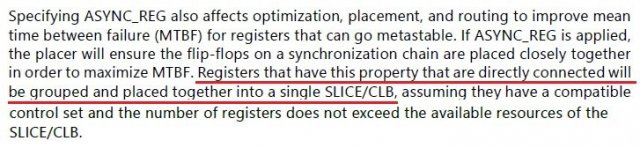

Зря надеетесь.. :) Да, всё так. Хотя на мой взгляд, логичнее было бы сделать на SRLC32E: Но Виваде, конечно, виднее.. :) ---------------------------------- Посмотрел в рабочем проекте как соединены триггера с атрибутом ASYNC_REG: Да, регистры соединены через интерконнект: Но задержка всего 286 ps:

-

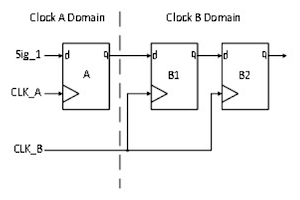

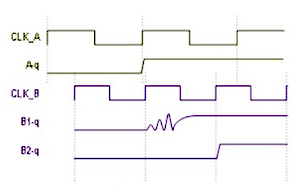

Задержки на выходе цепочки ASYNC регистров к CDC отношения уже не имеют, а потому на величину MTBF никак не влияют. А разговор сейчас именно про влияние задержки между регистрами в схеме CDC на величину MTBF. Вот схема: А вот диаграмма: Если провод с выхода B1-q будет длинным (с большой задержкой), то колебания на выходе B1-q сместятся вправо на величину этой задержки. При этом, вероятность того, что триггер B2 тоже окажется в метастабильном состоянии увеличится, так как на входе d триггера B2 будет нестабильное значение.

-

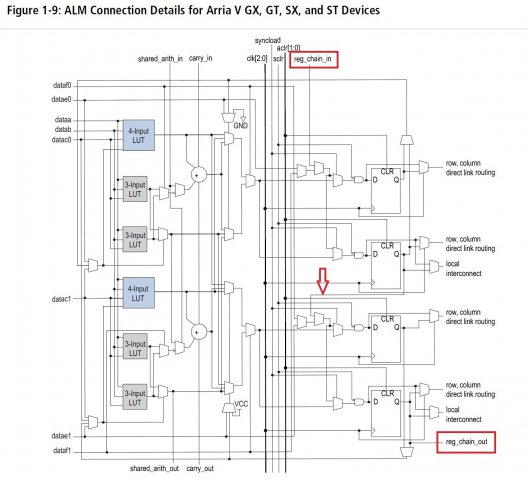

Хм.. Я всегда считал, что роутинг реализован между SLICE'ами. Внутри SLICE/CLB всё жестко соединено проводами и задержки внутри одного SLICE/CLB не больше сотни пс.

-

-

Готовых решений полно на edn: Synchronizer techniques for multi-clock domain SoCs & FPGAs 10 design issues to avoid during clock domain crossing Get those clock domains in sync И в конце каждой статьи есть ещё ссылки на похожие статьи по этой же теме.

-

Сделайте им Clear Cache: Tools->Settings->Project Settings->IP->Clear Cache.

-

Доделать проект видеорекордера.

blackfin ответил 163264 тема в Предлагаю работу

DRM ? Использование DRM в России -

Можно три старших бита упаковать в TUSER, а восемь оставшихся бит упаковать в TDATA. Насколько я понял, стандарту IHI0051A это не противоречит. Это если требуется воспользоваться готовыми IP Cores из PG085.

-

Да, не универсальный, но ADI уже предлагает виртуальные инструменты для тестирования своих АЦП: AD9213 Remote Evaluation Tool

-

Есть xapp523, но она для Kintex'ов и в ds182 пишут, что в Kintex'ах IDELAY/ODELAY chain resolution = 39 to 78 [ps]. Для Artix UltraScale+ в ds931 пишут, что IDELAY/ODELAY chain resolution = 2.1 to 12 [ps]. Так что и на Artix UltraScale+ ошибку меньше 2 ps на IDELAY/ODELAY chain не сделать.

-

Kickback current:

-

Фольгированный текстолит

-

Цифровой приём

blackfin ответил patron тема в RF & Microwave Design

Я смотрел фильтры с полосой от 60 МГц до 100 МГц. Вы дали ссылку на фильтр с полосой 240 МГц. Согласитесь, это разные мегагерцы.. Но все равно спасибо. Ход ваших мыслей ясен.. )) -

Цифровой приём

blackfin ответил patron тема в RF & Microwave Design

Так я ради спортивного интереса уже просмотрел несколько десятков фильтров. У всех внеполосное подавление 30-40 дБ. Потому и спрашиваю. Пока не озвучены параметры существующих в природе фильтров, смысл переноса на ПЧ такой широкой полосы не очевиден.