blackfin

Свой-

Постов

4 126 -

Зарегистрирован

-

Победитель дней

3

Весь контент blackfin

-

ADI: Low Noise Op Amps

-

А из чего следует, что переменная "a" имеет целочисленный тип? Что будет, если a = 9.5 ? И второй вопрос: из чего следует, что значение "a" не меняется в первом операторе ? Как будет работать такой код: if (a < 10) {a = a + b;} if (a > 9) {}

-

Тогда, наверное, нужно оставить и файлы *.xcix

-

-

-

Не совсем то, но возможно, пригодится: Adaptively Cancelling Server Fan Noise

-

Ужос! Не знал. Спасибо, за ликбез.. :)

-

А что это за процы? И почему их так много? Может, можно все сделать как-то проще?

-

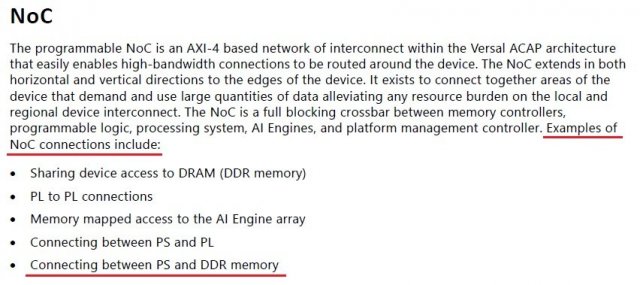

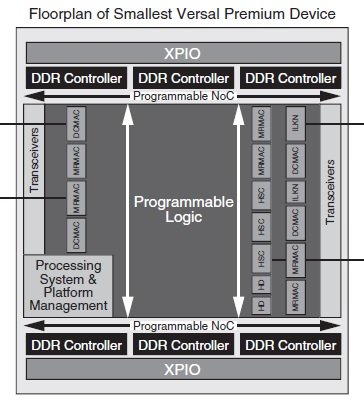

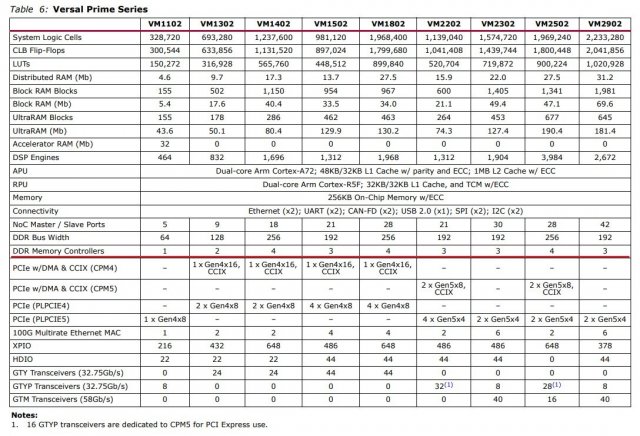

На мой взгляд, это следует из здравого смысла. Очевидно, что всем Cortex'ам непременно нужна внешняя DDR память. Самый короткий путь к этой памяти лежит через NoC и аппаратные контроллеры DDR. Можно, конечно, вообразить, что в PL будет синтезирован soft DDR контроллер для монопольного доступа к внешней памяти со стороны Cortex'ов, но этот путь длиннее и ест ресурсы PL: PS->NoC->PL (soft DDR)->XPIO. Вот ещё картинка из wp519:

-

Аппаратный, но жестко привязан к Cortex-A72: То есть, ломиться в него со стороны FPGA можно, но придется конкурировать с процессорами A72 и R5.

-

Похоже на то. Особенно если учесть, что на картинке указан довольно странный бит-рейт (4266Mb/s) для LPDDR4 памяти.

-

Наверное, это была презентация Versal HBM. Там и сама память DDR аппаратная.

-

Если 4% это 100k LUTs, то речь, видимо, о XCVU440.. Круто! На спичках уже можно не экономить.. :)

-

Для XC7A200T-2 этот же проект работает на частоте ~250 MHz. Про float'ы ничего не скажу, не пробовал. А 24-х битное FFT на 16к точек с фиксированной запятой работает в XCKU60-2-i на 475 MHz. Чип заполнен на 5%. Понятно, что если чип будет заполнен на 80%, то эта частота будет существенно ниже. Видимо, на сайте Xilinx'а указана такая высокая частота IP Cores именно потому, что их частота измеряется на практически пустых чипах..

-

Сделал пробный P&R тестового проекта на XCAU25P-2-i. Для чипа заполненного на ~30% проект работает на частоте ~600 MHz. Осталось выяснить цены.. :)

-

Vitis™ Unified Software Platform 2021.1.1 is now available: - with support for Artix UltraScale+ Devices:- XCAU25P

-

Ну меня повеселили вот эти ваши откровения: И это при том, что в мануале на DC на стр. 82 сам Synopsys приводит пример использования default в операторе case и дает пояснения по синтезу latches. PS. Уж не знаю, какой вы разработчик ASIC'ов, но в элементарных вещах вы явно плаваете.. :)

-

Кстати, да. При чем тут инициализация? До вас о ней тут никто не упоминал. Речь, напомню, шла про отсутствие дефолтных кейсов. Про инициализацию вы запели чтобы увести разговор в сторону и заболтать вопрос. Впрочем, это ваша обычная манера.. :)

-

Серьёзно? Ну, тогда Synopsys пишет, видимо, на чем-то другом.. :):):)

-

Да хотя бы FFT.. :) Сможет Матлаб-hdl "из коробки" посчитать FFT на 4096 точек на каком-нить XCVU3P за 1,5 мкс?

-

Только нужно определиться с тем, что мы понимаем под термином "первый боковой лепесток". :) После умножения функции sinc(γTt/2) на функцию cos(ω0t) (из учебника на стр. 72-73) главный лепесток функции sinc() распадется на несколько лепестков имеющих большую амплитуду и меньшую ширину. Например, при соотношении частот Fhi = 2*Flo главный лепесток функции sinc() превратится в семь более узких лепестков.

-

Нее.. Монстры вот тут: :)

-

200 MHz на CYCLONE V EX С8 ??? Да вы оптимист!.. :) Вот результат синтеза FFT на 64k точек для 5CEFA9F23C7: +-----------------------------------------------------------------------------------+ ; Fitter Summary ; +---------------------------------+-------------------------------------------------+ ; Fitter Status ; Successful - Tue Jul 27 19:53:33 2021 ; ; Top-level Entity Name ; fft ; ; Family ; Cyclone V ; ; Device ; 5CEFA9F23C7 ; ; Timing Models ; Final ; ; Logic utilization (in ALMs) ; 1,801 / 113,560 ( 2 % ) ; ; Total registers ; 4314 ; ; Total block memory bits ; 2,713,752 / 12,492,800 ( 22 % ) ; ; Total RAM Blocks ; 337 / 1,220 ( 28 % ) ; ; Total DSP Blocks ; 6 / 342 ( 2 % ) ; ; Total PLLs ; 1 / 8 ( 13 % ) ; +---------------------------------+-------------------------------------------------+ +----------------------------------------------------------------------------------------------------------------+ ; Slow 1100mV 0C Model Fmax Summary ; +------------+-----------------+--------------------------------------------------------------------------+------+ ; Fmax ; Restricted Fmax ; Clock Name ; Note ; +------------+-----------------+--------------------------------------------------------------------------+------+ ; 202.18 MHz ; 202.18 MHz ; pll_inst|pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk ; ; +------------+-----------------+--------------------------------------------------------------------------+------+

-

Медиана векторного массива

blackfin ответил my504 тема в Алгоритмы ЦОС (DSP)

Скажу, что он тоже сформулирован с ошибками.. :)