-

Постов

1 241 -

Зарегистрирован

-

Посещение

-

Победитель дней

9

Весь контент VladislavS

-

Даже чистые виртуальные в итоге, к сожалению, не бесплатны. А оно нам не надо.

-

Так я и смотрю. Ограничение есть. Когда я об него споткнусь - вопрос только времени.

-

Конечно!

-

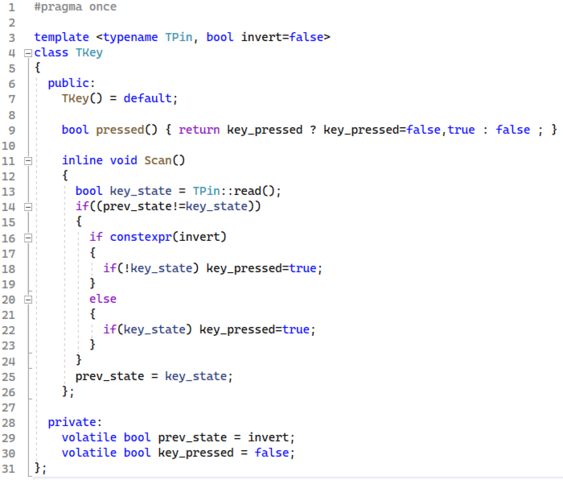

Там проблема с constexpr будет. Не делают так. Сейчас можно концептов навесить и фактически задать требования к интерфейсу.

-

В плюсах всё гораздо проще. Код можно в описании класса писать прямо в заголовочных файлах. Количество единиц трансляции снижается до минимума автоматически.

-

В данном случае всё наоборот. Память 32 бита, периферийное <32 бита. Всё одной записью обойдётся.

-

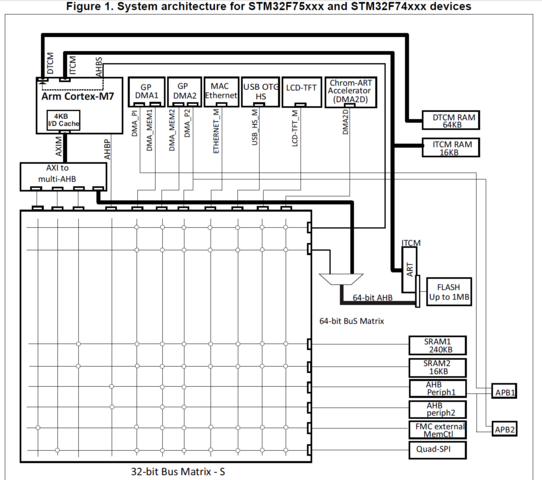

Шина. Не даст она двум устройствам одновременно доступ.

-

Не может. Причём тут доступ к памяти и барьерные инструкции?

-

stm32f1 автомат управления уровня воды

VladislavS ответил dimir тема в STM

Держи нас в курсе! -

Чужой исходник -> IAR

VladislavS ответил muravei тема в IAR

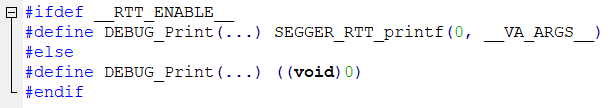

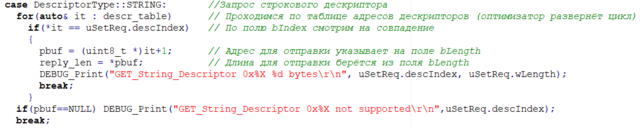

Предать анафеме всю эту макросную муть!!! -

А это такая народная забава пытаться сделат всё через опу, лишь бы не использовать предназначенное для этого устройство(таймер)?

-

Все попытки сделать импульс программно умрут вот тут Проследите путь от CPU до GPIO (он не работает на частоте CPU) и всё поймёте. А вот таймер с ШИМ то что доктор прописал.

-

Инициализовать массив во Flash-памяти

VladislavS ответил tathagata тема в Keil

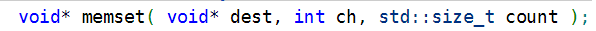

Если она в процессе работы перешивается, например. Чтобы компилятор не подумал, что там всегда нули как во время компиляции и не соптимизировал доступ к ней. -

Компилятор IAR 8.5 Си не дает ошибку

VladislavS ответил razrab83 тема в IAR

-

Компилятор IAR 8.5 Си не дает ошибку

VladislavS ответил razrab83 тема в IAR

Глобальная по стандарту должна инититься нулём. Все остальные нет и иар это, самом собой, не делает. -

У кортексов в таблице векторов прерываний есть пустые места. Идеальное место для хранения размера прошивки, crc и т.д.

-

STM32G4 PLL

VladislavS ответил Sergo1799 тема в ARM, 32bit

На будущее, в кубе отличный конфигуратор системы тактирования. Не надо даже код генерить, а просто установить все делители и переключатели правильно и на их основе код написать. -

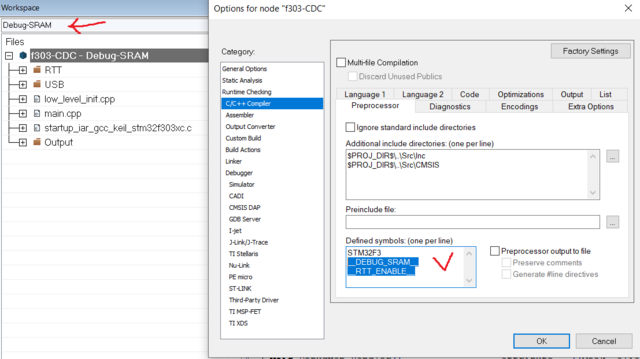

Бинарник должен быть разный? Тогда это и есть условная компиляция, которая делается заданием WE_ARE_RUNNING_UNDER_DEBUGGER в одной из конфигураций.

-

Бывают программы, которые работают не благодаря, а вопреки. В них главное - не спугнуть.

-

Он их не совмещает, а изначально формирует так как вы описали во втором абзаце вашего сообщения. Зачем? При взгляде на исходник должно быть видно ЧТО делает код, а не КАК. Часто вы кишки printf изучаете при его использовании? При такой постановке задачи и результата ноль. И выводы ложные. А реальная задача автора "мигать списком диодов". Ну это оно и есть. Именно так и делается. Именно поэтому нет совмещения volatile, а есть их оптимальное формирование.

-

Об ошибочном заключении, что автор статьи получил сложным способом тот же результат и поэтому делать так не имеет смысла. Имеет, просто надо более сильное кунг-фу использовать, тогда результат будет лучше.

-

Нет, я не о том как лучше ногами дрыгать. Вы неправильно поняли.

-

Задача - помигать четырьмя диодами, приведёнными в списке. На С вы решаете сами первым или вторым способом её решать. А на С++ я просто говорю "переключи состояние всех диодов из списка". Есественно, заменить первое<=>второе он не имеет права. Но сформировать одну операцию вместо трёх для решения задачи на этапе компиляции и есть джедайство.

-

Что volatile?

-

Не нахожу. Код автора статьи (без delay, он тут ни на что не влияет) я бы написал так. using LEDS = PinList<PA_5,PC_5,PC_8,PC_9>; for(;;) LEDS::toggle(); Что для STM32 в процессе компиляции превратиться во что-то такое for(;;) { // PA5 toggle if (GPIOA->ODR & (1<<5)) *((volatile uint16_t *)&GPIOA->BSRR+1) = (1<<5); else GPIOA->BSRR = (1<<5); // PC5,PC8,PC9 toggle GPIOC->BSRR = (((1<<5)|(1<<8)|(1<<9)) << 16) | (~GPIOC->ODR & ((1<<5)|(1<<8)|(1<<9))); } Естественно не в ODR ^=, ибо это неправильно. Ну и из-под ARM Compiler v6 будет как-то так MOVS r0,#0x14 MOVW r2,#0x320 MOVW r3,#0x818 MOVT r0,#0x4800 // R0 = &GPIOA->ODR MOV r12,#0x20 MOVT r2,#0x320 MOVT r3,#0x4800 // R3 = &GPIOC->BSRR main: // if (GPIOA->ODR & (1<<5)) LDR r1,[r0,#0x00] LSLS r1,r1,#26 ITE PL // GPIOA->BSRR = (1<<5) STRPL r12,[r0,#0x04] // *((volatile uint16_t *)&GPIOA->BSRR+1) = (1<<5); STRHMI r12,[r0,#0x06] // GPIOC->BSRR = (((1<<5)|(1<<8)|(1<<9)) << 16) | (~GPIOC->ODR & ((1<<5)|(1<<8)|(1<<9))); LDR r1,[r0,#0x800] AND r1,r1,#0x320 EORS r1,r1,r2 STR r1,[r3,#0x00] B main И никто в лужу не сел, как ни странно.