dlsh

Свой-

Постов

337 -

Зарегистрирован

-

Посещение

Весь контент dlsh

-

То что IP внешний и со стороны оператора все обеспечено для корректной работы устройства и ping в том числе указывают следующие факты. 1. TCP соединение на данный IP адрес устанавливаются с устройством и данные благополучно передаются. 2. При замене M660 на другой GSM модуль (EHS5, MG323B) в том же самом устройстве, после регистрации в сети оператора устройство нормально пингуется по данному IP адресу. Кроме того, была сделана попытка пинговать модулем M660 самого себя, подав команду AT+PING=31.13.149.182 в результате получили таймаут ожидания.... если поставить любой другой статический IP адрес в эту команду то пинги идут нормально. Если кто использует модем М660 в режиме сервера со статическим IP, сообщите работает ли пинг до вашего устройства.

-

Модуль в качестве сервера, ошибок в командах я не нашел. Лог команд дал ниже. Статический IP 31.13.149.182 *Лог от момента включения модема* Лог специфичный, в нем выведено без разделения и что посылается в модем и что принимается из модема. 001036 15:36:31.620 ..+EIND: 128.. 001037 15:36:31.732 ..+CALV: 0..PTS OK!.. 001038 15:36:32.690 ..+EUSIM: 1.. 001039 15:36:33.202 ..+STKPCI: 0,"D081C9810301250082028182050D8 001040 15:36:33.266 004110438043B04300439043D8F1C8080041104430434044C00 001041 15:36:33.329 20043D0430002004410432044F043704388F168180041C043E04 001042 15:36:33.393 39002004110438043B04300439043D8F108280041704300433044 001043 15:36:33.457 00443043704388F1A83800053004D0053002D043F043E0434043F 001044 15:36:33.521 04380441043A04388F0C848004170432043E043D04388F1E8580 001045 15:36:33.585 0053004D0053002D0437043D0430043A043E043C0441044204320 001046 15:36:33.648 4308F0E8680041F043E043C043E0449044C8F098A68616D656C656F6 001047 15:36:33.712 E1E02FFFF".. 001048 15:36:34.558 ..+EIND: 2.. 001049 15:36:35.293 ..+EIND: 1..AT.AT...OK.. 001050 15:36:35.357 AT+CPIN?.AT+CPIN?...+CPIN: READY....OK. 001051 15:36:35.421 .AT+CREG?.AT+CREG?...+CREG: 0,2.. 001052 15:36:35.485 ..OK.. 001053 15:36:39.461 AT+CREG?. 001054 15:36:39.541 AT+CREG?...+CREG: 0,2....OK.. 001055 15:36:43.565 AT+CREG?.AT+CREG?...+CREG: 0,1....O 001056 15:36:43.629 K..AT+CR=1.AT+CR=1...OK..A 001057 15:36:43.693 T+CRC=1.AT+CRC=1...OK..AT+CBST 001058 15:36:43.756 =71,,1.AT+CBST=71,,1...OK..AT+CP 001059 15:36:43.820 MS="SM","SM","SM". 001060 15:36:43.932 AT+CPMS="SM","SM","SM"...+CPMS: 0, 10, 0, 10, 0, 10. 001061 15:36:43.996 ...OK.. 001062 15:36:44.059 AT+CMGF=1.AT+CMGF=1...OK.. 001063 15:36:44.123 AT+CNMI=1,1.AT+CNMI=1,1...OK..A 001064 15:36:44.187 T+CLIP=0.AT+CLIP=0...OK..AT+CSQ 001065 15:36:44.251 .AT+CSQ...+CSQ: 13, 99....OK..AT+CG 001066 15:36:44.316 REG?.AT+CGREG?...+CGREG: 0,1....OK.. 001067 15:36:44.379 AT+NETAPN="static.beeline.ru 001068 15:36:44.443 ","beeline","beeline". 001069 15:36:44.587 AT+NETAPN="static.beeline.ru","beeline","beeline"...OK.. 001070 15:36:44.714 AT+CGDCONT=1,"IP","static.b 001071 15:36:44.778 eeline.ru".AT+CGDCONT=1,"IP","static.be 001072 15:36:44.842 eline.ru"...OK.. 001073 15:36:44.906 AT+XIIC=1.AT+XIIC=1...OK.. 001074 15:36:44.970 AT+XIIC?.AT+XIIC?...+XIIC: 0,0.0. 001075 15:36:45.033 0.0....OK.. 001076 15:36:49.058 AT+XIIC?.AT+XIIC?...+XIIC: 0,0.0 001077 15:36:49.122 .0.0....OK.. 001078 15:36:53.162 AT+XIIC?.AT+XIIC?...+XIIC: 0,0.0 001079 15:36:53.225 .0.0....OK.. 001080 15:36:57.250 AT+XIIC?.AT+XIIC?...+XIIC: 001081 15:36:57.314 0,0.0.0.0....OK.. 001082 15:37:01.402 AT+XIIC?.AT+XIIC?...+XIIC: 001083 15:37:01.465 0,0.0.0.0....OK.. 001084 15:37:05.506 AT+XIIC?.AT+XIIC?... 001085 15:37:05.570 +XIIC: 0,0.0.0.0....OK.. 001086 15:37:09.562 AT+XIIC?.AT+XIIC?...+XIIC: 0,0.0 001087 15:37:09.626 .0.0....OK.. 001088 15:37:13.666 AT+XIIC?.AT+XIIC?...+XIIC: 0,0.0. 001089 15:37:13.731 0.0....OK.. 001090 15:37:17.755 AT+XIIC?.AT+XIIC?...+XIIC: 001091 15:37:17.819 1,31.13.149.182....OK..AT+TCPCLOS 001092 15:37:17.883 E=0. 001093 15:37:17.947 AT+TCPCLOSE=0...+TCPCLOSE: ERROR..AT+A 001094 15:37:18.010 SCII=0.AT+ASCII=0...OK..AT+TCPL 001095 15:37:18.074 ISTEN=58598.AT+TCPLISTEN=58598...+TC 001096 15:37:18.138 PLISTEN:0,OK.. 001097 15:37:29.077 ..Connect AcceptSocket=0,ClientAddr=

-

Версия модема +CGMR: M660_1230_LQS13000_V018

-

Не проходит ping для модема GSM M660

dlsh опубликовал тема в Сотовая связь и ее приложения

Доброго времени суток. В устройстве установлен модем M660 и SIM карта со статическим IP. Устройство сконфигурировано в режиме прослушивания TCP порта, зарегистрировано в сети и соединение TCP при необходимости успешно устанавливается и данные идут. На ПУ Win пытаюсь пинговать модем чрез ping IP, где IP - статический адрес выделенный оператором под данную сим карту. Результат выполнения ping - превышение таймаута ожидания ответа. Пробовал разные настройки. Вопрос к тем кто работает с данным модулем. Были ли похожие проблемы и удалось ли их решить? -

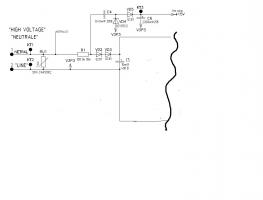

Уточню по приведенной схеме. Сам GSM модем подключен к цепи +12В и развязан от V3P3 на 4кВ трансформатором Т1. В варианте исполнения устройства с GSM модемом отсутствуют VD12, R69, C42, DA2, R64. Вместо DD2 поставили NCP1075. NCP1013 просто выключалась. VD7 убирали - никакого эффекта. V3P3,+12В пропадают одновременно. Возможно происходит срабатывания защиты в NCP1075, но что является причиной срабатывания не могу выяснить. Может ли VT1 открываться/закрываться под воздействием GSM сигнала? Может ли Т1 входить в насыщение от того же сигнала? Может ли сама DD2 под воздействием сигнала GSM входить в защиту? Если у кого есть источники собранные на подобных м/с. Попробуйте поднести антенну(источника GSM, телефон) в момент регистрации/звонка. Будет ли наблюдаться подобный эффект? Само устройство проходило испытания на воздействие внешнего высокочастотного поля 10 В/м в диапазоне от 0,1 до 1 ГГц. Подобного эффекта не наблюдалось. БП достаточно мощный для обеспечения работы GSM модема.

-

Доброго времени суток. Столкнулся со следующей проблемой. В устройстве при поднесении антенны GSM к месту расположения БП и в момент регистрации модема в сети происходит кратковременное пропадание выходного напряжения 3,3В (V3P3). Схем блока питания по ссылке. Пропадание питания V3P3 показано на рисунке. Включение через делитель 1/10. Кто нибудь сталкивался с подобными проявлениями?

-

Требуется Разработать Аналого-Цифровую Плату

dlsh ответил felex тема в Предлагаю работу

Здравствуйте У Вас личка не работает. Прошу указать контактные данные. С уважением Дмитрий -

Ответная часть для разъема PBD

dlsh ответил dlsh тема в Компоненты

Спасибо, буду смотреть/искать. -

Ответная часть для разъема PBD

dlsh опубликовал тема в Компоненты

Здравствуйте Ищу ответную часть для PBD разъема шаг 2,54 на картинки. При сочленении межплатное расстояние должно быть 14 мм. Нужно чтобы продавался в москве. Вроде такой был в буром медведе.. но не нашел. Если кто встречал, подскажите его название и где купить. -

Да все верно. Спасибо за схему просчитаем её на стоимость с другими номиналами и проверим на модели/макете.

-

Конденсатор обеспечивает питание для управления реле. В том и вопрос что поставить.... Естественно цена должна быть сопоставима с уже используемыми компонентами.

-

Заряд конденсатора до 12 от сети 220В

dlsh опубликовал тема в Силовая Преобразовательная Техника

Здравствуйте Используем схему Заряд С6.jpg для зарядки конденсатора С6 как на прикрепленном рисунке. Сетевое напряжение подается на точки 1 и 2. Данная схема всем устраивает кроме одного - реактивная энергия 6-7 Вар. Прошу помощи в модернизации схемы для того чтобы после заряда С6 схема отключала его. Общие требования Напряжение на С6 должно быть от 11 до 15В Время заряда не более 6 сек при напряжение сети от 160 до 265В Температура рабочая -40 ... +60 Внешнее потребление от С6 отсутствует. Среднее потребление от С5 ~1Вт Сделали схему Вариант 1 Заряд С6.jpg полностью устраивает по потреблению реактивной энергии, но не устраивает по времени. Отталкиваясь от данной схемы можно добиться 7 сек при крайних условиях. Если у кого есть решения и/или варианты, прошу поделиться. С уважением Дмитрий -

Разыскиваем Людей в Нижни Новгород

dlsh ответил MIkler тема в Предлагаю работу

Здравствуйте Отправил сообщение. -

Обращаюсь к знатокам VHDL

dlsh ответил Garik тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. Для создания кода по расчету КС использую ресурс http://outputlogic.com/?page_id=321 -

Здравствуйте Есть ли у вас оборудование для калибровки/поверки подобных приборов? п.с. Возможно речь идет об узле прибора РЗА.

-

Для уточнения деталей обратитесь к Блохин Юрий Васильевич +7 (495) 4379906 Москва, Озёрная, 46 стоимость работ в безэховой камере у них 10тыр в час. Если вам не подойдет условия/параметры существующего оборудования думаю он сможет сказать организации/людей которые помогут вам с данными видами работ.

-

была ошибка в схеме, потому и не поднимался линк на 1Гбит. все заработало на раз, после коррекции. всем спасибо

-

Приветствую всех. Добился что phy подключается и к ПК и к медиаконвертеру. Не как не могу запустить езернет на 1Гбит. подключил tse в этой части таким образом // -- Ethernet .reset_tse_reset_n(reset_n_tse), .tse_export_rx_control (eth_hrd.NET0_RX_DV), // tse_mac_conduit.rx_control .tse_export_rx_clk (eth_hrd.NET0_RX_CLK), // .rx_clk .tse_export_tx_control (eth_hrd.NET0_TX_EN), // .tx_control .................. .tse_export_ena_10 (ena_10), // .ena_10 .tse_export_eth_mode (eth_mode), // .eth_mode ................ .tse_export_set_10 (1'b0), // .set_10 .tse_export_set_1000 (1'b1), сигнал tse_export_eth_mode устанавливается в 1, т.е. 125МГц но все одно phy спускается на 100Мбит. если dawnshift запретит то линк вообще не поднимается. Перекопал форум по данному вопросу. Что можно еще посмотреть в части запуска линка на 1Гбит?

-

Здравствуйте. возник вот какая проблема с использованием PHY_88E1111 + MAC_tse + Nios. В ниосе проект от уважаемого vadimzzz. Когда подключаешся к сети то все нормально все пакеты ходят взад вперед, все работает, лампочки усердно мигают . Собственно так проект и отладили до конца через общественную сеть. Сложность возникла когда стали использовать Media Converter 10/100/1000Base-T to 1000Base-X. Есть два конвертера, когда делаешь связку общественная сеть --- КонвертерА --- оптика --- КонвертерВ -- ПК то все работает как положено, все линки есть и сеть работает. А вот когда подключаешь прибор например к КонвертеруА( или Б) то лампочки на конвертере горит только PWR и иного мигает FDX (по описанию это означает коллизия). На плате прибора тоже все лампочки гаснут и иного мигает лампочка Duplex как сказано в описание тоже означает что коллизия. ни какое шаманство с регистрами не поменяло состояние. Еще заметил что часто бывает что первое чтение после программного сброса возвращает нормальные записи в реситрах, а последующие чтения рестров возвращают всегда фффф. При просмотре сигналов видно что действительно марвел не отвчает по шине мдио/млс. при подключении прибора к ПК на прямую прямым кабелем светодиоды маргают что линк есть, но данные идут странные вот когда связь есть т.е. общественная сеть http://gyazo.com/05d003d967dae4be0368f02ece9c225d а вот когда анпрямую к ПК http://gyazo.com/114e94aa45b6d8446475cd91f440cf26 видно что потерялась преамбула я так понимаю что марвел должен был автоматом поменять полярность.. или что то нужно еще сделать чтобы это произошло? вот рисунок дампа регистров взятых и марвела http://gyazo.com/ac80ec5b599128cc1efa4ab7eabe9288 здесь показан дамп регистров когда прибор подключен к сети и с линком все нормально http://gyazo.com/c04829de874a1f808321ff8f5d146e03 документация на конвертер http://gyazo.com/d313c01d2734b09e4c8329fceed85d16 http://gyazo.com/4c2a277e89eec85bf7ba3d7974a13a04 фотка конвертера при подключении его к прибору http://gyazo.com/63121c90c10225904d2e760dbd4445a6 вот код подключения модуля module DevEthernet( // Clock input CLOCK_50, // reset input reset_n, // Ethernet output NET0_GTX_CLK, output NET0_MDC, inout NET0_MDIO, output NET0_RESET_N, input NET0_RX_CLK, input [3: 0] NET0_RX_DATA, input NET0_RX_DV, output [3: 0] NET0_TX_DATA, output NET0_TX_EN ); wire sys_clk, clk_125, clk_25, clk_2p5, clk_200, tx_clk; wire core_reset_n; wire mdc, mdio_in, mdio_oen, mdio_out; wire eth_mode, ena_10; // -- wire udp_stack_fifo_start_to_ethernet; // udp_stack_fifo.start_to_ethernet wire [7:0] udp_stack_fifo_rd_data; // .rd_data wire udp_stack_fifo_rdreq; // .rdreq wire udp_stack_fifo_rdempty; // .rdempty wire [10:0] udp_stack_fifo_rdusedw; // .rdusedw wire [7:0] udp_stack_fifo_wr_data; // .wr_data wire udp_stack_fifo_wrreq; // .wrreq wire udp_stack_fifo_wrfull; // .wrfull wire udp_stack_eth_cntrl_export; // udp_stack_eth_cntrl.export assign mdio_in = NET0_MDIO; assign NET0_MDC = mdc; assign NET0_MDIO = mdio_oen ? 1'bz : mdio_out; assign NET0_RESET_N = core_reset_n & udp_stack_eth_cntrl_export; assign udp_stack_fifo_start_to_ethernet = 1'b0; assign udp_stack_fifo_rdreq = 1'b0; assign udp_stack_fifo_wr_data = 8'h00; assign udp_stack_fifo_wrreq = 1'b0; pll pll_inst( .areset(~reset_n), .inclk0(CLOCK_50), .c0(sys_clk), .c1(clk_125), .c2(clk_25), .c3(clk_2p5), .c4(clk_200), .locked(core_reset_n) ); assign tx_clk = eth_mode ? clk_125 : // GbE Mode = 125MHz clock ena_10 ? clk_2p5 : // 10Mb Mode = 2.5MHz clock clk_25; // 100Mb Mode = 25 MHz clock ddio_out ddio_out_inst( .datain_h(1'b1), .datain_l(1'b0), .outclock(tx_clk), .dataout(NET0_GTX_CLK) ); nios_system system_inst( .clk_clk (sys_clk), // clk.clk .reset_reset_n (core_reset_n), // reset.reset_n .reset_tse_reset_n (udp_stack_eth_cntrl_export), .tse_export_rx_control (NET0_RX_DV), // tse_mac_conduit.rx_control .tse_export_rx_clk (NET0_RX_CLK), // .rx_clk .tse_export_tx_control (NET0_TX_EN), // .tx_control .tse_export_tx_clk (tx_clk), // .tx_clk .tse_export_rgmii_out (NET0_TX_DATA), // .rgmii_out .tse_export_rgmii_in (NET0_RX_DATA), // .rgmii_in .tse_export_ena_10 (ena_10), // .ena_10 .tse_export_eth_mode (eth_mode), // .eth_mode .tse_export_mdio_in (mdio_in), // .mdio_in .tse_export_mdio_out (mdio_out), // .mdio_out .tse_export_mdc (mdc), // .mdc .tse_export_mdio_oen (mdio_oen), // .mdio_oen // -- .udp_stack_fifo_start_to_ethernet(udp_stack_fifo_start_to_ethernet), // udp_stack_fifo.start_to_ethernet .udp_stack_fifo_rd_data(udp_stack_fifo_rd_data), // .rd_data .udp_stack_fifo_rdreq(udp_stack_fifo_rdreq), // .rdreq .udp_stack_fifo_rdempty(udp_stack_fifo_rdempty), // .rdempty .udp_stack_fifo_rdusedw(udp_stack_fifo_rdusedw), // .rdusedw .udp_stack_fifo_wr_data(udp_stack_fifo_wr_data), // .wr_data .udp_stack_fifo_wrreq(udp_stack_fifo_wrreq), // .wrreq .udp_stack_fifo_wrfull(udp_stack_fifo_wrfull), // .wrfull .udp_stack_eth_cntrl_export(udp_stack_eth_cntrl_export) // udp_stack_eth_cntrl.export ); endmodule вот код инициализации IOWR_ALTERA_TSEMAC_MDIO_ADDR0(TSE_BASE, PHY); t2 = IORD_ALTERA_TSEMAC_MDIO(TSE_BASE,0,0x1B);//Extended PHY Specific Status Register t2 &= 0xFFF0; IOWR_ALTERA_TSEMAC_MDIO(TSE_BASE,0,0x1B,t2|0xB);//RGMII to Copper t2 = IORD_ALTERA_TSEMAC_MDIO(TSE_BASE,0,0x14);//Extended PHY Specific Control Register IOWR_ALTERA_TSEMAC_MDIO(TSE_BASE,0,0x14,t2|0x82);//Add Delay to RX_CLK for RXD Outputs; Add Delay to GTX_CLK for TXD Inputs t2 = IORD_ALTERA_TSEMAC_MDIO(TSE_BASE,0,ALTERA_TSEMAC_PHY_ADDR_CONTROL); IOWR_ALTERA_TSEMAC_MDIO(TSE_BASE, 0, ALTERA_TSEMAC_PHY_ADDR_CONTROL, t2 | PCS_CTL_sw_reset);//Previous Operations Require SW Reset do { for(i = 0; i < sizeof(reg_phy); i++){ reg_phy[i] = IORD_ALTERA_TSEMAC_MDIO(TSE_BASE, 0, i); } t2 = IORD_ALTERA_TSEMAC_MDIO(TSE_BASE,0,ALTERA_TSEMAC_PHY_ADDR_STATUS); } не могу понять куда дальше копать, в чем проблема что марвел не хочет подключится к прибору? Как/чем можно посмотреть почему phy не поднял линк?

-

Москва, нужен программатор и софт к нему

dlsh ответил priboy_095 тема в Предлагаю работу

Здравствуйте. Стоимость по первому варианту это 100 - 200 тыр. Срок 1-3 месяца. конечная стоимость будет определяться дополнительными требованиями со стороны заказчика в ходе проработки вопросов связанных с функционированием устройства, условиями/алгоритмом приемки разработанного устройства, сроками требуемыми со стороны заказчика. С уважением Дмитрий -

Москва, нужен программатор и софт к нему

dlsh ответил priboy_095 тема в Предлагаю работу

Здравствуйте. Стоимость сильно зависит от вариантов 1. Требуется получить только программатор + софт обеспечивающие описанный алгоритм + техническая поддержка 2. Если требуется получить исходники от п.1, цена сразу станет 2-3 порядка выше чем в п.1 Прошу Вас сообщить какой вариант для вас приемлем. С уважением Дмитрий -

Есть работа в Самаре инженеру-разработчику ПЛИС

dlsh ответил Skbsv тема в Предлагаю работу

Здравствуйте Сергей Самарский. Прошу Вас указать почту и/или другой электронный адрес для связи. через сайт http://www.skbsv.ru/ не удалось отправить письмо. Отправил вам письмо через "Контактная информация" в вашем профиле. С уважением Дмитрий -

Активная/реактивная энергия

dlsh ответил AndreyVN тема в Математика и Физика

первая ссылка гугла http://ru.wikipedia.org/wiki/Электрическая_мощность одной из основных задач счетчиков электрической энергии является именно разделение активной/реактивной по прямой/обратной. если не секрет а какую цель вы преследуете пытаясь складывать данные мощности/энергии? -

Опечаленный студент

dlsh ответил leon13rus тема в Предлагаю работу

Приветствую всех. Прошу Вас уточнить. В данной теме созданной топикстартером вы в качестве кого участвуете - представитель работодателя или исполнитель данной работы? С уважением Дмитрий -

Опечаленный студент

dlsh ответил leon13rus тема в Предлагаю работу

Здравствуйте. На запрос с вашей стороны, мною был дан ответ в котором озвучена стоимость и сроки проведения работы. Те условия которые были выдвинуты Вам и на которые вы согласились (утверждения согласились мое предположение, прошу поправить если я ошибаюсь), отношения к озвученной мною суммы и срокам оно не имеет никакого отношения. да, все так. С уважением Дмитрий