dlsh

Свой-

Постов

341 -

Зарегистрирован

-

Посещение

Весь контент dlsh

-

Также интересен данный вопрос. Если кто знает прошу подсказать рабочий путь экспорта/импорта AD <-> Quartus Prime. Что удалось накопать самому. Есть подробное описания от AD каким образом они видят этот процесс. Может кто видел плагин для конвертации форматов между данными ПО. Однако либо они его не проверяли или что то не так. В чем суть проблемы. AD делает экспорт информации через Pin Mapper в *.csv файл с заголовками Pin Designator,Net Name,Display Name,IO Bank,IO Standard,Slew Rate,Drive Strength,IO Pin,Vref Pin,CLK Pin,Config Pin,Special Pin,Group,Differential Pair Pin Designator,Net Name,Display Name,IO Bank,IO Standard,Slew Rate,Drive Strength,IO Pin,Vref Pin,CLK Pin,Config Pin,Special Pin,Group,Differential Pair где Pin Designator - номера пинов вида 1,2,3... Net Name - имея подключенной цепи в AD. Quartus -> Pin Planner, на сколько я понял, умеет только экспортировать пины в *.csv файл с заголовками, а импортировать он не может. To,Direction,Location,I/O Bank,VREF Group,Fitter Location,I/O Standard,Reserved,Current Strength,Slew Rate,Differential Pair,Strict Preservation,Special Function,Live I/O Check Error где To - наименование цепи, Direction - Input/Output/Bidir Fitter Location - пины вида PIN_1, PIN_2, PIN_3 .... Очевидно что AD при попытке подсунуть ему файл из Pin Planner выдает ошибку и не понимает. В сам Quartus можно загрузить через Assignment Editor пины через *.csv файл, НО формат там свой, а именно To,Assignment Name,Value где To - наименование цепи, Assignment Name - Location Value - PIN_1, PIN_2 ... Вырисовывается запутанная картина требующая плагины переконвертации одного формата в другой с использованием, как я понимаю, некого словаря перекодирования как заголовков таблиц так и соответствие наименований цепей. В общем, если у кого есть workflow то прошу указать. А каким образом вы автоматизируете этот процесс?

-

По OpenOCD чего достиг: Скачал OpenOCD-20200729-0.10.0, запустил openocd.exe -f .\..\share\openocd\scripts\interface\stlink-v2.cfg -f .\..\share\openocd\scripts\target\stm32f7x.cfg -c "init;" Подключаюсь telnet telnet localhost 4444 пытаюсь включить логер tpiu config internal "D:\Documents\Project\log.txt" uart off 216000000 itm port 0 1 В ответ все тихо, никаких ошибок, но файл "D:\Documents\Project\log.txt" не создается... Хотя команда reset работает... Как бы его запустить этот логер.

-

Подниму тему. Необходимо вести лог с вывода SWO через J-Link(или ST-Link) в файл. J-Link SWO Viewer (Serial Wire Viewer) работают, но не понятно сколько по времени они могут вести логирование (нужно хотя бы сутки - размер текстового лога при этом оценивается как 100-200 МБайт). bragswv.exe - вылетает с ошибкой. SWOAnalyzer.exe - сохраняет какую то статистику, но самих логов нет. На хабре нашел статью вывод логов через tpiu, но запустить на windows 10 не смог. Вроде простейшая задача, но решения в легкую не находиться. Поделитесь кто находил решение по записи лога в файл с SWO. (Подключить USB-UART к SWO нет возможности, есть ST-Link/J-Link).

-

Тоже так думал, однако Keil считает иначе. void *malloc( size_t sizemem ) __attribute__((malloc)){ .... } ../../Source/main.c(547): warning: GCC does not allow 'malloc' attribute in this position on a function definition [-Wgcc-compat] void * malloc( size_t sizemem ) __attribute__((malloc)){ ^ 3 warnings generated. compiling main.c... linking... .\STM32F777\STM32F777.axf: Error: L6200E: Symbol malloc multiply defined (by lto-llvm-bde691.o and malloc.o). /////////////////////////////////////////////////////////////////////////////////////////////////// void *MyMalloc( size_t sizemem ) __attribute__((malloc)){ .... } ../../Source/main.c(547): warning: GCC does not allow 'malloc' attribute in this position on a function definition [-Wgcc-compat] void *MyMalloc( size_t sizemem ) __attribute__((malloc)){ ^

-

Доброе время суток. Собственно нужно указать линкеру использовать вместо библиотечной функции malloc (из lto-llvm-aeb2e5) собственный планировщик динамический памяти. В IAR это делается в опция линкера как --redirect malloc=MyMalloc А как также пояснить в Keil MDK-ARM ?

-

Так и сделаю в понедельник, сегодня пятница - технолога нет, отдыхает. Здесь вся и соль, что мне нужно включить её как деталь, т.к. в только в этом случае идет автоматический расчет количества провода из AD в спецификацию. Добиваюсь некой автоматизации процесса создания КД по ЕСКД из проекта Altium Designer с минимальным инженерным участием. Как только это переводиться в материалы, то подсчет количества сразу теряется.

-

Конечно станет. Согласно ГОСТ 2.109-73 п.2.1.а чертеж не выпускают, а вместо этого согласно ГОСТ 2.106-2019 п.4.2.17.1 третий абзац и п.4.2.17.5 второй абзац в спецификации в разделе "Детали" указывают материал и параметры для изготовления. Да, спасибо я про это и спрашиваю, по какой причине перенос одного и того же по сути в разные разделы (Деталь/Материалы) спецификации на ПП согласно ЕСКД ведет к удорожанию производства. Т.о. имеем 1. Для детали необходима расценка в нормочасах; 2. Для детали должна быть сдача в ОТК... хотя здесь вопрос открытый т.к. в ОТК сдается изделие собранное по чертежу, а т.к. чертежа нет, то и сдается собранная плата целиком (т.к. только на неё и есть чертеж). Может кто накинет еще хоть пару причин почему перенос провода из материалов в детали вызовет удорожание/усложнение производства/производственного процесса. Буду признателен.

-

Вот это и странно что материал. Согласно ГОСТ 2.101-2016 п.5.1.2 строго цитата "Деталь - ... отрезок провода заданной длинны....". А вот что касается термина "материал" то в ГОСТах вообще ни одной строгой трактовки нет. >> Если есть жесткие требований к углам изгибам и длинам, то это деталь, т.е. отдельный чертеж, ОТК и т.д. то то и оно, что достаточно указать длину и провод сразу станет деталью. Собственно с чего все началось. В AD достаточно создать компонент провода и далее последующие документы СП получается автоматически. Если жестко затребовать чтобы провод стал Материалом, то автоматизация теряется и приходится вручную считать сколько требуется этого провода... А нужен ли запас по данному материалу?

-

Доброе время суток. Камнем преткновения по согласованию спецификации на ПП встал вопрос куда поместить два провода соединяющие выводы компонентов длинной 10 мм 0,07 мм^2. Первоначально оформил как деталь БЧ указав тип, длину L = 10 мм и количество в разделе Деталь СП на ПП. У н.к. вопросов нет. В процессе согласования документ дошел до самого верха и потребовали перенести его в раздел материалы объясняя это технологической сложностью (оформление норма/часов на деталь и чего то там еще). Кто куда относит подобные вещи в какой раздел ? А что по этому поводу говорит ЕСКД есть ли преимущестнво материалов над деталями? Ответа сам пока не нашел.

-

Draftsman

dlsh ответил inter_pro тема в Altium Designer, DXP, Protel

Добрый день. В моем случае на сколько помню оказалось важным порядок размещения графики (типа графики) и вида. Сначала разместил вид, затем размещал геометрию определенного типа. Причем что было странно. Если рисовал графику типа окружность, то вид перекрывал графику. В случаи выбора графики типа линия то линии перекрывали вид. С выносками имхо важно только порядок, а именно сначала вид затем добавлять выноски. По моим впечатлениям от работы с draftsman, пакет не доработан, очень ресурсоемкий (особенно по памяти). Вероятно его будут постепенно допиливать. -

Спасибо, хороший вариант, мне нравится - так попробую сделать.

-

2018 Вопросы начинающих

dlsh ответил Sanchosd тема в Altium Designer, DXP, Protel

Да, конечно. Это pads, не via. Продолжил бы изыскания с изометрией в Draftsman, но компьютер не позволяет по памяти (стоит всего 8 ГБ) - как только делаю Import можно отдыхать минут 5. -

Решение прямолинейное и самое простое, хочется оставить А3. Если не найду/не договорюсь с нк то видимо так и придется делать. Предложенное решение понятно, сложность в обосновании только возникнет т.к. в области действия ГОСТ 2.601-2019 строго записано ЭД. Есть еще вполне стройный вариант - нумеровать рисунки на каждой странице свой номер рисунка. Т.о. Лист 1 - Рис.1 Лист 2 - Рис.2 Лист 3 - Рис.3 (остальное см. Рис.1, 2.) И в таблице исполнений в графе Рис. указывать 1,2 вместо 1.

-

Рисунок 1 на двух листах в групповом сборочном чертеже на ПП

dlsh опубликовал тема в Документация

Возник такой момент. Сделал групповой сборочный черетеж на ПП, но так получилось что Рис.1 размещен на двух листах А3. Вопрос собственно как обозначить на втором листе что это продолжение Рис.1. Структура документа такая - на первом листе Рис.1, на втором листе продолжение Рис.1, на третьем листе Рис.2. Как офоромить лист 2? Рис.1 (продолжение) Или на втором листе вообще не указывать рисунок, и так понятно что это относиться к Рис.1 раз ничего не указано. В ГОСТ 2.113-75 на этот счет ничего нету. -

2018 Вопросы начинающих

dlsh ответил Sanchosd тема в Altium Designer, DXP, Protel

Доброе времени суток. AD20 вопрос по Board Isometric View (Draftsman). На данном виде не отображаются металлизированные отверстия - совсем. Если на плате ставить отверстия с отсутствием металлизации - то они появляются на данном виде. Нет ли где настройки аналогичной виду Board of assembly view где можно указать минимальный диаметр после которого отверстия не отображаются? В плате необходимо крепежные отверстия сделать металлизированные и они на изометрии не отобразились. Кто как выходит из этой ситуации? -

Доброе время суток. Необходимо создать таблицу вариантов исполнения для Э3 Каким образом в графах таблицы вместо текста, вывести параметр нужно мне компонента? Пробовал =XP1.Value =XP1::Value

-

Altium Designer 20

dlsh ответил toshas тема в Altium Designer, DXP, Protel

В 20.1.7 у меня такая же ошибка появлялась, хотя в окне Message сообщение - успешно. -

Что делать с лишними элементами на схеме?

dlsh ответил kipmaster тема в Документация

Столкнулся с аналогичной ситуацией. Можете поделиться опытом в части ссылок на ГОСТ/аргументы почему в данном случае поле "Наименование" остается пустым, а не вписывается наименование элемента. ГОСТ 2.701-2008 п.5.7.2 рекомендует для ПЭ3 в "Примечание" указывать тех.данные элемента, какие у вас были аргументы для н.к. в части записи "не устанавливается"? На схеме около элемента который "не устанавливается" при этом можно указывать тип/номинал? Можно конечно притянуть сюда ГОСТ 2.701-2008 п.5.7.7 Примечание 4 - но полного соответствие ситуации описанной в данном пункте и обсуждаемой как таковой нету. -

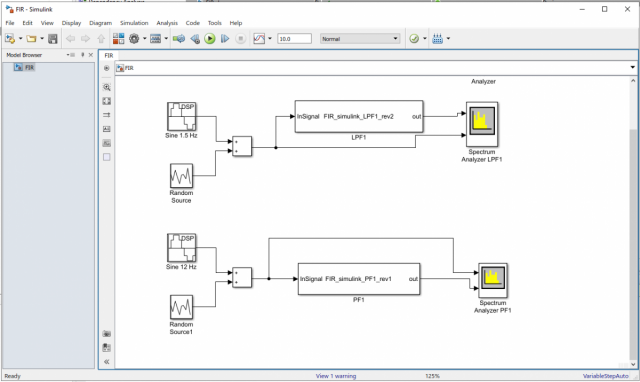

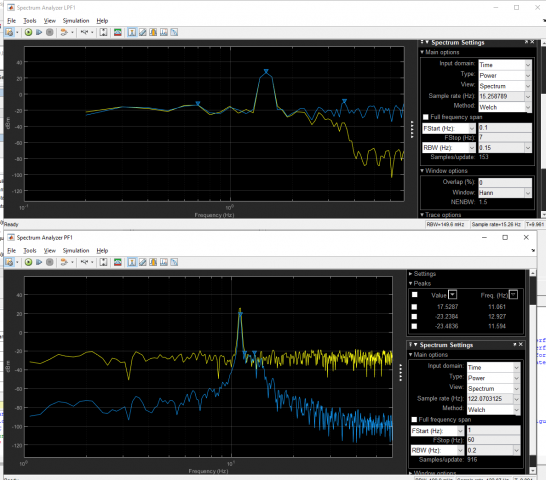

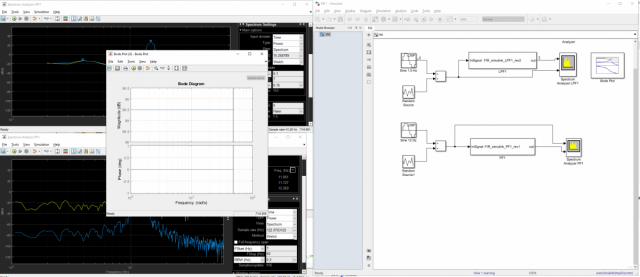

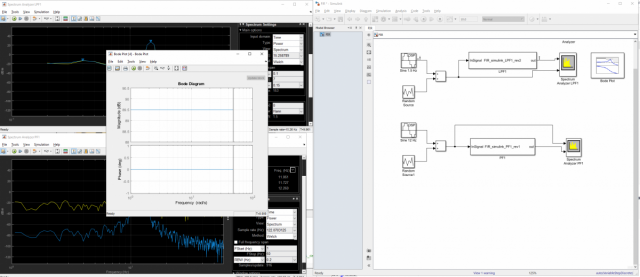

fvtool

dlsh ответил lennox тема в Вопросы системного уровня проектирования

Так и не разобрался каким образом подать дельта функцию для получения ИХ. Решил пойти другим путем. В Simulinke сделал блок фильтра - указав в качестве его реализации .с/.h файлы. Подключил к фильтру синусоидальный сигнал+шум, а к выходу спектроанализатор. В результате получил на каждый фильтр два спектра Здесь есть непонятный момент связанный с установкой параметра RBW спектроанализатора, при значении RBW < 0.15 Гц - график не строится. Далее решил получить АЦХ данного фильтра. Выбрал LPF1, задал вх/вых (Input Perturbation/Output Measurement) и добавил Simulink Control Disign->Linear Analysis Plots->Bode Plot для снятия АФЧХ. Однако результата нет, ошибок тоже. Возможно это связано с дискретностью источника сигнала и/или настройки нужно задать верные - так и не разобрался. Собственно вопрос как можно построить АЧХ данной модели? В какую сторон здесь надо копать? Проект FIR_v1.zip прикрепил. FIR_v1.zip -

fvtool

dlsh ответил lennox тема в Вопросы системного уровня проектирования

Доброе времени суток коллеги. Есть вопрос связанный с применением fvtool для верификации своего алгоритма реализации фильтра на С. Написал алгоритм реализации КИХ фильтра на С в виде функции принимающая один аргумент в качестве входного отсчета данных с АЦП и возвращающий значение с выхода фильтра. Коэффициенты взяты из Filter Designer. Код реализация на С через mex конвертируется в функцию матлаб. Есть желание отобразить в fvtool АЧХ моего алгоритма. Каким образом это можно реализовать? Есть примеры где можно это посмотреть? -

А при этом вы какую емкость ставили в обвязку XT2? Или не ставили вообще?

-

Интересно, а можете указать модель кварца SJK поточнее что применяется у вас?

-

Altium Designer - Specctra

dlsh ответил nicaraguanec тема в Altium Designer, DXP, Protel

length_amplitude - это еще один из параметров задаваемый для всей платы, самое начало генерируемого dsn файла выглядит так Здесь видимо не само погружение в спектру (хотя это тоже важно), а каким образом и по какому алгоритму формируются правила Altium при генерации правил зазоров для спектры. -

Altium Designer - Specctra

dlsh ответил nicaraguanec тема в Altium Designer, DXP, Protel

Методом проб выяснил что правило для всего проекта типа (rule (length_amplitude 200 20) (width 31.4961) (clearance 78.7402) (reorder starburst) ) в части clearance генерируется исходя из максимального!!! значения clearance из группы правил Electrical->Clearance. Спрашивается и каким образом задать правила для всего проекта тогда? Или это что придется все цепи заводить в какой то общий класс и для него описывать свои правила? Кто как делает? -

Altium Designer - Specctra

dlsh ответил nicaraguanec тема в Altium Designer, DXP, Protel

Добрый день. Осваиваю связку Altium 20.1.7 - Specctra v16.6 столкнулся с рядом непонятных моментов. В созданном алтиумом файле project.dsn присутствует правила для всей платы Не могу понять - где данные правила задаются в Altiume. Более менее подходящий вариант это Design->Rules->Electrical->Clearance но там задан зазор в 0,3 мм Рисунок. Также не понятно почему для TopLayer/BottomLayer задается ширина в dsn файле как 0,3мм, а для MidLayer1 не задается ? Хотя в Altiume ширина задана для всех слоев Рисунок Где/как задаются/считаются эти правила?