-

Постов

4 564 -

Зарегистрирован

-

Посещение

-

Победитель дней

14

Весь контент dxp

-

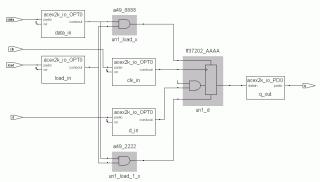

Я не сторонник асинхронного дизайна в ПЛИС, и делать асинхронную загрузку в процессе работы никому бы не рекомендовал. Но при начальной инициализации этот подход, имхо, вполне оправдан - сам так всегда делаю. Правда, там у меня значения загрузки обычно определены - 0 либо 1. Главная причина, побуждающая использовать асинхронную установку - разгрузить рабочую логику. Что касается обсуждаемого описания, то все прекрасно синтезируется. Например, на альтеровском Циклоне. См картинку. Блокирующее присваивание при описании синхронной логики - bad style. Не надо так делать.

-

Что-то не понял, что Вам не понравилось в приведенном описании? Покажите, как привильно с Вашей точки зрения это должно выглядеть - а именно: триггер с асинхронной установкой.

-

Что лучше взять для AVR?

dxp ответил High Voltage тема в AVR

Так и не используйте его оболочку. У ИАРа главное - компилятор. А редактор лучше внешний взять. Который все это (и многое другое) умеет. -

Помогите разобраться....

dxp ответил Kyle тема в Altium Designer, DXP, Protel

При начале трассировки убедитесь, что текущие единицы - mil, а не мм. :) Должно работать. А исправляется это путем изменения в региональных настройках знака разделителя целой и дробной части. Измените ',' на '.', и проблема уйдет. -

В CCS есть утилита для конвертации .out->.hex Называется dsphex.exe Утилита называется hex2000.exe. Входит в состав CCS. Для этого существует утилита cgtools\bin\hex2000.exe. Почитайте описание, разберетесь. Размещение в памяти полностью управляется скриптом линкера - который .cmd файл. Для того, чтобы фукнция работала из ОЗУ, надо поместить ее в отдельный сегмент, а сегмент этот скопировать на этапе инициализации из флеши в ОЗУ. Все это можно посмотреть в примерах по конфигурации флеши. Кстати, реальная работа из флеши не в пять раз медленнее. Если включить конвейер флеши, то скорость значительно возрастает и составляет на линейных участках примерно 90-100 МИПС при 150 МГц тактовой.

-

:) Так все же подходят такие дроссели для фильров пульсаций питания или нет? Или есть что-нито более подходящее по каким-то параметрам? Что посоветуете?

-

IMHO, не менее главное отличие ещё и отсутствие почти всех основных средств, предоставляемых C++. "Спору нет вещица забавная, цены немалой", однако вобще зачем понадобилось исключать из него например namespaces или templates непонятно. С таким компилятором на C++ че-то делать особого смысла нет, ну разве что использовать inline и объявление переменной в любом месте, где допустим оператор. ЕС++ не имеет никакого отношения к специфике AVR. Это просто урезанный С++, в нем нет шаблонов, пространств имен, множественного наследования, информации о типе на рантайме, поддержки исключений и поддержки нового синтаксиса кастов. Из полезного - есть основная фича С++ - классы. Инлайны, как раз, до кучи. Кстати, в версиях EWAVR 4.xx введена поддержка шаблонов, неймспейсов, новых кастов, т.ч. получается есть почти все, что нужно - RTTI и исключения на AVR уж точно не нужны. Множественное наследование, возможно было бы не лишним, но, имхо, его отсутствие совершенно не мешает жить.

-

Да не придется ничего вводить при правильном выборе материала и сечения кольца. Кстати, а -что это? CDRH - это серия дросселей от Sumida. Предназначены для использования со step-up/down DC/DC преобразователями типа MAX1685/TPS62xxx. Констуктивно представляют собой обмотку на ферритовом сердечнике, помещенном в ферритовую же оболочку так, что между сердечником и самой оболочкой имеется небольшой зазор. Посмотреть можно тут. Т.е. относится к силовым дросселям, не к фильтровым. Вопрос был, насколько такие дросселя адекватны в качестве фильтров питания (пульсации давить после тех же DC/DC). Может есть что более подходящее?

-

Да нет, не он враг. Враг это собственно частота переключения и кол-во переключаемых гейтов. А на сколько там все синхронно, на жрачку не влияет. А когда клок щелкает, он же, по идее, тоже перезаряжает входные емкости элементов, на которые заведен. И если таких элементов много (в синхронном дизайне их больше, чем в асинхронном), то это тоже должно вылиться в потребление. Или нет? Или на фоне общего количества элементов число этих элементов (входы которых дергает клок) мало?

-

рекомендации по использованию FreeRTOS

dxp ответил sergik_vrn тема в FreeRTOS

В ресурсах и смысл :-(. Например, телефонная станция - сотни-десятки тысяч абонентов. Процессы обслуживания одного абонента более, чем просты, не требуют много ресурсов но их МНОГО. Кроме этих естественно есть и другие, серьезные. С вытясняющей весь пар уйдет в свисток и ляжет любая система. Это что ж, на каждого абонента отдельный процесс? Зачем? Вытесняющая ОС имеет главное преимущество - детерминированное время отклика на событие. Если все абоненты равнозначны по приоритету - то их и должен обслуживать один процесс. Если есть разные группы абонентов - например, есть группа VIP, которая должна быть обслужена вперед других, то ее обслуживание поместить в другой процесс с более высоким приоритетом. Только и всего. В общем, при использовании RTOS тоже ведь надо думать и грамотно проектировать систему. В этом случае все прекрасно ложится, ничего "в свисток" не уходит. -

Перспективы микроконтроллеров

dxp ответил micro51 тема в Все остальные микроконтроллеры

Извините, пожалуйста, не хочу показаться грубым, но что Вы предлагаете? Просто молчать, когда несут совершенную чушь (и при этом настаивают на ней)? Можно и так поступить. Оно, может, и тише будет. Только вот почитает это какой-нибудь начинающей разработчик, "неокрепшая душа" и будет думать, что все МК - это которые имеют разрядность менее 32 бит. И что даже есть некая классификация, "официально" утверждающая такую позицию. Что ж в этом хорошего и правильного? Характер высказываний тут скорее обусловлен не столько личностями авторов, сколько безапелляционными, безосновательными и, мягко говоря, не верными высказываниями одного из участников. Кстати, к слову, в некоторых фидошных эхах, к примеру, есть правило, по которому модератор может накладывать взыскание на подписчика, если тот пишет очевидные глупости. Насчет переноса в формум "Общение" - оно, может, и правильно. -

Перспективы микроконтроллеров

dxp ответил micro51 тема в Все остальные микроконтроллеры

Уважаемый Charley! Вы продолжаете тяжело бредить, хотя уже не на тему MCS-51, а просто на тему МК. Еще разок (хотя уже Вам объясняли, что-такое МК): микроконтроллером называется дивайс, в котором совмещается процессороное ядро, память и периферия, делая такое устройство законченной однокристальной ЭВМ. Разрядность к этому не имеет вообще никакого отношения. На всякий случай подумайте, а LPCxxx - это DSP или специализированный процессор (и какая у него специализация, и чем она отличается от специализации АВР, ПИК, МСП430, 51-х и прочих). Еще неплохо было бы объяснить, что это за такая существующая классификация микроконтроллеров, откуда она взялась, кто автор. Уж не Вы ли? Да что Вы говорите!!? А я-то и не знал, что там дока-то есть. Как начал работать полтора года назад с ними, так и не знал до сего момента, а вся инфа, необходимая для работы, мне, не иначе, свыше по телепатическому каналу в голову пришла. Во время медитации. В заключение, если Вы не поняли (а Вы не поняли), хочу сказать, что вопрос этот (в известной степени риторический) я задал с намеком, что сегодня грань между МК и DSP постепенно стирается. TMS320F28xx - это МК, у которого ядро содержит фичи DSP (много шин, позволяющих грузить операнды в параллель, развитая косвенная адресация, умножитель-аккумулятор, толстый шифтер, поддержка циклических буферов и т.д.). Но по сути он все равно МК. Кроме этого МК существуют и другие варианты, вроде черного фина, но я специально не стал его упоминать, т.к. там граница между МК и DSP более сдвинута в сторону процессора, хотя этот дивайс все равно вполне тянет на МК. -

Перспективы микроконтроллеров

dxp ответил micro51 тема в Все остальные микроконтроллеры

DSP однако.... :) Как же так? А встроенный АЦП с мультиплексором на 8 и двумя схемами выборки-хранения, а два UART'а, а SPI, а куча таймеров с функциями формирования ШИМ с мертвыми зонами и без, с функциями Compare/Capture, а полста ног на вво-вывод, каждая из которых может быть настроена индивидуально, а набортная флешь? Законченная однокристальная ЭВМ - то бишь микроконтроллер. Процессорное ядро + богатая периферия. Дык как же оно на самомт деле? :) -

Перспективы микроконтроллеров

dxp ответил micro51 тема в Все остальные микроконтроллеры

А вот интересно, TMS320F28xx - это МК или DSP? :) -

Цифровое, Аналогове питание

dxp ответил Muxamor тема в Силовая Преобразовательная Техника

Да вот я уже это понял. Просто никогда ранее не слышал о таком финте (чтобы между землями бусину ставить), тут увидел, стал думать и пришел к выводу: если между аналогом и цифрой нет быстрых сигналов, то поставить, видимо, можно - изоляция по ВЧ будет лучше, а на взаимодействие это не повлияет. Но вот при наличие этих быстрых сигналов должны быть проблемы - и они, как Вы подтверждаете, есть. Да, так где-то и должно быть - глючить должно замечательно: от величины импульса тока (сколько пинов переключилось), от взаимного расположения времянок фронтов (их суперпозиции) и т.д. -

CPLD + EPCS1

dxp ответил bsp тема в Работаем с ПЛИС, области применения, выбор

Слышал много, но не пробовал. В какой степени они совместимы? Внутренняя архитектура совпадает на 100%? Они не то, чтобы совместимы, они - одно и тоже. EPCS - просто перемаркинованный M25P. Альтера эти самые EPCS делает на заводат ST и чипы там одни и те же (родные ST'шные M25P). -

Ну, порт-то не выгорит. Если токи какие-нито значительные, то тут скорее чревато помехами на аналоговую часть. Еще зависит от индикатора. У меня 3[А]ЛС339 прекрасно работали прямо с порта. И с MSP430, и с AVR. Там сегменты маленькие, токи, соответственно, тоже. Итого, вся схема - 8 токоограниивающих резисторов (или сборка) и ключи в SOT-23 на переключение разрядов.

-

Цифровое, Аналогове питание

dxp ответил Muxamor тема в Силовая Преобразовательная Техника

Земля выходного драйвера подключена практически к точке соединения земель. Т.е. на выходе из аналогового региона. АЦП ADS850Y, частота семплинга порядка 5 МГц. -

FPGA и CPLD

dxp ответил Muxamor тема в Работаем с ПЛИС, области применения, выбор

Но ведь надо же как-то их различать. Я имею в виду SRAM-Based и EEPROM-Based. Которые на LUT-ах и которые на P-Term'ах. Одного безликого ПЛИС (PLD) явно мало. Придумать удачное, адектватное название (термин, имя и т.д.) вообще зачастую очень сложно. -

Цифровое, Аналогове питание

dxp ответил Muxamor тема в Силовая Преобразовательная Техника

А вот не надо бы так делать. В пухлой книжке Analog-Digital Conversion от Analog Devices на стр. 9.35 сказано: The ADCs and DACs (and other mixed-signal ICs) with low digital currents should generally be treated as analog components and also grounded and decoupled to the analog ground plane. Здесь имеется в виду, что токи в цифровой части не слишком большие. И рисуночек у них там дальше: внутри АЦП (ЦАП) есть раздельные шины земли и питания, но снаружи они прочно закорочены. А цифровые сигналы АЦП (ЦАП) через некие резисторы уходят в цифровую часть схемы. На то она и цифровая, чтобы игнорировать мелкие помехи. Это я не по всей теме в целом, а только про микросхемы со смешанными сигналами, где есть и цифровая часть, и аналоговая. Я в курсе, читал это. Реально так и есть: цифровое питание АЦП - суть аналоговая цепь и целиком находится над аналоговым плейном. А имелся в виду только выходной буфер. У АЦП три питания: AVcc (питание аналоговой части АЦП), DVcc (питание цифрой части АЦП), Vdrv (питание выходного драйвера). Vdrv даже и напряжение другое имеет - 3.3 В, в то время как первые два - 5 В, и развязаны между собой фильтром. Так вот, к цифровой земле относится только драйвер. -

Цифровое, Аналогове питание

dxp ответил Muxamor тема в Силовая Преобразовательная Техника

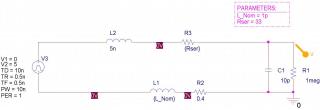

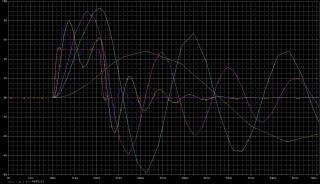

Я, возможно, сам не до конца имею правильное представление (потому и спрашиваю). Но рассуждаю так: вот идет, скажем сигнал с выхода АЦП на вход ПЛИС, это выражается, кроме прочего, в том, что по сигнальному проводнику протекает ток, а по земле (по общему) протекает возвратный ток. Т.е. при прохождении сигнала всегда имеет место протекания тока по контуру. При наличие индуктивности в контуре фронт тока будет завален (вопрос только насколько). Вот, слабал в спайсе маленькую схемку, посмотрел (схему и временнЫе диаграммы прилагаю). Все так, как и думал. На диаграмме показано семейство кривых переходного процесса. Значения индуктивностей (которые изображают ферритовую бусину) такие (в Гн): 1p, 1n, 50n, 100n, 525n (соответствует реальной бусине BLM21BB331SN1), 1u, 10u. Выводы делайте сами. Не зря же во всех букварях по High-Speed цифровому дизайну пишут, что делайте как можно более короткие и толстые земли - чтобы было меньше сопротивление и, главное, индуктивность. Еще более правильно соорудить эту схему прямо на плате и посмотреть SI. Но это следующий этап. :) -

Простите, не понял, откуда при отрицательной ОС возьмется гистерезис?

-

Точно, на стр. 214 дейсвительно сказано, что отрицательная ОС снижает стабильность. Используется только положительная. Надо почаще классиков читать. Правда все равно не очевидно почему, надо подумать. Дык это как бы очевидно: положительная ОС тут вводит гистерезис. Без гистерезиса при близких понециалах на входах компаратора будут происходить срабатывания , причем изменение режима работы внутренних элементов компаратора при переключении частенько (особенно у быстродействующих компараторов) приводит к дополнительному изменению потенциалов на входах (по питанию и другим цепям), которое хоть и мизерное (хотя порой бывает и не такое уж мизерное - опять же у быстродейтсвующих), но меняет в достаточной мере картину на входах, что приводит к обратному переключению компаратора. И этот процесс "звона" продолжается. Гистерезис же позволяет успешно бороться с этой проблемой.

-

Цифровое, Аналогове питание

dxp ответил Muxamor тема в Силовая Преобразовательная Техника

По поводу ферритовых бусин. А вот, скажем, есть некая плата, на ней стоит усилитель, далее АЦП (порядка десятка-двух мегавыборок), с АЦП данные валяться в ПЛИС. Земляной плейн "разрезан", есть только узкий "перешеек" между двумя половинками. Одна половинка - аналоговая земля, другая - цифровая. Усилитель и аналоговая половинка АЦП находятся над аналоговой землей, цифровая половинка АЦП (собственно ноги буфера цифры) и ПЛИС (и прочее цифровое хозяйство) находятся над цифровой землей. Вопрос: если поставить вместо того "перешейка", ферритовую бусину, не станет ли хуже для передачи цифры от АЦП на ПЛИС и, главное, для сигналов управления АЦП, которые идут с ПЛИС (клок и прочее)? Т.е. понятно, что индуктивность бусины не даст импульсным токам цифровых сигналов "забредать" на аналоговую половинку. Но ведь и возвратный ток цифровых сигналов между АЦП и ПЛИС тоже будет течь через эту идуктивность и фронты будут завалены. Что скажете? -

FPGA и CPLD

dxp ответил Muxamor тема в Работаем с ПЛИС, области применения, выбор

Я что-то не понял, к чему этот стеб? Микроконтроллер - это НЕ программируемая логика. Что не ясно? Названия не я придумал, не ко мне вопрос. Для CPLD нужен программатор, для FPGA он не нужен. В этом коренное отличие. Предполагается, что в "поле" программатора нет - программатор есть принадлежность производственного цикла. Еще раз, не надо меня убеждать, эти термины и их трактовку не я придумал. Мне тоже вначале показалось все это неудачным. Сейчас уже привык, стало все равно. Наличие пусть неудачных терминов лучше отсутствия таковых. Оно помогает людям вносить ясность в подавляющем большинстве случаев - когда коллега говорит FPGA, я четко понимаю, что он имел в виду. И это есть хорошо - неудачный термин, тем не менее, играет весьма полезную роль. Возможно более адекватным было название SBPLD (SRAM-Based PLD), но "паровоз уже ушел", тут обуждать нечего. Gate Array - массив вентилей, т.е. массив логики. Не более того. К БМК это имеет весьма опосредованное отношение, заключающееся в том, что БМК - это тоже массив логики. Детали внутренней реализации к делу не относятся. В разных FPGA в том числе и межсоединения делаются по-разному. И помимо вертикальных и горизонтальных каналов есть еще и прямые связи... Ладно, как уже сказал, это к делу не относится. Речь шла про классы дивайсов и их названия. Про внутренниости уже все сказали выше, я лишь про названия высказался. Именно то, как сам слышал. Причем в разное время, из разных источников. "За что купил, за то продаю".