Джеймс

Свой-

Постов

654 -

Зарегистрирован

-

Посещение

Весь контент Джеймс

-

Чтобы получить именно "те" зеленые окошки Вам нужно запустить designer.exe Путь: \Microsemi\Libero_SoC_v11.9\Designer\bin НО если работать из Libero то тоже всё в порядке - вы же сами выше дали маленький скриншот. Сейчас чуть выше показал, что нужно сделать Нет, у вас этот файл конечно же есть. Он образуется например, если вы запустите _только_ Synthesize (обвел этот пункт на Вашем скриншоте). Внимательно посмотрите папку проекта "synthesis" и найдите там файл с расширением .edn Найдите его, и будем продолжать

-

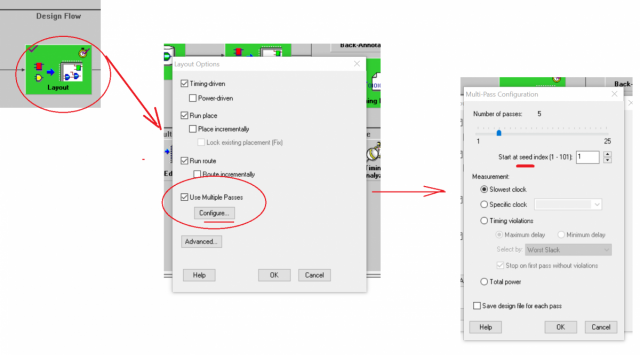

Да Place and Route - > правая кнопка мыши -> Configure Options.. Таак. Стоп. Вылетело из головы.. Начать-то надо с получения совпадающего EDIF-файла! Папка synthesis, файл - имя_проекта.edn Формат файла текстовый, и в нем всё должно совпадать, кроме даты-времени. То, что у них на компе, то должно получиться и у Вас. При условии совпадения версий Synplify, конечно! И тут уж не свалишь всё ни на какие seed-ы. Получите совпадающие EDN-ы, дальше резберемся.. Ну это неправда. Вы сейчас с AGL600V5-FGG256 боретесь? НО в любом случае надо начать с совпадающих EDN-ов ..или у вас вообще ничего не "компилируется" из-за ошибок в проекте?

-

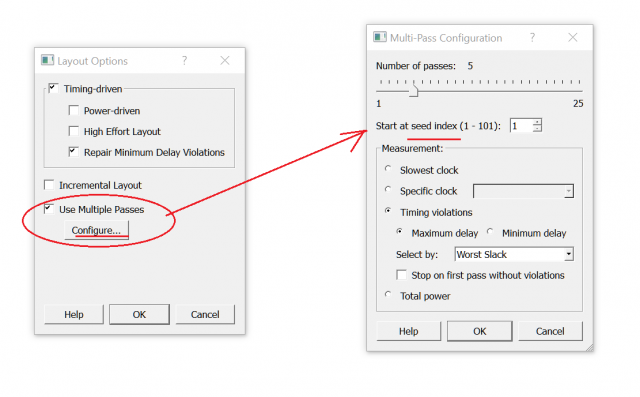

Cтранно.. Номер (812)740-6209 не отвечает?.. Может со связью что-то. Продублируйте на всякий случай вопрос на почту m1 собака actel точка ru Seed-ы (вернее индекс seed-а) можно менять при итерационной трассировке. На скриншоте показано, как. При каждой итерации в логе (в начале) будет отображаться seed. Ээ.. вот это не до конца понял. А к соисполнителям напрямую обратиться нельзя?.. C вопросом, что чему соответствует?..

-

Нет! Эти seed-ы можно менять самому. Но Libero сам их случайным образом не выбирает. При необходимости позже сделаю скриншот. Судя по Вашим последним сообщениям у вас есть какая-то проблема. Вы можете описать эту _проблему_? Могу догадываться, что у заказчика есть некая "рабочая" прошивка, и вы теперь не можете получить ее же (один-в-один) из исходников. Эта проблема тоже решается, но только не "через боковую дверь". Особенно при применении в Aerospace. Вы у официального дистрибьютора чипы покупали?

-

-

Ради интереса - почему не подходит готовый чип контроллера, например от Cypress? (пристыкованный к FPGA естественно)

-

Помочь не могу, но советую всё же расшифровать, для чего Core (ASIC или FPGA... производитель.. семейство.. технология..) Может и ответы станут более конкретными

-

Cкорее всего поставил(а) галочку "вакансии размещены в сети интернет" и забыл(а) об этом.

-

-

Такие штуки для FPGA в настоящее время constrain-ами не описываются Советую почитать про альтернативный подход с использованием PLL https://retroramblings.net/?p=515 Думаю успех на 50% будет зависеть от трассировки печатной платы

-

Напряжение питания I/O 2.5 вольта ?

-

Так на какой все-таки частоте работает ваша SDRAM?

-

"Концерн" вообще в Петербурге. Но лаконичность автора зашкаливает..

-

Боюсь вы не поняли Автора) Ему надо еще увеличить число тактовых доменов. А Global-ы кончились. Вот например цитата отклика на вопрос из предыдущей темы: ---------------------------- Например модуль timer8bit - это же тихий ужас. Работа по двум фронтам. [ ....] С модулем timer16bit ситуация та-же. Сделайте правильно один таймер, и меняйте его коэффициент пересчета при помощи параметров. ------------------------------

-

Извините, а сейчас проект работает надежно, "как часы"?

-

Вот из этой серии позволяет. Разрешения могут быть разные, только смотрите чтобы был TI Davinci DM365 на борту https://russian.alibaba.com/product-detail/ip-camera-ti-davinci-dm365-dsp-module-60343364867.html

-

Подскажите, а что за линейка? Что-то сходу не могу найти..

-

Угу. А впереди у Вас еще и пересмотр роли "супостата"

-

Так вы бы в первом сообщении указали, что за ОС на " ноуте с LPT". Может и подсказал бы кто. Ну и другой вопрос - стоит ли $3 трех часов мучений.. UPD. Вы хотите сказать, что на ноуте с 64-разр. процессором есть LPT ??

-

Заменить sram 256K x 8 на 512K x 8

Джеймс ответил zombi тема в Схемотехника

Посмотрите память FRAM с параллельной шиной (Ramtron - Cypress - Infineon?). Энергонезависимая память, тайминги близки к SRAM. Батарейка не нужна будет. -

SDRAM кто сейчас ещё производит?

Джеймс ответил zombi тема в Микросхемы

https://www.rocelec.com/about -

Ну на таких форумах люди как бы сказать.. комплектуют большие системы. А автор обращается к разработчикам, что верно. Абсолютно! Ничего себе.. Да, например министерство культуры.. Или, гораздо ближе к делу - пример "T-платформ".

-

Вы помните, как было у Булгакова? "Есть нужно уметь.... Нужно не только знать, что съесть, но и когда и как. ... И что при этом говорить. " Как думал ТС? Так и рассуждал! Ну а что SPI Clock? Обычный клок! Как и любой другой. Счетчик на нем тоже будет работать, всё просто. А то, что у такого счетчика с таким clock-ом даже reset корректно не сделать (и это заметьте не SRAM FPGA!) так об этом мы пока не задумываемся (а сброса в проекте и до сих пор нет). Конечно, автору нужен clock-бридж (особенно если он захочет довести частоту SPI до 100MHz). Ну давайте ещё 11 страниц обсуждать clock-бриджи. Вместо того чтобы объяснить, как сделать просто и правильно. На этом моё участие в этой дискуссии закончено.

-

Так какой вариант проекта вы в итоге использовали? C тактированием от clock 50MHz или с тактированием от SPI_CLK ?