-

Постов

8 009 -

Зарегистрирован

-

Посещение

-

Победитель дней

81

makc стал победителем дня 3 мая

makc имел наиболее популярный контент!

Репутация

195 Очень хорошийИнформация о makc

-

Звание

Гуру

- День рождения 26.11.1981

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Да, точно, это немного другой интерфейс с таковым сигналом (синхронный UART), которого у FTDI нет. Поэтому единственное на мой взгляд решение для FTDI это программно воспроизвести этот протокол с использованием режима BitBang или MPSSE. Точно так же сделан драйвер для протокола SWD. Но готовых реализаций для этого варианта нашел только одну - https://github.com/DiUS/xmega-pdi-pi2 Если в ней заменить работу с GPIO-пинами на работу с пинами FTDI, то вы получите искомое решение.

-

https://github.com/mraardvark/pyupdi Avrdude использует ту же схему.

-

Раздел вполне соответствует уровню и характеру вопроса. Устное предупреждение: исходники и логи (длинный текст) прикрепляйте к сообщениям в виде файлов (аттачей), а не вставляйте в текст без тега код и спойлеров. В противном случае вы получите предупреждение и посты будут удалены.

-

Я успешно использовал https://github.com/atomicobject/heatshrink

-

Да, точно, перепутал.

-

У Logos2 в 324-м корпусе есть трансиверы и они работают. Или что вы имеете в виду?

-

-

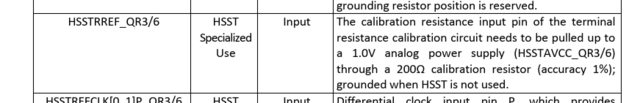

Нет, не совсем так. Трансиверы и их питание не полностью совпадают с Xilinx.

-

Вы сравнивали токи потребления рабочих и сбоящих микросхем по каждому из номиналов?

-

А что с питанием банка ВВ, через который идёт конфигурация? И нет ли у них каких-либо специальных пинов, типа CFGBVS, которые могут влиять на этот процесс?

-

Паяльная станция на 200 Вт

makc ответил yuriger тема в Пайка и монтаж

На выставке их и правда было заменено меньше, чем раньше. Но были и будут. -

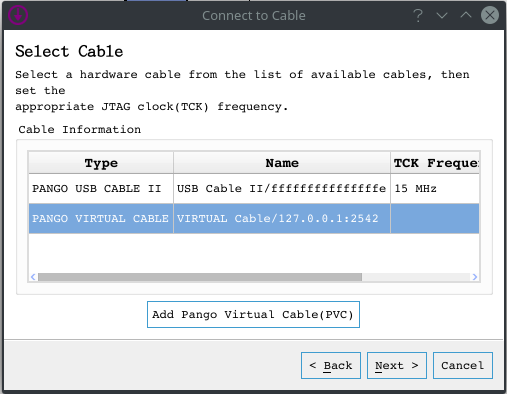

Добрый день, уважаемые участники, Если-ли у кого-нибудь описание протокола взаимодействия с сервером виртуального кабеля (PVC) для Pango и опыт работы по этому протоколу? На сколько я понимаю, они переизобрели протокол XVC (Xilinx Virtual Cable), судя по начальному запросу "getinfo:", это он и есть. Пример реализации можно посмотреть здесь - https://github.com/Xilinx/XilinxVirtualCable Мой демон XVCD, который успешно работает с Vivado, сумел зацепиться и начать работать с Logos2 на отладочной плате AXP100 в среде PDS 2023.2-SP1: Тестовый проект через этот кабель загрузился, работает. Но пока не оставляет ощущение, что как-то всё слишком гладко прошло для первого раза. 😉

-

- pango micro

- pvc

-

(и ещё 4 )

C тегом:

-

Предлагайте.

-

ПЛИС PangoMicro

makc ответил Gas Wilson тема в Работаем с ПЛИС, области применения, выбор

Обсуждение проблем поддержки Verilog/VHDL выделено в отдельную тему -

Там скорее другие проблемы (тормоза), т.к. в них есть деление на энергоэффективные (тормозные) и производительные ядра. И из-за недоработок планировщика ОС некоторые быстрые задачи оказываются вытеснены на тормозные ядра, они не тянут и начинает пинг-понг, который не идёт на пользу скорости работы. Для Vivado и т.п. задач это не проблема. Особенно под Linux. На работе разработчики под Windows тоже не замечают проблем с этими новыми процессорами на задачах компиляции проектов и т.п.