Поиск

Показаны результаты для тегов 'spi'.

-

Ищу список перепаек для Raystar под SPI

firstvald опубликовал тема в Интерфейсы

Ищу список переделок на плате Raystar 20x2 под работу на SPI. Хотя режим упоминается как рабочий необходимые перепайки не указаны. Нашел только это. Некоторое упоминание есть для Winstar. Но это раскопки. Нашел через внешний поиск отсыл сюда же. И уже по цепочке вот. -

Народ, а кто-нибудь пробовал реализовать на CH569W мост USB-FIFO по типу CYUSB3014? Или может быть есть у кого-нибудь грамотный пример приёма и отправки пакетов по USB3.0 на CH569W?

-

SPI NOR и Allwinner SoC

repstosw опубликовал тема в TI, Allwinner, GigaDevice, Nordic, Espressif и другие

Есть SPI NOR, которая подключена через SPI к Allwinner T113-s3. Функционал записи, чтения, стирания работает. Запись - блок до 256 байт Стирание - блок 4096 байт Необходимо прикрутить FatFs к SPI NOR и отобразить диск через USB для ПК. ПК тоже должен уметь читать и писать файлы в SPI NOR. Есть проблема: ПК видит только съёмные диски с размером сектора 512 байт. Если записать такой кусок я ещё смогу - 2 раза по 256 байт для SPI NOR. То как быть со стиранием? Стираются сразу 4096 байт. В идеале, заставить FatFs работать с размером сектора 4096 байт, но Windows в ПК такой диск не распознаёт и требует форматирования. Что можно сделать? Как избежать лишнего стирания? (копировать все 8 блоков по 512 байт каждый, менять один и записывать все 8 - это сильно уменьшит ресурс по стиранию SPI NOR). -

Приветствую уважаемых участников форума! Пытаюсь найти информацию по таймингам интерфейсов довольно интересного с точки зрения скоростных интерфейсов контроллера - http://www.wch-ic.com/products/CH569.html - и не нахожу вообще ничего. Т.е. в даташите отсутствуют данные даже по банальным параметрам setup/hold и т.п. для SPI, не говоря уже о других более скоростных интерфейсах типа HSPI или SERDES. При этом протокол SERDES у них вообще не описан ни в каком виде, хотя для HSPI они нашли в себе силы описать структуру пакета. Где можно взять эту информацию? И мне очень интересно, как можно разрабатывать что либо работающее надёжно не имея этой информации. На что рассчитывают товарищи китайцы не отражая в документации временные параметры? PS: Про отсутствие полноценного reference manual или users guide я молчу, такое у них сплошь и рядом. Но чтобы из динамических параметров были только времена выхода из сна и т.п. - это уже немного через чур.

-

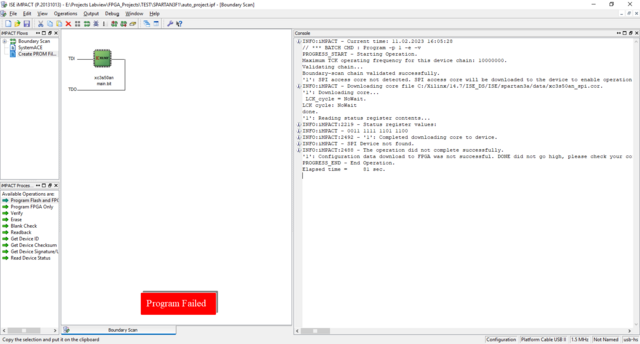

Spartan3AN - SPI Device not found

Valek87 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Помогите пожалуйста разобраться с программированием внутренней flash микросхемы Spartan3AN. PROG_B и INIT_B через резистор 4,7 кОм к VCC, SUSPEND = GND, M2:0 = "JTAG" Вот что пишется после подачи питания при нажатии "Get device ID": Вот что пишется после подачи питания при нажатии "Read device status": Если просто прошить ПЛИС, то без проблем она прошивается. Но стоит попытаться прошиться во внутреннюю flash, то вот что пишется: Пишется якобы не найден внутренний SPI. Я пробовал на трёх микросхемах. И везде одинаковый результат. Подскажите, пожалуйста, на что обратить внимание!- 7 ответов

-

- spartan3an

- flash

-

(и ещё 1 )

C тегом:

-

Компания Everspin объявила о запуске производства образцов нового семейства микросхем памяти с интерфейсами SPI/QSPI/xSPI – серия EMxxLX. Данная серия является самой высокопроизводительной постоянной памятью с полной пропускной способностью чтения и записи 400 Мбайт/c. Подробнее

-

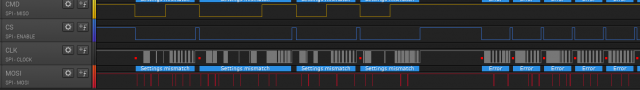

Предпринимаются попытки настройки микропроцессора 1892ВМ14Я на базе процессорного модуля Салют–ЭЛ24ПМ и отладочного модуля САЛЮТ-ЭЛ24ОМ1 (рев. 1.2). SDR-приемник 1288ХК1Т расположен на отладочном модуле MF-01EM (вер. 4.0). Работы заключается в создании программы для процессора, которая по интерфейсу SPI настраивает регистры 1288ХК1Т и получает отсчеты сигнала по параллельному LINK-порту. В ходе написания и отладки кода возникла проблема, при которой не получается записать данные в регистры 1288ХК1Т. Это проявляется тем, что при попытке считывания значений нескольких регистров один за другим 1288ХК1Т отвечает всегда значением первого считанного за этот сеанс отладки регистра. То есть, складывается ощущение, что так называемый внутренний регистр данных порта позволяет записать в себя что-то 1 раз, а после этого не дает себе перезаписать. При этом при попытке считать не данные, а адрес регистра, который сейчас пытается быть настроенным процессором, чтение выполняется корректно. То есть, с так называемым внутренним регистром адреса никаких проблем нет. Были попытки изменять конфигурацию SPI в значении числа слов в одной посылке и скорости обмена данными по интерфейсу. Однако, проблема пока не исчезла. Параллельно ведется активная беседа с технической поддержкой Элвис, но для ускорения процесса хотелось бы узнать, если ли мнения по этому вопросу у других пользователей, которые работали с этими продуктами. Демонстрационное ПО, которое предлагается вместе с отладочной платой MF-01EM работает корректно, в связи с чем можно заключить, что плата и микросхема исправны.

-

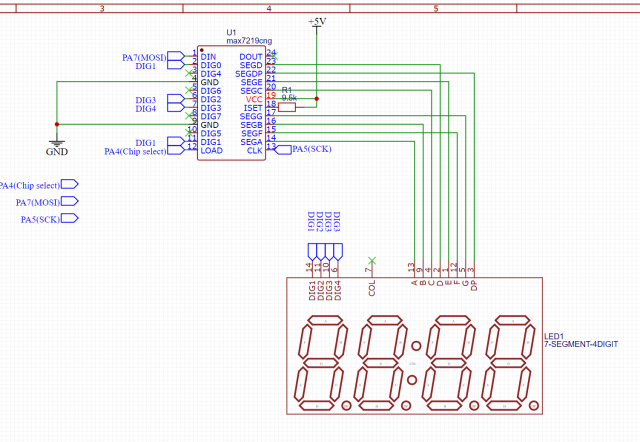

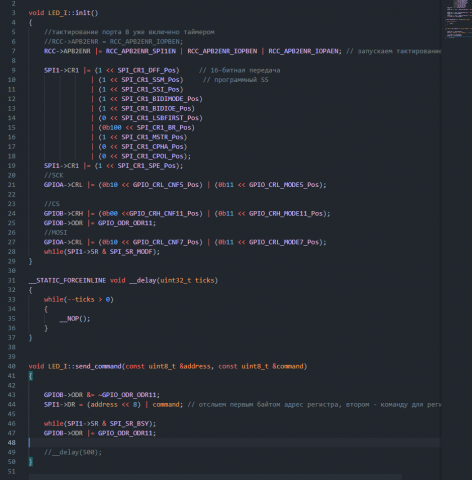

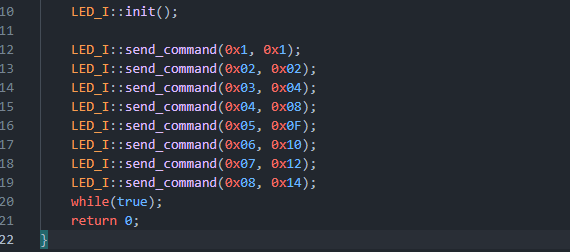

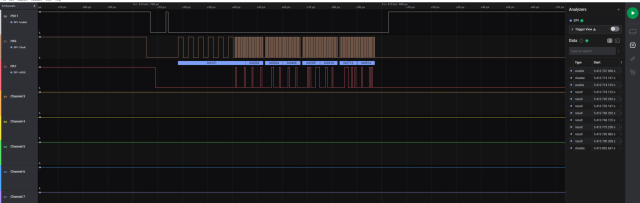

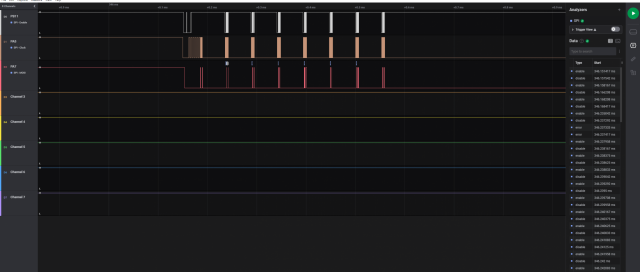

Приветствую, друзья! Передо мной стоит задача: подключить камень stm32f103c8t6 по SPI через MAX7219 к семисегментнику. Подключал по схеме: Выясняется, что у меня ничего не работает. Понять почему я, увы, не могу. Функции инициализации SPI и отправки данных: Чтобы понять проблему, я подключил логический анализатор ко всем трем выводам(MOSI, SCK, SS): Исходя из даташита на MAX7219, она принимает данные после того, как будут отправлены 2 байта и поднята ножка SS. На фотографии с анализатора становится понятно, что SS дергается после того, как абсолютно все данные уйдут. В чем проблема, с чем это связано - я не могу понять. Пробовал добавить задержку в функции отправки, подумав, что, может быть, мой анализатор не фиксирует их. На что я получил ошибки в отправляемых данных: Не понимаю, что я сделал не так... Буду очень рад, если Вы подскажете! Заранее большое спасибо!

-

Возможно ли моделирование, отладка, SPI, AD7714

Zx80 опубликовал тема в Операционные усилители и АЦП

Привет коллеги. Работаю через SPI c AD7714. Подскажите возможно ли ее моделирование в системах подобных Proteus ? Или какой другой путь отладки программы общения с AD7714 через SPI ? -

Нужна помощь по SPI, DMA, Vivado

Nano2021 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! Я работаю над реализацией высокоскоростной передачи SPI и ищу лучший вариант для блока DMA. Схематическое изображение моей конструкции:прикрепил На сайте Xilinx я нашел следующиe блоки, который могу использовать: DMA Central Direct Memory Access DataMover 1. В чем разница между DMA и CDMA? Судя по описаниям и блок-схемам, это ... как будто потоковым устройством будет устройство, которое производит или потребляет поток байтов. Устройство с отображением памяти подключается к шине памяти. Таким образом, периферийному устройству, которое хранит входящие данные в регистре с отображением в память, потребуется CDMA, а периферийному устройству, где данные поступают непосредственно из буфера FIFO, потребуется DMA. 2. AXI Data Mover. Если я подключу его с блоком AXI FIFO Stream (параметры передачи команд), я получу блок DMA, как я понял. Этот блок дает мне больше свободы в реализации? 3. Какой вариант лучше всего для передачи данных из высокоскоростного SPI через DMA в память? Я бы хотел достичь 50-100 Мбит / с Заранее спасибо за вашу помощь -

Трассировка SPI

lucy опубликовал тема в Интерфейсы

Всем, доброго времени суток!))) Так уж случилось, что ранее я не имела дел с SPI интерфейсом... Сейчас накидываю схему, где у меня 3 устройства общаются по кольцевой схеме. Расстояние между устройствами будет минимально возможное. В связи с этим встает вопрос: какие особенности трассировки следовало бы соблюсти? Изделие будет не сильно шумящее. Частота 20MHz. Ну, CLK я задам правило, чтобы расстояние не менее 0.5мм было до трассы. А вот фильтры, допустим, по линиям передачи ставить? Я думаю, что стоит подобрать на 50МГц ориентировочно. Все-таки spi довольно уязвим к помехам, как я считаю... -

Корпорация Winbond Electronics объявила о расширении своей линейки SPI NOR Flash, представив одинарную монолитную флеш-память SPI NOR 1,8 В 512 Мбайт, которая может поддерживать стандартную/двойную частоту до 166 МГц/quad SPI clocks. Подробнее

-

Ограничения Multi cycle

Tik31 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

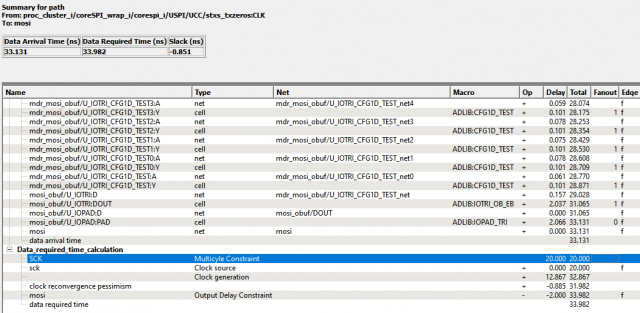

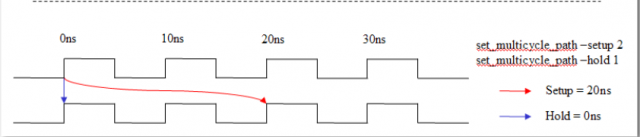

Здравствуйте! Продолжаю разбираться с написанием констрейнтов для текущего проекта (Polarfire Microchip). В этот раз проблема связана с ограничениями для SPI ядра (частота шины - 50 МГц, SPI - 25 МГц). Мною (на основе примера) был подготовлен следующий файл с ограничениями. ################################################################# # Определение частоты ################################################################## # Частота системной шины - 50 МГц. Максимальная частота SPI - 25 МГц set clkSysPeriod 20 set clkSpiPeriod 40 create_generated_clock -name SCK \ -divide_by 2 \ -source [get_pins proc_cluster_i/coreSPI_wrap_i/corespi_i/USPI/UCC/spi_clk_out/CLK] \ [get_ports sck] ################################################################# # Задание входных и выходных задержек ################################################################# set trace_delay_clock 0 set trace_delay_mosi 0 set trace_delay_miso 0 set trace_delay_ss 0 set mosi_setup 2.0 set mosi_hold 2.0 set ss_setup 3.0 set ss_hold 3.0 set mosi_max_delay [expr {$trace_delay_mosi + $mosi_setup - $trace_delay_clock}] set mosi_min_delay [expr {$trace_delay_mosi - $mosi_hold - $trace_delay_clock}] set ss_max_delay [expr {$trace_delay_ss + $ss_setup - $trace_delay_clock}] set ss_min_delay [expr {$trace_delay_ss - $ss_hold - $trace_delay_clock}] # Задание Tco для MISO (см. datasheet) set Tco_Max 8.0 set Tco_Min 0.0 set miso_max_delay [expr $Tco_Max + $trace_delay_clock + $trace_delay_miso] set miso_min_delay [expr $Tco_Min + $trace_delay_clock + $trace_delay_miso] # Данные из FPGA изменяются по заднему фронту частоты SCK и защелкиваются по переднему во Flash set_output_delay -clock [get_clocks {SCK}] -clock_fall -max $mosi_max_delay [get_ports {mosi}] set_output_delay -clock [get_clocks {SCK}] -clock_fall -min $mosi_min_delay [get_ports {mosi}] set_output_delay -clock [get_clocks {SCK}] -clock_fall -max $ss_max_delay [get_ports {ss}] set_output_delay -clock [get_clocks {SCK}] -clock_fall -min $ss_min_delay [get_ports {ss}] # Данные из Flash изменяются по заднему фронту частоты SCK и защелкиваются по переднему в FPGA set_input_delay -clock [get_clocks {SCK}] -clock_fall -max $miso_max_delay [get_ports {miso}] set_input_delay -clock [get_clocks {SCK}] -clock_fall -min $miso_min_delay [get_ports {miso}] ################################################################# # Multi-Cycle ################################################################# set multiCycleCount [expr {int(ceil($clkSpiPeriod/$clkSysPeriod))}] set_multicycle_path -setup $multiCycleCount \ -to [get_ports {mosi}] set_multicycle_path -hold [expr {$multiCycleCount - 1}] \ -to [get_ports {mosi}] set_multicycle_path -setup $multiCycleCount \ -to [get_ports {ss}] set_multicycle_path -hold [expr {$multiCycleCount - 1}] \ -to [get_ports {ss}] set_multicycle_path -setup $multiCycleCount \ -through [get_ports {miso}] \ -to [get_clocks {clk50}] set_multicycle_path -hold [expr {$multiCycleCount - 1}] \ -through [get_ports {miso}] \ -to [get_clocks {clk50}] Системная частота задается в другом файле и имеет вид: # Входная тактовая частота create_clock -name {clk} -period 20 -waveform {0 10 } [ get_ports { clk } ] # Входная частота JTAG create_clock -name {tck} -period 166.67 -waveform {0 83.33 } [ get_ports { tck } ] # Частоты SYS_PLL create_generated_clock -name {clk125} -multiply_by 5 -divide_by 2 -source [ get_pins { pll_0/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { pll_0/PF_CCC_C0_0/pll_inst_0/OUT1} ] create_generated_clock -name {clk50} -multiply_by 1 -divide_by 1 -source [ get_pins { pll_0/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { pll_0/PF_CCC_C0_0/pll_inst_0/OUT2} ] После P&R и Timing Verify я получил нарушение по Hold В данном очтете мне не понятно откуда берется +20 нс (Multicycle), если я задал: set_multicycle_path -hold [expr {$multiCycleCount - 1}] \ -to [get_ports {mosi}] Libero корректно воспринял конструкции как -setup 2 -hold 1. Ориентировался я на картинку ниже -

Здравствуйте. Появилась следующая задача: к STM32F103C8T6 подключена SD карта по SPI. Библиотека FatFS. Микроконтроллер читает содержимое карты и выдает список файлов в USART. На ПК в терминальной программе я наблюдаю этот список. Но не могу понять как получить обратную связь от ПК, а именно как указать МК по USART что я выбрал какой либо файл? Пусть, например, на SD карте у меня 4 файла и одна папка. Я наблюдаю их в окне терминальной программы: ПАПКА1 Data1.txt SuperData.txt BigDataSuperMegaLog.txt Данные.txt Как дать понять МК что я выбрал файл "Данные.txt" ? Чтобы он его прочитал и также выдал содержимое в USART. Или что я выбрал ПАПКА1 и МК прочитал содержимое этой папки и так же выдал в USART список файлов в ней. Пересылать названия скорее всего не очень правильная идея. Организовать буфер в МК и присвоить каждому файлу свой номер - не хватит ОЗУ. Может есть в FatFS какие то индексы у файлов? Читаю список так:

-

Гадание по эпюрам: какому контроллеру LCD они принадлежат?

Doka опубликовал тема в В помощь начинающему

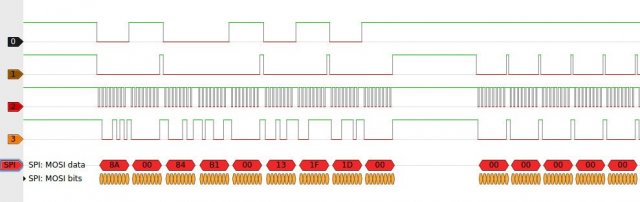

Взываю к помощи коллективного разума. Проснифал SPI-подобный интерфейс монохромного матричного LCD экрана и пытаюсь отыскать на каком контроллере он реализован, чтобы узнать полный набор команд. Сам интерфейс самый что ни на есть банальный: SCK, MOSI, CS + CMD (в даташитах на контроллеры называют RS - наследие эпохи HD44780): 0 - команда, 1 - данные. помимо десятка непонятных команд выяснилось следующее, сам вывод пиксельной инфы: команда 0xB1 - индекс строки (8битной) в которую будем выводить пиксели команда 0x1D - позиция (индекс столбца) начиная с которого выводим пиксели После 0x1D и индекса идут сразу непосредственно данные экрана, для экрана 100х100 это, например, 100 байтов (т.е. строка 8х100). Этот протокол (и контроллер) используется и в дисплее 100х100, и в дисплее 256х64, притом есть некая разновидность контроллера, когда CS выдаётся не на каждую команду, а только на данные, сопровождающие конкретную команду (скриншот приложу). Притом похоже встрачаются двухбайтовые команды (не В1, а 84В1 а после payload — байт данных для этой команды) Может кому попадался такой протокол и подскажет конкретную модель контроллера? -

Разработка ПО (STM32, TMS320F28xxx, PIC, LPC)

C2000 опубликовал тема в Ищу работу

На время карантина ищу удаленную работу, дабы скомпенсировать денежные потери. Большой опыт в разработке как аппаратной части так и ПО. НО в данный момент приоритеты на стороне программного обеспечения, хотя если будет интересная (в смысле оплачиваемая) работа, то есть возможность разработки схем и трассировки PCB. Есть опыт работы с IDE: Eclipse, Keil, MPLAB, CodeComposer. Сейчас работаю в Eclipse + GCC, это среда разработки по умолчанию. Опять же если у заказчика есть жесткие требования, то можно будет использовать и другую среду разработки. Ради интереса не работаю, проекты на 2 часа (как бы) где 95% уже сделано, осталось всего 5% доделать тоже не интересны. Адрес для связи: [email protected] -

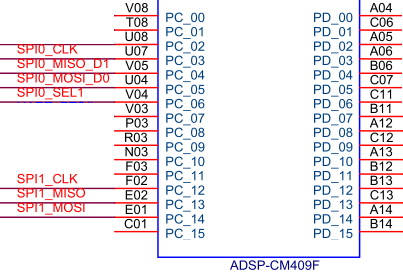

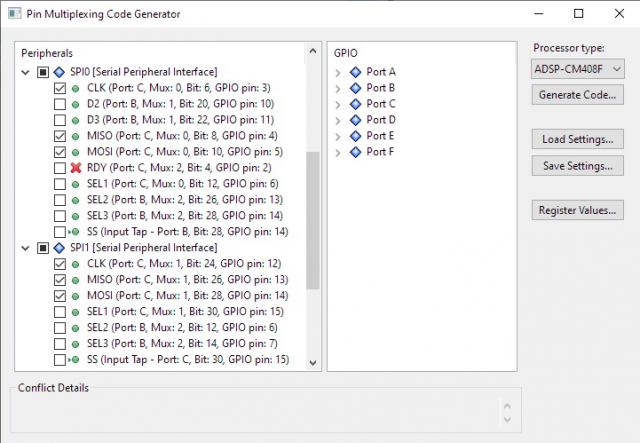

ADSP-CM409F проблемы c SPI

Vengin опубликовал тема в Все остальные микроконтроллеры

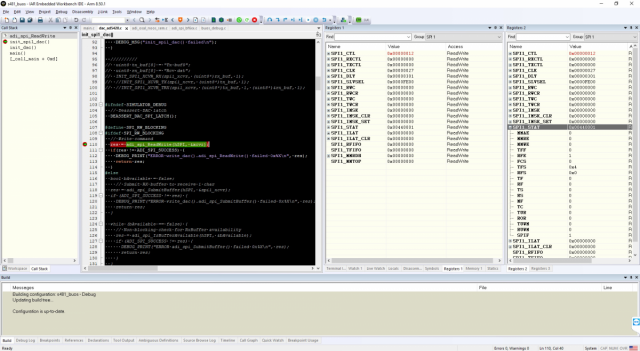

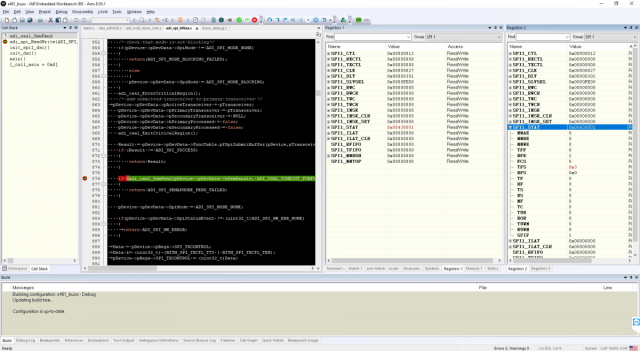

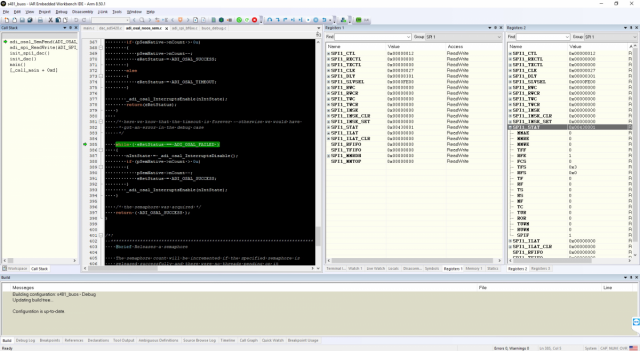

Здравствуйте. Имеется кастомная плата с процессором ADSP-CM409F (Analog Devices). Задействовано два SPI интерфейса, и любые попытки транзакций чтения/записи не происходят (блокируются). Далее детали. Используется два SPI интерфейса (SPI_0, SPI_1), оба подсоединены к Porct_C (к специальным пинам, которые могут быть промультиплексированы на SPI интерфейс): Мультиплексирование сделано используя PinMux тул (часть "ADSP-CM40x Enablement Package"): Код для тестирования SPI базируется на примере “SPI_flash_read” (также входящий в "ADSP-CM40x Enablement Package"), который использует выделенный SPI_2 интерфейс для чтения встроенной Flash памяти, и этот пример работает. Далее упрощённая версия кода (который не работает) для инициализации и чтения одного байта по SPI_1: #include <stdio.h> #include <drivers/spi/adi_spi.h> // SPI variables uint8_t rx_buf[4] = {0}; // SPI_1 transceiver setup for 1 byte RX operation (without prologue) ADI_SPI_TRANSCEIVER xcvr = { NULL, 0, NULL, 0, &rx_buf[0], 1 }; static ADI_SPI_HANDLE hSPI; static uint8_t SpiMemory[ADI_SPI_INT_MEMORY_SIZE]; ADI_SPI_RESULT tst_spi1() { /******************************************************************************* * SPI Init: Master, Non-DMA mode, Software SlaveSelect ******************************************************************************/ ADI_SPI_RESULT res; res = adi_spi_Open(1, &SpiMemory, ADI_SPI_INT_MEMORY_SIZE, &hSPI); res += adi_spi_SetMaster(hSPI, true); //set as master res += adi_spi_SetHwSlaveSelect(hSPI, false); // Software (not Hardware) Slave Select res += adi_spi_SetWordSize(hSPI, ADI_SPI_TRANSFER_8BIT); // 8-bits word size res += adi_spi_SetClock(hSPI, 39); // 2 MHz (for SYSKCLK = 80MHz) res += adi_spi_SetClockPolarity(hSPI, true); // Active HIHG clock res += adi_spi_SetClockPhase(hSPI, true); // Data transitions on the RISING edge of the clock res += adi_spi_RegisterCallback(hSPI, NULL, NULL); // none res += adi_spi_EnableDmaMode(hSPI, false); // Interrupt driven mode /******************************************************************************* * SPI transfer to read 1 byte in either Blocking/Non-Blocking mode ******************************************************************************/ #define SPI_RW_BLOCKING #ifdef SPI_RW_BLOCKING // Blocking Transfer res = adi_spi_ReadWrite(hSPI, &xcvr); #else // Non-Blocking Transfer bool bAvailable = false; // Submit RX buffer to receive 1 char res = adi_spi_SubmitBuffer(hSPI, &xcvr); do { // Non-blocking check for rx_buf availability res = adi_spi_IsBufferAvailable(hSPI, &bAvailable); if (ADI_SPI_SUCCESS != res) { break; // exit the loop } } while (!bAvailable); #endif // SPI_RW_BLOCKING return res; } Код состоит из двух частей: Инициализация (Master, Non-DMA mode, Software Slave-Select). Транзакция чтения 1 байта в блокирующем/неблокирующем режиме. Проблема возникает во 2-ой части при попытке транзакции данных. Любая транзакция (чтения/записи в блокирующем или неблокирующем режиме) никогда не заканчивается, а зависает в бесконечном цикле ожидания. В блокирующем режиме код зависает на строке adi_spi_ReadWrite(hSPI, &xcvr): Внутри функции adi_spi_ReadWrite() видно, что код зависает на функции adi_osal_SemPend(): При входе в функцию adi_osal_SemPend(): видно что код просто крутится в бесконечном цикле while, в котором вроде что-то связанное с прерываниями (функции _adi_osal_InterruptsDisable()/_adi_osal_InterruptsEnable()): Такая же проблема возникает в неблокирующем режиме. В этом случае после передачи буфера (функция adi_spi_SubmitBuffer(hSPI, &xcvr) ), код зависает на функции adi_spi_IsBufferAvailable(), т.е. буфер данных никогда не становится доступным. Что конкретно не так непонятно. Пробовал разные настройки инициализации – не помогает. Пробовал разные комбинации чтения/записи данных разных размеров – ничего. Проблема идентична для обоих SPI интерфейсов (SPI_0 и SPI_1). Может кто знает, в чем может быть проблема и как это решить? ADSP-CM409F SPI debug.zip -

Помогите разобраться с AT89s8253

Владимир В опубликовал тема в MCS51, AVR, PIC, STM8, 8bit

Пытаюсь освоить работу с AT89s8253. Начал мастерить отладочную плату и для дальнейшей разработки встал вопрос о связи с внешними устройствами посредством: USB, LAN, RS485. Наткнулся в инете на LAN модули имеющие интерфейс SPI, однако порты ввода вывода модуля LAN имеют несколько соединительных линий (SS, MOSI, MISO, SCK) а AT89s8253 имеет на своем борту для SPI только Р 3.0 Ранее я работал с 80С51 Intel, теперь пытаюсь вспомнить молодость и собрать конкретную умную железку. Информации о AT89s8253 в свободном доступе очень мало, даже не попадается карта адресов регистров данной сборки. А говорить о решениях с интерфейсами пока только кажется наглостью с моей стороны. Ощущение, что Atmel не поддерживает свои изделия. На данный контроллер практически отсутствуют средства разработки: Эмуляторы, симуляторы. Нашел отладочную плату для студентов и разработчиков, жду доставку. Хоть что то чем совсем ни чего. Городить кучу кубиков вокруг контроллера не хочется, было бы идеальным получить вектор в котором нужно двигаться для объединения высокоскоростных последовательных интерфейсов с вышеупомянутым контроллером. -

Много SPI ?

Allregia опубликовал тема в ARM, 32bit

Задача такая - есть 6 линий данных (0..i) плюс клок. Нужно сделать задержку в каждой линии данных на N(i) тактов (т.е. на разное число в разных линиях данных!) Клок может быть от 2 до 12Мгц (известный заранее), а задерживать надо до 10мс (ну хотя бы до 5мс), т.е. N достаточно большие. "В лоб" понятно - ввсести в проц через один SPI, далее буферная память, и вывести через другой. Но процов с 6-ю фулл-дуплекс SPI меньое чем с 144 ног не нашел (F429ZITx), памяти у него зватит, но вроде как там нельзя задействовать 12 каналов DMA, а делать по прерываниям - я тогда не смогу на этот-же проц навесить другую работу - придется ставить отдельно проц для всего остального, и этот чисто как линию задержки, для чего LQFP144 немного великоват по размерм (БГА исключается). Может есть какие более простые/логичные пути решения? (цена ВОМ-а - $10-15 на количестве в десяток подойдет, так что ФПГА за полторы штуки баксов не предлагать :)) Спасибо за любой совет. P.S. можератору почему-то дубль темы получился, удалите одну пожалуйства. -

Много SPI ?

Allregia опубликовал тема в ARM, 32bit

Задача такая - есть 6 линий данных (0..i) плюс клок. Нужно сделать задержку в каждой линии данных на N(i) тактов (т.е. на разное число в разных линиях данных!) Клок может быть от 2 до 12Мгц (известный заранее), а задерживать надо до 10мс (ну хотя бы до 5мс), т.е. N достаточно большие. "В лоб" понятно - ввсести в проц через один SPI, далее буферная память, и вывести через другой. Но процов с 6-ю фулл-дуплекс SPI меньое чем с 144 ног не нашел (F429ZITx), памяти у него зватит, но вроде как там нельзя задействовать 12 каналов DMA, а делать по прерываниям - я тогда не смогу на этот-же проц навесить другую работу - придется ставить отдельно проц для всего остального, и этот чисто как линию задержки, для чего LQFP144 немного великоват по размерм (БГА исключается). Может есть какие более простые/логичные пути решения? (цена ВОМ-а - $10-15 на количестве в десяток подойдет, так что ФПГА за полторы штуки баксов не предлагать :)) Спасиюбо за любой совет. -

Варианты отображения карты регистров конфигурации чипа

alexunder опубликовал тема в Программирование

Приветствую! Для конфигурации ИМС используем набор регистров, доступных по интерфейсу SPI. Регистры бывают разной длины (как правило, не больше 14 бит), отдельные поля внутри регистров так же могут быть разной длины. Для первичного тестирования поведения чипа в статическом режиме я сделал форму, в которой содержимое отдельных полей каждого регистра может меняться на лету. Пример такой формы с картой регистров представлен на картинке ниже. Регистры расположены по вертикали, содержимое регистров (отдельных битовых полей) - по горизонтали. Внутри каждой ячейки отображено имя поля и его текущее значение. Принцип работы прост: оператор нажимает на ячейку, меняет значение, форма отсылает команду по SPI, оператор наблюдает, что происходит с ИМС и т.д. Для каждого проекта своя карта регистров, которая "подцепляется" к форме из JSON файла. Форма создавалась по-быстрому и, как это обычно бывает, так и осталась в первозданном виде. Хотелось бы сделать что-то более удобное или компактное, даже не знаю, что конкретно в этой не устраивает, но хочется, чтобы содержимое отображалось покомпактнее. Наверняка многие сталкивались с задачами удобного отображения конфигурации регистров. Буду рад, если кто-нибудь поделится своими или чужими визуальным решениями. -

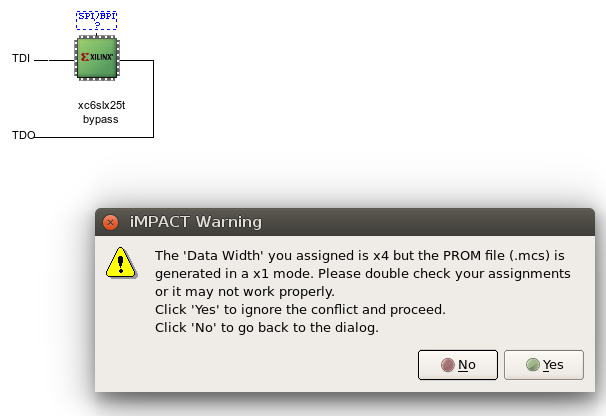

Есть плата, на которой Quad SPI Flash, и очень важно, чтобы оно работало именно в таком режиме - в x4, иначе плата стартует слишком долго и поэтому прошивка не работает. Для этого я пытался через GUI создать PROM файл в формате mcs, но так и не добился x4 mode. Пробовал и в командной строке создавать mcs через bash скрипт - есть опции spi_width 8/16/32, но 4 нет, но и на 8 при попытке назначить прошивку флэшки все равно про нее пишет что она x1. Что делать??? Может mcs формат не поддерживает x4 и нужно выбрать другой? Но нет, promgen поддерживает много форматов и опции общие для всех них. Еще один вопрос, а можно ли повысить частоту работы SPI флэшки при загрузке? Мне автор прошивки говорит, что дескать по дефолту она стартует на частоте 10 МГц, а можно сделать 20-25 МГц! Вот я не нашел, где же задать это. Да и странно это, как это возможно, разве при загрузке первых кусков прошивки оно там считает скорость, на которой грузить остальное?

-

Добрый день! Необходимо сконфигурировать с помощью zynq ацп и цап, имеющий только 3 - х проводный spi. Axi-quad SPI работает только в 4-х проводном. Может кто сталкивался, как это можно сделать? Спасибо.

-

Программирование SPI-флешки

Art55555 опубликовал тема в Работаем с ПЛИС, области применения, выбор

На плате установлен Artix 7 и SPI-флеш N25Q256. Для создания Initial и Update-MCS прошивок использую perl-script. Вопросов нет. Но вот для того, чтобы "загнать" первичную прошивку в SPI-флеш N25Q256, использую IMPACT (JTAG). Всё бы хорошо, только этот процесс очень длительный (более 10 минут). Есть способ как-то ускорить процесс первичной записи флешки?