Nano2021

Участник-

Постов

11 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйПосетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

оптика или радио

Nano2021 опубликовал тема в Сигнальные процессоры и их программирование - DSP

Привет. Я провожу исследования и пытаюсь понять разницу между оптическими и радиосистемами в спутниковой связи. не могли бы вы помочь мне разобраться в некоторых вопросах? В чем разница между передатчиком или приемником в оптических и радиосистемах? Оптический передатчик или приемник одинаковый по конструкции (модуляция / демодуляция, фильтр ...) + оптический детектор? -

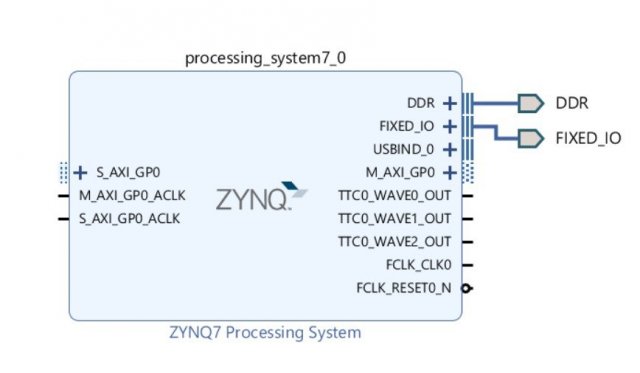

Я написал функцию "memcpy" для копирования блока данных с исходного адреса на адрес назначения. Хочу протестировать на плате (Zynq). Я новичок в MCU и изучаю эту тему самостоятельно, извините, если мой вопрос для вас глупый. Что я сделал: Я создал проект в vivado, начал block design с Zynq, изменил конфигурацию PS-PL (добавил GP Master и Slave AXI Interface) [Смотри приложение]. Я читал, что Zynq может быть Master, но Slave/ периферийнoe устройство я должен спроектировать как настраиваемое IP-ядро. Я уже нашел, как создать собственный AXI IP (slave или master). Vivado создает шаблон настраиваемого IP-ядра (slave). (1) Могу ли я использовать этот шаблон без каких-либо изменений? (2) Следует ли мне добавить дополнительную информацию (сигналы, которые я использую в функции memcpy: адреса и количество битов)? Я пропустил дизайн custom master . (3) Я сделал правильно или мастер должен быть частью настраиваемого IP ядра?

-

Привет всем! Я хочу создать собственный блок (custom AXI IP), простой, для новичка-самоучки, который будет копировать данные в память (что то похожее на memcpy). Создаю блок IP , из которого я хотел бы сделать периферийные устройства AXI Master и Slave с помощью VIVADO. Я создал новое периферийное устройство AXI4 с помощью tools – create and package new IP в Vivado. Выбрал следующие параматры: Master: Interface Type: Full Interface Mode: Master Data Width (Bits): 32 Slave: Interface Type: Lite Interface Mode: Slave Теперь захожу в редактор IP и добавляю три дополнительных сигнала в Slave: destination_addr : out std_logic_vector (C_S_AXI_DATA_WIDTH-1 downto 1); -- 32 source_addr : out std_logic_vector (C_S_AXI_DATA_WIDTH-1 downto 1); -- 32 length : out std_logic_vector (C_S_AXI_DATA_WIDTH-1 downto 15); --16 В конце еще добавил: dst_addr <= slv_reg0; src_addr <= slv_reg1; length <= slv_reg2(31 downto 15); А еще добавляю эти 3 сигнала в Top файл. в мастер файле не делал изменений (пока...не знаю должен ли что то добавить) Собрал блок схему,приложу. Генерирую бит. И получаю следующую ошибку: Project 'Custom_slave_master_accelerator' Bitstream Generation failed. Перебрал сотни tutorial в интеренете, ничего из этого не помогло исправить ошибку. Где я ощибся? Master файлу нужны дополнительные параметры? Slave? Верны ли мои три сигнала? Может кто уже делал что то похожее и есть парочка примеров как такое мне собрать или знает хороший tutorial? или совет? PS До SDK еще не дошел, это еще меня ожидает!

-

Здравствуйте, Zig ! спасибо, что нашли время ответить. Переделал...показывает 0

-

Я работаю над процессом сохранения байтов в FIFO с глубиной N. Это конструкция SPI slave. Сигналы MOSI собираются в байт, а байты отправляються в FIFO. Если в FIFO сохранено M байтов, будет сгенерирован триггер. PS: процесс fifo_store_buff - это только часть дизайна. signal trigger_signal: std_logic; --> сигнал, показывающий, достигнуто ли значение "byte_counter" 2200 (1) или нет type fifo_buffer is array(0 to fifo_depth - 1) of std_logic_vector(7 downto 0); signal fifo_sgn : fifo_buffer; constant max_value_counter: integer := 2200; Процесс: fifo_store_buff: process(clk, rst) variable byte_counter : integer range 0 to max_value_counter-1; begin if rst = '1' then trigger_signal <= '0'; elsif (rising_edge(clk)) then for i in 0 to fifo_depth - 1 loop fifo_sgn(i) <= byte_formed_in_process_A; byte_counter:= byte_counter +1; end loop; -- Если пороговое значение (max_value_counter) достигнуто или обнаружен нарастающий фронт сигнала «spi_cs_bb», будет сгенерирован сигнал запуска (trigger_signal). if (byte_counter = max_value_counter-1) or (spi_cs_bb = '1') then trigger_signal <= '1'; --> достигнуто максимальное значение (2200) байтов end if; end if; end process fifo_store_buff; Почему byte_counter показывает 0? он не считает количество байтов.

-

могу я задать еще один вопрос? В чем разница между SPI stream и memory mapped SPI? Они выполняют аналогичную задачу: отправляют данные в ЦП, верно?

-

какая тогда разница? между AXI_Datamover и AXI DMA ? или AXI CDMA (нужно AXI_BRAM_controller и Block_memory_generator)?

-

автомате управления это axi stream fifo, верно? как создать свои автомате управления? редактировать блок axi stream fifo ( VHDL code) , прописывать там свой код ? PS извините, я новичок! опыт 6 месяцев

-

Здравствуйте, Rob ! спасибо, что нашли время ответить. честно говоря, я не понял вашего третьего ответа. Это должен быть блок axi dma?

-

Нужна помощь по SPI, DMA, Vivado

Nano2021 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! Я работаю над реализацией высокоскоростной передачи SPI и ищу лучший вариант для блока DMA. Схематическое изображение моей конструкции:прикрепил На сайте Xilinx я нашел следующиe блоки, который могу использовать: DMA Central Direct Memory Access DataMover 1. В чем разница между DMA и CDMA? Судя по описаниям и блок-схемам, это ... как будто потоковым устройством будет устройство, которое производит или потребляет поток байтов. Устройство с отображением памяти подключается к шине памяти. Таким образом, периферийному устройству, которое хранит входящие данные в регистре с отображением в память, потребуется CDMA, а периферийному устройству, где данные поступают непосредственно из буфера FIFO, потребуется DMA. 2. AXI Data Mover. Если я подключу его с блоком AXI FIFO Stream (параметры передачи команд), я получу блок DMA, как я понял. Этот блок дает мне больше свободы в реализации? 3. Какой вариант лучше всего для передачи данных из высокоскоростного SPI через DMA в память? Я бы хотел достичь 50-100 Мбит / с Заранее спасибо за вашу помощь