Поиск

Показаны результаты для тегов 'vivado'.

-

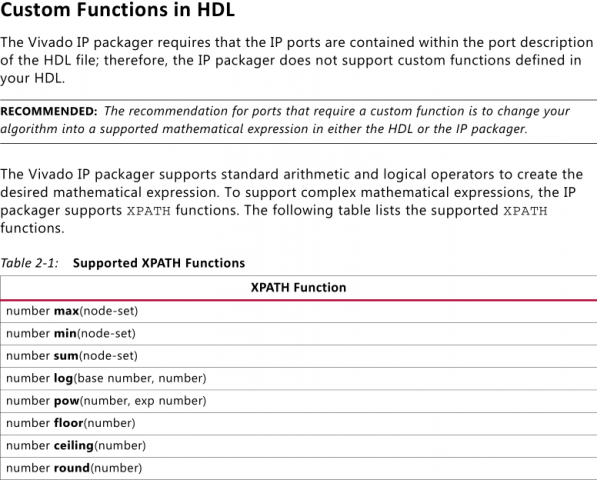

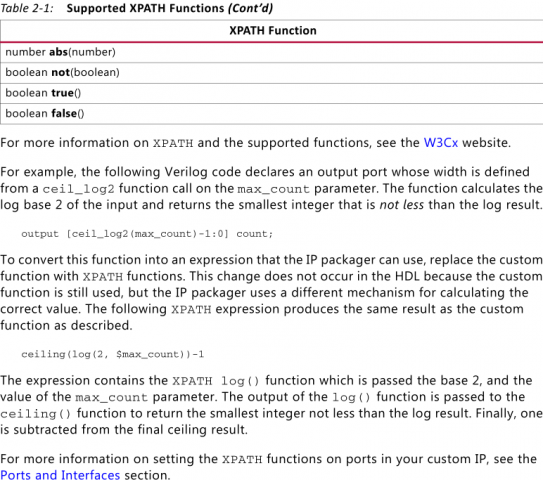

Здравствуйте. Нужно создать в Vivado IP Core, чтобы интегрировать его в Block Design и подключать к Zynq. Был неприятно удивлён тем, что не поддерживаются пользовательские функции (к примеру log2 для задания параметра ширины шины). На форуме Xilinx нашёл пару похожих тем (например, ), только вот решения так и не увидел. В основном описываются проблемы "парсера" IP Packager. Но вроде как в том же ug1118 Creating and Packaging Custom IP говорится о поддержке более сложных математических выражений при помощи XPATH функций: Вот только как и где использовать эти функции XPATH? Как ни пытался ничего не получилось. Даже в описываемом примере, как можно в Verilog коде "output [ceil_log2(max_count)-1:0] count;" заменить пользовательскую функцию ceil_log2 на некую XPATH функцию ceiling(log(2, $max_count)), у которой параметр $max_count описывается как в языке Tcl. Как понять фразы: Может знает кто, как собственно можно использовать эти самые XPATH функции? Или вообще, как кто боролся с кастомизацией параметров для ядер в IP Packager?

-

Вакансия FPGA/SoC Engineer

dmi_iii опубликовал тема в Предлагаю работу

Крупная радиоэлектронная компания ищет разработчика устройств на базе ПЛИС и СнК. Форма занятости: 5-дневная рабочая неделя Локация: Санкт-Петербург, м. Политехническая Требования к кандидату: • Высшее техническое образование по профилю радиофизика/радиотехника/микропроцессорная техника; • Опыт работы в данном направлении от 3 лет; • Наличие завершенных проектов; • Владение английским языком; Ключевые обязанности: • Оценка вычислительной сложности и необходимых ресурсов FPGA/SoC для разрабатываемых алгоритмов; • Перенос алгоритмов цифровой обработки сигнала (децимация, фильтрация, модуляция, демодуляция, преобразование Фурье, корреляционный анализ) с CPU на FPGA и SoC серии UltraScale и выше; • Документирование алгоритмов; • Работа с электрической схемой; • Взаимодействие с разработчиками аппаратной части; Требуемые навыки: • Разработка прошивок для FPGA, SoC фирмы Xilinx; • Моделирование RTL-модулей; • Владение средами Vivado / Vitis; • VHDL/Verilog, TCL Преимуществом будет: • Владение С/C++ • Опыт программирование CUDA; • Владение системами контроля версий; -

Захотелось поднять JESD на двух КИТах ZCU102 (Zynq Ultrascale+) и АЦП AD9695 1300EBZ Eval соединив их по FMC. С проектом никаких сложностей не возникло, ядра все быстро настроил, принялся работать, но микруха AD9695 молчит по SPI и никаких признаков жизни не подаёт. Стандарты протокола, сигналов и распиновку перепроверил много раз, проблем не увидел. На мезонине есть чудесная возможность отладки SPI через контрольные точки Осциллом, ей и воспользовался. Рис.1 - Часть схемы AD9695 Eval Ткнулся в контрольные точки и увидел странную картину. Сигналы "SDI_from_FPGA" и "SCLK_FROM FPGA" накладываются друг на друга и мешают корректно друг другу работать. Когда на шине SDI есть данные (уровень "1"), Клок на SCLK задирается и портится... Рис.2,3 - Осциллограммы на тестовых пинах (Сверху SCLK, снизу SDI); При этом сам клок фонит на данные превращая их в кашу. Рассмотрел более подробно схему и понял, что эти два пина являются ДИФФ парой на разъёме FMC (LA01_P_CC/LA01_N_CC) Рис.4 - Часть схемы AD9695 Eval (FMC) Думал в начале может проблема в настройках VIVADO и как то случайно поставил стандарт не тот на эти выводы, но нет. Стандарт явно обозначен "LVCMOS18" у всех пинов SPI. Залез на всякий случай в схематик в имплементации, там всё верно стоит на выходе "OBUF". О Дифференциальном выходе и речи нет... Кто знает, почему соседние сигналы могут портить друг друга? и что можно с этим сделать? Рис.5 - Мои настройки для пинов SPI в VIVADO Рис.6 - Схематик из VIVADO; PS: На всякий случай ещё уточню, что проблема точно не в мезонине или его разводке. Мезонин снимал и смотрел щупами прямо на FMC разъёме со стороны ZCU102. Картинка та-же. Такими сигналы идут из ПЛИС.

-

И снова кастомизация IPcore в Vivado

OparinVD опубликовал тема в Среды разработки - обсуждаем САПРы

Приветствую всех! Давно я кручусь вокруг этой темы, много раз возвращался к похожим веткам на форуме, перечитал мануалы от Xilinx, но не дается оно мне. Есть ощущение, что не хватает легкого волшебного пендаля, чтоб всё встало на свои места, и чтоб над головой лампочка, как в мультике, загорелась. Что я хочу получить: Хочу навести красоту, наподобие стандартных корок - чтоб жмешь разные галочки в GUI, и в зависимости от этого подключались разные HDL-ные или IPcore-ные внутренности, и менялось, например количество внешних портов. Что умею на данные момент: 1) Могу накидать форму для GUI в IP packager'е - тут всё интуитивно понятно. Могу играть с Enablement dependency, включая/выключая порт. Вижу сгенерированный tcl-скрипт для GUI с функциями proc update_PARAM_VALUE... и proc validate_PARAM_VALUE... 2) Независимо от этого могу на основе Export Block Design создать свой скриптик, который будет с учетом внешних условностей делать create_cell'ы и соединять их connect_net'ами. Не могу понять, как мне скрестить первый и второй пункты. Сейчас у меня GUI - просто пустышка, а скрипт могу запустить только вручную, например, для восстановления проекта из git. По всей вероятности всё должно работать автоматически: кинул Ipcore на канвас, изменил параметры - запустился скрипт, который подтянул нужные исходники, создал топ-левел и т.д. Запустил валидацию BD, пошла пропаганда параметров - опять запустился тот же скрипт. Как этого добиться?- 27 ответов

-

- customization parameters

- tcl

-

(и ещё 2 )

C тегом:

-

Ищем ведущего специалиста разработки проектов на ПЛИС. Проекты средней и высокой сложности, по обработке сигналов и с поддержкой скоростных интерфейсов. Работа в команде разработчиков. Заработная плата от 90 000 до 180 000 на руки, определяется по результату собеседования с руководителем. Адрес офиса: г. Санкт-Петербург, Пискарёвский проспект, д. 150, к. 5, «Ручьи». Действует развозка от ст.м. Гражданский пр., Площадь Мужества, Комендантский пр., Пр. Просвещения, Ул. Дыбенко. График работы: 5/2, с 9:00 до 18:00 или с 10:00 до 19:00. Формат: полностью офисный (не дистанционка и не гибрид). Официальное оформление, ДМС после испытательного срока. Требования к кандидатам: ▶ высшее техническое образование; ▶ уверенные знания Verilog; ▶ опыт работы с DSP; ▶ инициативность; ▶ умение работать в команде; ▶ навыки организации работ. Навыки работы с ПО: ▶ Xilinx Vivado; ▶ желательно уметь самостоятельно создавать модели по обработке сигналов на С++, Python, Matlab или других языках. О компании: Специальный технологический центр (сайт компании, хабр). Занимаемся разработкой и производством: ⠀ ▶ систем в сфере информационной безопасности ▶ систем сбора и анализа больших данных с применением методов машинного обучения и искусственного интеллекта ▶ телекоммуникационных систем спутниковой связи ▶ беспилотных летательных аппаратов и квадрокоптеров семейства «Орлан», спутниковых комплексов и систем управления ими ▶ телекоммуникационного оборудования, включая комплексы радиомониторинга, различной военной техники наземного, воздушного и морского базирования Контакты для связи: +7 911 700-09-66 (звонки, Telegram) 8 (812) 244-33-13, доб. 2664 [email protected]

-

Всем привет. Много работал ранее с проектами в среде QUARTUS, очень часто приходилось отлаживать проекты в железе при помощи встроенного логического анализатора Signal Tap II. Очень удобный инструмент, ни один раз помогал мне найти и выявить ошибки, пропущенные на стадии моделирования и некоторые моменты, которые моделирование в принципе не способно обнаружить. В данный момент создаю проект в Xilinx Vivado, где на ПЛИС принимаю по JESD отчёты из АЦП, провожу некоторую обработку данных и кладу в память. Столкнулся с ситуацией, что на модели всё идеально, никаких проблем нет, но в железе не работает должным образом моя внутренняя логика (при этом приём сигнала с АЦП по JESD в норме). Стал разбираться, с помощью ядер ILA выводить интересующие меня сигналы JESD, флаги и статусы для анализа. Первая проблема, с которой я столкнулся, не могу завести ядра на частоте, которой изначально нет в ПЛИС (в момент подачи питания). Частота появляется с программируемого генератора позже и САПР Vivado говорит мне, что не может запустить ядро ILA и показать результаты... Пришлось перебрасывать все нужные мне сигналы через три регистра на стабильный клок (от DDR у меня есть 300МГц, которые всегда поступают в ПЛИС). ILA запускается, но тут начинается танец с бубном. У меня либо совсем умрёт JESD, что перестают корректно приниматься данные, либо работает но данные бьются. Причём бьются не те данные, которые я вывел на ILA, а реальные отчёты АЦП, поступающие в память. Лечится эта штука путём полного сброса проекта (команда "reset_project" TCL) и 1-2 перекомпиляции, не меняя исходников или настроек. В итоге этот процесс очень сильно стопорит процесс отладки. После каждых изменений в проекте, приходится танцевать с бубном и надеяться, что после 2-3 перекомпиляций проект получится рабочий, JESD запустится и ILA ему мешать не будет. Прошу помощи у более опытных пользователей. Как вы работаете с ILA? Как тестируете работоспособность проекта в железе на xilinx?

-

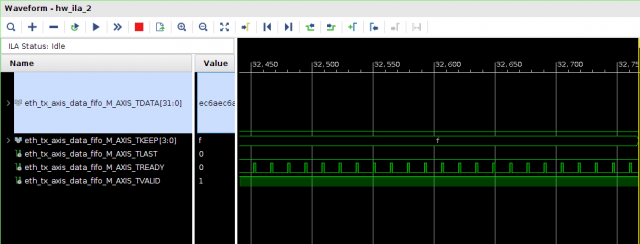

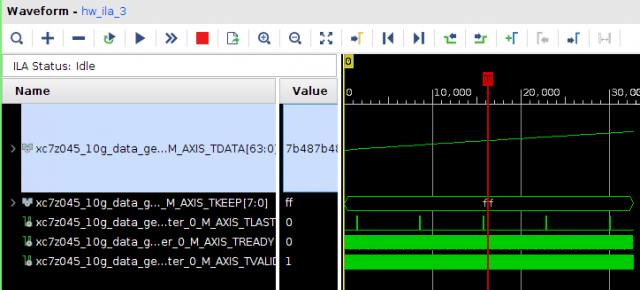

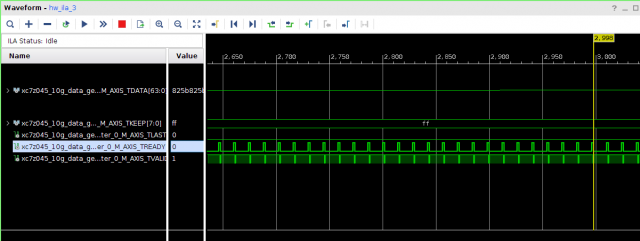

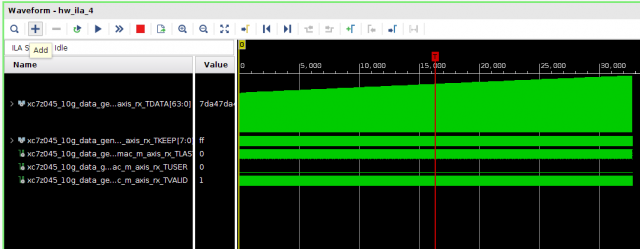

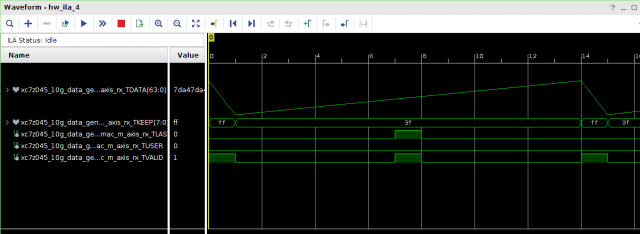

поток данных через 10GE

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

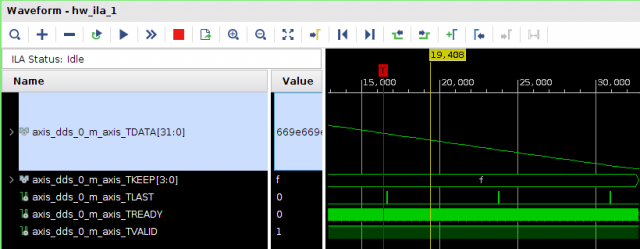

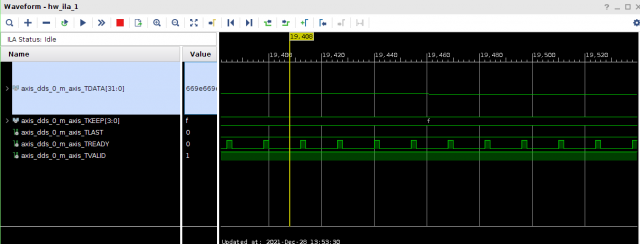

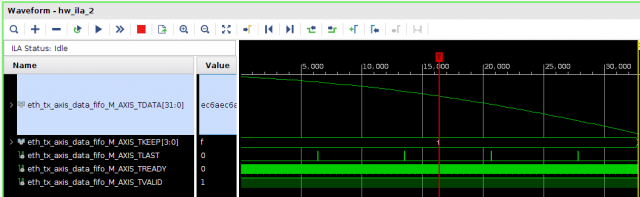

Всем привет! Друзья подскажите, почему принемаемые данные прореженны нулями. dds -> axis_fifo -> width_converter (32 -> 64) -> 10ge (mac + pcs/pma) -> axis_checker -> ila Тактовый генератор настроен и работает на 156.25МГц. ЕСли чегото не хватает говорите, дозалью) Заранее спасибо! dds -> fifo dds -> fifo зазумлен fifo -> width converter fifo -> width converter зазумлен width converter -> mac 10G tx width converter -> mac 10G зазумлен rx -> axis checker rx -> axis checker зазумлен 1 rx -> axis checker зазумлен 2 bd.pdf -

Компания Xilinx сообщила о выходе нового релиза программного обеспечения Vivado ML и Vitis версии 2021.2. Подробнее

-

вебинар Язык TCL в проектировании на Xilinx. Вебинар

МакроГрупп опубликовал тема в Объявления пользователей

-

вебинар Знакомство с экосистемой Xilinx. Вебинар

МакроГрупп опубликовал тема в Объявления пользователей

На вебинаре Вы узнаете, какие готовые устройства и отладочные платы существуют, какие фреймворки и библиотеки можно использовать для ускорения приложений и где найти всю необходимую информацию. Подробнее -

Собираем MicroBlaze (на русском)

KeisN13 опубликовал тема в Обучающие видео-материалы и обмен опытом

Сборка софт процессора MicroBlaze от Xilinx на русском в пошаговом режиме с огромным количеством картинок в нескольких частях: Разработка процессорной системы на базе софт-процессора MicroBlaze в среде Xilinx Vivado IDE/HLx. Часть 1. Разработка процессорной системы на базе софт-процессора MicroBlaze в среде Xilinx Vivado IDE/HLx. Часть 2. Программирование загрузочной FLASH для запуска MicroBlaze Подключение подсистемы памяти к MicroBlaze (MIG 7 Series)- 16 ответов

-

- microblaze

- arty

-

(и ещё 2 )

C тегом:

-

Xilinx ADAPT EMEA. Онлайн конференция

МакроГрупп опубликовал тема в Объявления пользователей

Компания Xilinx c 9 ноября по 16 декабря 2021 года проведёт онлайн конференцию для регионов Европы, Ближнего Востока и Африки по адаптивным вычислительным технологиям Xilinx. Подробнее -

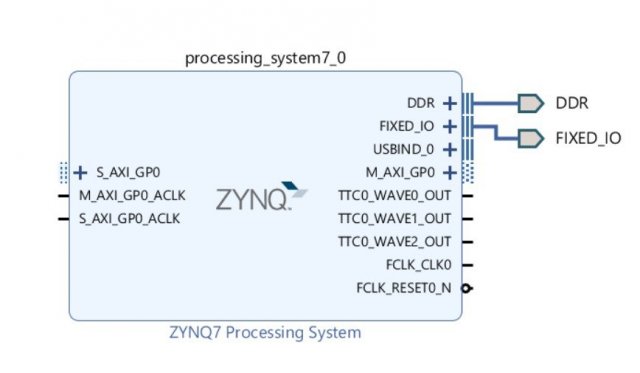

Я написал функцию "memcpy" для копирования блока данных с исходного адреса на адрес назначения. Хочу протестировать на плате (Zynq). Я новичок в MCU и изучаю эту тему самостоятельно, извините, если мой вопрос для вас глупый. Что я сделал: Я создал проект в vivado, начал block design с Zynq, изменил конфигурацию PS-PL (добавил GP Master и Slave AXI Interface) [Смотри приложение]. Я читал, что Zynq может быть Master, но Slave/ периферийнoe устройство я должен спроектировать как настраиваемое IP-ядро. Я уже нашел, как создать собственный AXI IP (slave или master). Vivado создает шаблон настраиваемого IP-ядра (slave). (1) Могу ли я использовать этот шаблон без каких-либо изменений? (2) Следует ли мне добавить дополнительную информацию (сигналы, которые я использую в функции memcpy: адреса и количество битов)? Я пропустил дизайн custom master . (3) Я сделал правильно или мастер должен быть частью настраиваемого IP ядра?

-

Приобрел на Али пару плат, Нашел пример собрал, попробовал зашить - не получается. Обновил драйвера - по прежнему не работает. Нашел рекомендацию попробовать ISE. У меня 14.2, собрал проект с одним инвертором. Похоже, что до ПЛИС достучатся удается, но инициализация JTAG Chain не завершается Окошко "висит" Вернулся в Vivado 2018, по прежнему ошибка. Делаю вывод что с железом все в норме, а с драйверами проблема. Но какая не могу найти.

-

Vivado 2020.2 глюк при синтезе памяти

RobFPGA опубликовал тема в Среды разработки - обсуждаем САПРы

Приветствую! Какой великолепный глюк я поймал в Vivado 2020.2. Есть некий модуль где память используется несколькими каналами, соответственно удобно адрес такой памяти определить как структуру module tst_syn_ram #(parameter CH_WH = 4, IDX_WH = 8, DIN_WH = 8 ) ( input wire clk , input wire [ CH_WH-1:0] wr_ch , input wire [IDX_WH-1:0] wr_idx, input wire [DIN_WH-1:0] wr_din, input wire wr_en , // input wire [ CH_WH-1:0] rd_ch , input wire [IDX_WH-1:0] rd_idx, output logic [DIN_WH-1:0] rd_dou ); typedef struct packed { logic [ CH_WH-1:0] ch ; logic [IDX_WH-1:0] idx; } st_ADDR_t; loclparam ADDR_WH = $bits(st_ADDR_t); (* ram_style = "auto" *) // distributed, block logic [DIN_WH-1:0] mem [0:2**ADDR_WH-1]; st_ADDR_t wr_addr; st_ADDR_t rd_addr; // тут должно быть много логики формурующие адрес и данные // но для примера просто присвоенны входные порты assign wr_addr.ch = wr_ch; assign wr_addr.idx = wr_idx; assign rd_addr.ch = rd_ch; assign rd_addr.idx = rd_idx; // простая память always_ff @(posedge clk) begin if (wr_en) begin mem[wr_addr] <= wr_din; end rd_dou <= mem[rd_addr]; end endmodule : tst_syn_ram При синтезе такого описания Vivado считает что ширина адреса используемого для адресации памяти равна ширине первого поля в структуре и соответственно можно молча оптимизировать размер синтезируемой памяти. Сделать так сказать юзеру "приятно" Ну а второе поле не выбрасывать же. Соответственно Vv сворачивает его по И вместе с wr_en, мол пишем в память только если wr_addr.idx!=0. И это без все варнингов и ошибок при синтезе . "23 Infos, 0 Warnings, 0 Critical Warnings and 0 Errors encountered." Понятно что синтезатор сходит с ума когда в качестве адреса в памяти видит пакованную структуру. А у меня такого кода много Попробовал бороться с этим - можно обернуть адрес так: ... mem[ADDR_WH'(rd_addr)]. Но блин писанины много. А можно просто взять в скобки - ... mem[{rd_addr}]. Причем из экспериментов получается что на глюк в примере выше влияет описание адреса только при чтении! То есть - // глюк все еще есть always_ff @(posedge clk) begin if (wr_en) begin mem[{wr_addr}] <= wr_din; end rd_dou <= mem[rd_addr]; end // глюка уже нет always_ff @(posedge clk) begin if (wr_en) begin mem[wr_addr] <= wr_din; end rd_dou <= mem[{rd_addr}]; end Но для гарантии буду оборачивать скобками везде. Скобок много не бывает .... Удачи! Rob. -

Нужна помощь по SPI, DMA, Vivado

Nano2021 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! Я работаю над реализацией высокоскоростной передачи SPI и ищу лучший вариант для блока DMA. Схематическое изображение моей конструкции:прикрепил На сайте Xilinx я нашел следующиe блоки, который могу использовать: DMA Central Direct Memory Access DataMover 1. В чем разница между DMA и CDMA? Судя по описаниям и блок-схемам, это ... как будто потоковым устройством будет устройство, которое производит или потребляет поток байтов. Устройство с отображением памяти подключается к шине памяти. Таким образом, периферийному устройству, которое хранит входящие данные в регистре с отображением в память, потребуется CDMA, а периферийному устройству, где данные поступают непосредственно из буфера FIFO, потребуется DMA. 2. AXI Data Mover. Если я подключу его с блоком AXI FIFO Stream (параметры передачи команд), я получу блок DMA, как я понял. Этот блок дает мне больше свободы в реализации? 3. Какой вариант лучше всего для передачи данных из высокоскоростного SPI через DMA в память? Я бы хотел достичь 50-100 Мбит / с Заранее спасибо за вашу помощь -

vitis Компания Xilinx представила релиз Vitis 2021.1

МакроГрупп опубликовал тема в Объявления пользователей

-

- xilinx

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

На сайте компании Xilinx размещена для скачивания версия среды разработки для ПЛИС и СнК Vivado под номером 2021.1. Подробнее

-

- vhdl

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

В данном вебинаре вы познакомитесь с основными особенностями нового поколения адаптивных систем Versal, с тем, какие среди них существуют вариации и в каких сферах их применение принесёт максимальную пользу. Подробнее

-

- плис

- fpga xilinx

- (и ещё 7 )

-

Не прошивается ПЛИС Xilinx

Skryppy опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. У меня есть несколько приборов с Artix. Все приборы прошиты и работают. Когда понадобилось обновить прошивку, то выявил одну проблему - в одном приборе не обновляется прошивка. В Vivado прошивка начинает заливаться, но проходит буквально 2 секунды и окно прошивки закрывается, при этом сообщений об ошибке нет, но в ПЛИС осталась старая прошивка. Лог когда все ОК: Лог когда нет результата: Если прошивать флешку, то в этом приборе ошибка: [Labtools 27-3347] Flash Programming Unsuccessful: Failure to set flash parameters. Самое интересное, что если запустить Impact, то он прошивает и ПЛИС и флешку нормально в этом приборе. Может кто сталкивался с такой проблемой? P.S. Разъёмы переподключал, компьютер перезагружал, программатор менял - не помогло. -

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Приглашаем на информационно практический вебинар «Решения Xilinx для интеллектуального управления электроприводом». На вебинаре будут рассмотрены решения Xilinx на базе систем на кристалле (SoC) для экосистем, в которые входят различные электроприводы. Эти решения обеспечивают не только оптимальное управление одним или несколькими моторами/электроприводами, но также осуществляют управление через Интернет, сбор и обработку аналитики в облаке, обнаружение неисправностей и даже предсказание времени их наступления. Зарегистрироваться

-

Vivado. Disable Constraint From IP Core.

dxp опубликовал тема в Среды разработки - обсуждаем САПРы

Всем привет! Ситуация следующая. Есть IP ядро PCIe (для US+), собираю проект (их референс или свой, не суть важно), получаю на P&R несколько десятков предупреждений вида (иерархию пути я побил на отдельные строки, чтобы было проще воспринимать эту "кашу"): [Timing 38-3] User defined clock exists on pin pcie4_uscale_plus_0_i/ inst/gt_top_i/ diablo_gt.diablo_gt_phy_wrapper/ gt_wizard.gtwizard_top_i/ pcie4_uscale_plus_0_gt_i/ inst/ gen_gtwizard_gtye4_top.pcie4_uscale_plus_0_gt_gtwizard_gtye4_inst/ gen_gtwizard_gtye4.gen_channel_container[0].gen_enabled_channel.gtye4_channel_wrapper_inst/ channel_inst/gtye4_channel_gen.gen_gtye4_channel_inst[0].GTYE4_CHANNEL_PRIM_INST/TXOUTCLK [See "...kcu116/pcie4_uscale_plus_0_ex/pcie4_uscale_plus_0_ex.srcs/sources_1/ip/pcie4_uscale_plus_0/source/ip_pcie4_uscale_plus_x0y0.xdc":119] and will prevent any subsequent automatic derivation of generated clocks on that pin. If the user defined clock specifies '-add', any existing auto-derived clocks on that pin are retained. ["...kcu116/pcie4_uscale_plus_0_ex/imports/xilinx_pcie4_uscale_plus_x0y0.xdc":135] Все они ссылаются на один и тот же констрейн из указанного файла (строка 119): create_clock -period 2.0 [get_pins -filter {REF_PIN_NAME=~TXOUTCLK} -of_objects [get_cells -hierarchical -filter { PRIMITIVE_TYPE =~ ADVANCED.GT.* }]] По смыслу, как я понял, тулу не нравится то, что руками описан клок, который тул и так сам создаёт. Я закомментил этот констрейн, и предупреждения ушли. Собственно вопрос: поскольку файл этот генерируется в составе IP ядра, то править его в проекте идея так себе - при сборке проекта "с нуля" или пересборке все правки в этом файле потеряются. Поэтому надо бы как-то снаружи вырубать констрейн. Как это сделать? Путь в лоб: запускать скрипт после сборки IP ядра, который тупо закомментит эту строку. Но это как-то громоздко и некрасиво. Имеется ли альтернативное решение?- 18 ответов

-

- vivado

- constraint

-

(и ещё 1 )

C тегом:

-

Временные ограничения (timing constraints) используются для задания временных характеристик дизайна. Временные ограничения влияют на все внутренние временные взаимосвязи, задержки в комбинаторной логике (LUT) и между триггерами, регистрами или ОЗУ. Временные ограничения могут быть глобальными или зависящими от пути. Для достижения требуемых временных характеристик проекта, разработчику необходимо задать набор ограничений для этапов синтеза и физической реализации, которые представляют собой требования, предъявляемые к заданным путям или цепям. Ими могут быть период, частота, перекос на шинах, максимальная задержка между конечными точками или максимальная чистая задержка. После синтеза или реализации достигнутые характеристики анализируются с помощью инструментов статического временного анализа Vivado. Статический анализ тайминга – это метод определения соответствия схемы временным ограничениям без необходимости моделирования, поэтому он намного быстрее, чем симуляция с учетом временных задержек. Инструменты Vivado STA проверяют настройки, временные характеристики (setup and hold time), ограничения синхронизации, максимальную частоту и многие другие правила проектирования. Статический анализ тайминга в качестве исходных данных принимает синтезированный список соединений либо физический список соединений проекта. На основе этих списков, алгоритмы Xilinx рассчитывают временные задержки и их соответствие задаваемым разработчиком требованиям. Запись вебинара:

-

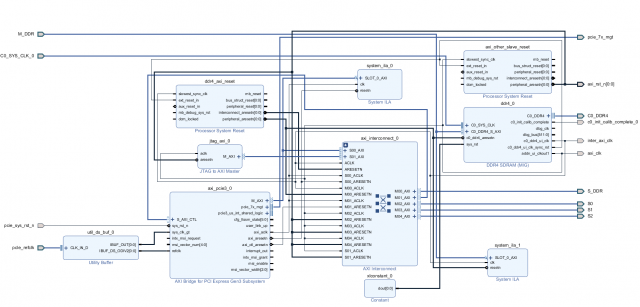

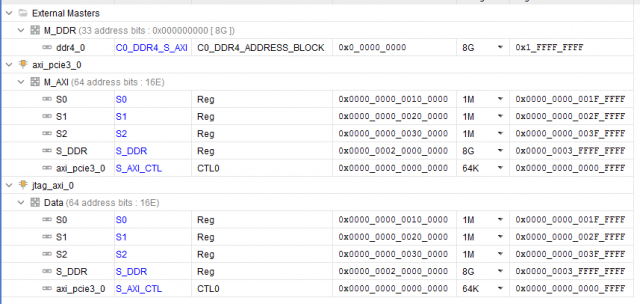

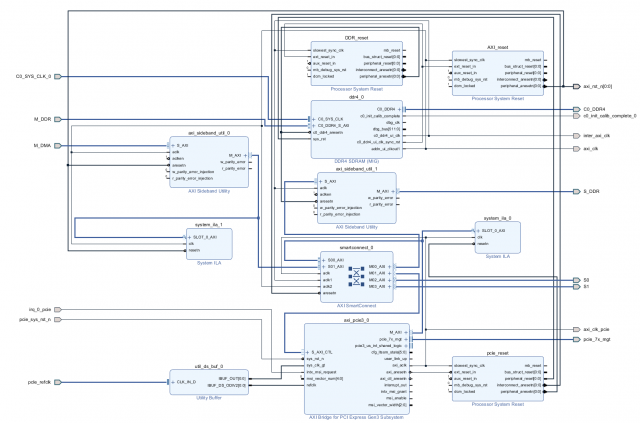

Добрый день. Долго работал с Intel (Altera) бед не знал в среде Quartus и вот пришлось перейти (к глубокому сожалению) на работу с Xilinx... Сразу был разочарован, многое из того, что доведено до автоматизма у Intel тут нужно делать самому, вникая в низкоуровневые тонкости. Очень большие ограничения на использования ip-ядер (плюс скудный набор изменяемых параметров) и плохие тайминги заводят меня в тупик. Так вот, какова суть проблемы. Работаю с Kintex Ultrascale. Понадобилось собрать систему из ядра PCIe -> interconnect ->DDR4. Прочитал кучу мануалов (PG194 v3.0, PG059 и тд.., Ответы с форумов, Видео пример настройки, Вивадовские примеры). В общем собрал систему похожую на систему из примеров. Рис. 1 Тут добавил ещё Jtag консоль для удобства отладки (в дальнейшем необходимо заменить её на свой блок ДМА), вывел интерфейсы для своих слейвов наружу. ДДР тоже вывел наружу (как S_DDR) на верхнем уровне закольцевал и вернул обратно (как M_DDR, опять же дикость связанная с XILINX пришлось решать одну из его проблем таким образом). Повесил ещё пару ИЛА для отладки и отображения шины АXI. Назначил адресные пространства. Рис. 2 Вроде всё задышало. Но с большими слеками на интерконнекте... То PCIe сама развестись не может, то на ядре ДДР какие то проблемы по таймингам. В общем всё плохо, но как то работает. По PCIe есть доступ и к DDR и к регистрам в слейвах, вроде всё корректно. Начинаю работать через Jtag консоль (в дальнейшем её нужно заменить своим блоком ДМА) и всё, ДДР не читается не пишется, комп умирает, интерконнект виснет. Проблема только при обращении к ДДР, при работе с моими слейвами регистровыми проблем нет, данные корректно пишутся и читаются. Залез по ИЛА и увидел что от ДДР не доходит сигнал BVALID и BID через интерконнект. Собственно из ДДР он вышел, но через интерконнект до второго мастера он не приходит, а для первого без проблем, всегда всё хорошо. Окей, меняю местами Jtag и PCIe та же шляпа. Jtag работает корректно, до PCIe не доходит BVALID и BID. Получается что второму мастеру по счёту просто не даётся доступ к ДДР. Листал форумы, читал советы, нашёл. Говорят что на Ultrascale и Ultrascale+ стандартный интерконнект не работает корректно, нужно ставить некий "SMARTCONNECT"... Ну окей.. читаю документацию, разбираюсь, вставляю смартконнект.. А у него оказывается выкидывает все ID(r/w/b) на шине AXI. Чтобы ID не выкидывались, ставьте "axi sideband" (говорит XILINX) до и после интерконнекта на каждой шине.. окей, поставил. Спустя все эти манипуляции я получил рабочую схему, которая может работать с двумя мастерами и без проблем читать и писать в ДДР. Рис. 3 Но эта штука разводится очень плохо. Сложность в том, что у AXI PCIe максимальная частота 250МГц, у ДДР в моём режиме (1200МГц частота памяти) AXI DDR 300МГц. Слейвы свои на такой частоте я не потяну, иначе вообще всё по таймингам умрёт... пришлось ставить в 2 раза меньше. Поставил 150МГц на слейвах. В итоге интерконнект городит очень сложную структуру из ядер клоковых конвертеров, конвертеров данных, протоколов и тд.. А потом при имплементации на эти же ядра и ругается Вивадо. Долго бьюсь над этой проблемой, не могу нормально побороть слеки. Пришлось понизить частоту ДДР до 1000МГц, соответственно AXI DDR стала 250Мгц, а частота моих слейвов 125 МГц. Слеки явно улучшились, работать можно, но проблема совсем не ушла. Как мне правильно настроить систему, чтобы не было конфликтов между ядер XILINX и всё нормально разводилось при требуемых параметрах?

- 17 ответов

-

- xilinx

- ultrascale

-

(и ещё 4 )

C тегом:

.thumb.jpg.81a4945a234826d4eb04fb86119e9230.jpg)